UNIVERSIDADE FEDERAL DE SANTA MARIA

CENTRO DE TECNOLOGIA

DEPARTAMENTO DE ELETRÔNICA E COMPUTAÇÃO

Caderno Didático - Disciplina de Sistemas Digitais “A”

Prof°. Dr. José Renes Pinheiro

Colaboradores: José Eduardo Baggio

Everton Correia de Camargo

Robinson Figueredo de Camargo

Ultima Atualização: junho/2000

ELC 419 - Sistemas Digitais A

2

SUMÁRIO

1. Introdução ................................................................................................................ 03

2.Flip-Flops ou BI-ESTÁVEIS ................................................................................... 04

2.1. Latches ................................................................................................................ 04

2.1.1. Latch SR com Portas NOR .............................................................................. 05

2.1.2. Latch SR com Portas NAND............................................................................ 05

2.1.3. Latch SR com ENABLE ................................................................................. 06

2.1.4. Latch D............................................................................................................. 07

2.2. Flip-Flop ............................................................................................................... 07

2.2.1 Flip flop SR Mestre Escravo .............................................................................. 08

2.2.2. Flip flop JK Mestre Escravo ............................................................................. 09

2.2.3. Flip-Flop Edge-Triggered...................................................................................10

2.2.4. Flip-Flop JK Sensível a Borda de Subida ..........................................................11

2.2.5. Flip-Flop T .........................................................................................................11

2.3. Entradas Assíncronas ............................................................................................12

2.4. Glossário de Flip-Flops e Registradores ...............................................................12

2.5.Aplicações e Exercícios ........................................................................................ 13

2.6. Glossário Considerações práticas para Projetos Digitais ..................................... 15

2.7. Registradores ........................................................................................................ 16

2.7.1. Registradores de Deslocamentos Síncrono ................................................... 16

3. PROJETO DE CIRCUITOS SEQÜÊNCIAS ..........................................................18

3.1. Características e Estrutura de Máquinas Seqüências Síncronas ............................18

3.2. Tipos de Máquinas Seqüências ............................................................................19

3.2.1. Procedimento para Análise de uma MSS ...........................................................20

3.3. Procedimento para Projeto para Máquinas de Estado .......................................... 27

3.4. Tabela de Estado .................................................................................................. 27

3.5. Exercícios de Diagrama de Estados ..................................................................... 29

3.6. Seleção das Variáveis de Estado .......................................................................... 34

3.7. Tabela de Transição ............................................................................................. 34

3.8. Tabela de Excitação ............................................................................................. 35

3.8. Equações de Excitação e de Saída ....................................................................... 36

3.10. Procedimento de Projeto através de Equações de Estado .................................. 37

3.11. Simplificações na Máquina de Estado ............................................................... 42

4. MEMÓRIAS ........................................................................................................... 49

5. CONVEROSRES A/D e D/A ................................................................................. 59

5.1. Conversor Analógico/Digital .......................................................................... 59

5.2. Conversor Digital/Analógico ...........................................................................67

7. BIBLIOGRAFIA .................... ............................................................................ 72

7. BIBLIOGRAFIA 69

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

3

CIRCUITOS SEQÜÊNCIAIS

1.

INTRODUÇÃO

Os circuitos digitais até agora conhecidos pela disciplina de Circuitos Digitais

eram formados por lógica combinacional, onde as saídas em qualquer instante de

tempo são inteiramente dependentes das entradas presentes neste tempo.

Embora todo sistema digital seja constituído por circuitos combinacionais,

muitos sistemas encontrados na prática também incluem elementos de memória, estes

requerem que o sistema seja descrito em termos de lógica seqüêncial.

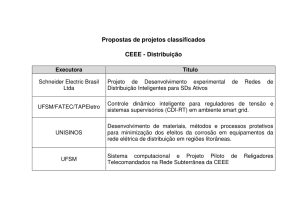

Um diagrama de blocos de um circuito seqüêncial é mostrado na figura 1

abaixo. Este consiste de portas de lógica combinacional que recebem sinais binários

de entradas externas e de saídas de elementos de memória e geram sinais de saídas

externas e de entradas de elementos de memória.

Figura 1 - Diagrama de blocos de um circuito seqüêncial

Um elemento de memória é um dispositivo capaz de armazenar um bit de

informação. A informação binária armazenada em elementos de memória pode ser

mudada pelas saídas do circuito combinacional. As saídas dos elementos de memória,

são ligadas nas entradas dos gatilhos no circuito combinacional.

O circuito combinacional, por si mesmo, executa um processo de operação de

informação específica, parte da qual é usada para determinar o valor binário para ser

armazenado em elementos de memória. As saídas dos elementos de memória são

aplicados no circuito combinacional e fixam, em parte, as saídas do circuito. O

processo claramente demostra que as saídas externas de um circuito são uma função

não somente das entradas externas, mas também do estado presente de elementos de

memória.

O próximo estado dos elementos de memória são uma função das entradas

externas e estados presentes. Assim, um circuito seqüêncial é especificado por uma

seqüência de tempo das entradas, e estados internos.

Os circuitos seqüênciais podem operar síncrona ou assincronamente.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

4

Nos sistemas assíncronos, as saídas dos circuitos lógicos podem mudar de

nível lógico, sempre que o nível de uma ou mais deste também mude. Nesta disciplina

serão focalizados os circuitos seqüênciais síncronos.

2.

FLIP-FLOPS ou BI-ESTÁVEIS

Os elementos de memória são usados em circuitos de seqüência que usam

clock e são chamados de flip-flops, onde estes circuitos são células binárias capazes

de armazenar um bit de informação. Um circuito flip-flop tem duas saídas, uma para o

valor normal e uma para o valor complementar do bit armazenado neste.

Nos sistemas síncronos, os instantes de tempo nos quais qualquer das saídas

pode ser alterada, são determinados por um sinal denominado clock. Este sinal, é via

de regra, um trem de pulsos retangular ou uma onda quadrada.

Estes circuitos também são chamados de bi-estáveis, por possuírem duas

saídas estáveis.

2.1.

LATCHES

São circuitos bi-estáveis capazes de guardar um bit de informação, assim podem ser

chamados de circuitos básicos de memória.

2.1.1. Latch SR com portas NOR

Figura 1 - Latch SR com portas NOR

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

5

Equação de estado

Símbolo

Q( n + 1) = R ⋅ Q(n ) + S

S ⋅ R = 0(est .in det .)

R

Q

S

Q

2.1.2. Latch SR com portas NAND

Figura 2 - Latch SR com portas NAND

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

Equação de estado

6

Símbolo

Q( n + 1) = S ⋅ Q( n) + R

S ⋅ R = 0( est .in det .)

2.1.3. Latch SR com Enable

Figura 3 - Latch SR com Enable

EN

0

1

1

1

1

S

X

0

0

1

1

Tabela característica

R

Q(n+1)

Q(n+1)

X

Q (n)

Q (n)

0

Q (n)

Q(n)

1

0

1

0

1

0

1

-------

Símbolo

2.1.4. Latch D

Figura 5 - Latch D

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

Equação de estado

7

Símbolo

Q( n + 1) = D

Para implementarmos um latch “ D ” com “enable” basta substituir o lacth “ RS ”

comum por um com entrada “enable”.

2.2.

FLIP-FLOPS

Os sinais de saída de uma latch variam instantaneamente com a combinação de

suas entradas durante o pulso alto na entrada, já em flip-flops as saídas variam

somente durante a transição da entrada de controle (clk) esta transição é chamada

disparo ou “trigger”.

Figura 6 - Circuito Digital com uso de Flip-flop

O uso de latches em circuitos seqüênciais pode causar sérios problemas, uma

vez que a entrada enable permaneça em nível alto, a saída é dada pela combinação

instantânea das entradas que são geradas por uma lógica combinacional das saídas da

Latch.

Esta realimentação pode ocasionar oscilações no sinal de saída e como

resultado os sinais de saída do sistema serão indeterminados.

Um bom exemplo é o circuito da figura 7 abaixo:

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

8

Figura 7 - Circuito Digital com realimentação

EN

0

1

1

1

1

Tabela característica

K

J

Q(n+1)

X

X

Q (n)

0

0

Q (n)

0

1

1

1

0

0

1

1

Indefinido

Existem duas maneiras de combinarmos latches para formarmos um flip-flop.

Uma é combinarmos duas latches fazendo com que o estado das saídas só mude no

nível alto ou baixo da entrada de clock. Tais circuitos são chamados flip-flops mestreescravo. Uma outra maneira é produzir um flip-flop que seja disparado somente a

transição do sinal de clock (0 para 1) ou (1 para zero).

2.2.1. Flip-Flop SR Mestre -Escravo

Figura 8 - Flip-Flop RS Mestre-Escravo

Como mostra a figura 8 este flip-flop consiste de duas latches e

Conforme a figura acima a latch da esquerda é chamada “mestre” e

“escravo”.

Quando a entrada de clock é 1 o mestre está habilitado, portanto

entrada produzem variações na variável intermediária Y, o escravo por

desabilitado através do inversor.

Prof. José Renes Pinheiro, Dr.Eng.

um inversor.

a da direita

variações na

sua vez está

[email protected]

ELC 419 - Sistemas Digitais A

9

Quando a entrada clk é zero o processo se inverte e o mestre é que está

desabilitado, mantendo Y e Y fixos, que por sua vez produziram as saídas do escravo

QeQ.

Este tipo de combinação para se produzir um flip-flop é chamado flip-flop

sensível a nível.

2.2.2. Flip-Flop JK Mestre -Escravo

O flip-flop JK é uma modificação realizada no "RS", visto anteriormente para

evitar termos o estado proibido fazendo com que esta combinação das entradas tenha

uma função específica, isto é, o complemento da saída.

Figura 9 - Flip-Flop JK Mestre-Escravo

Q( n + 1) = J ⋅ Q( n) + K ⋅ Q( n)

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

10

2.2.3. Flip-Flop Eddge-triggered

Um flip-flop disparado na borda ignora o pulso de sincronismo, enquanto este

possui um nível constante e dispara somente na transição do sinal de sincronismo. Os

flip-flops disparados na transição positiva (0 para 1) são ditos sensíveis a borda de

subida (positive edge), enquanto que os trigados a transição negativa (1 para 0) são

sensíveis a borda de descida (negative edge).

A figura abaixo mostra o diagrama lógico de um flip-flop tipo D sensível a

borda de subida.

Figura 10 - Diagrama lógico de um flip-flop tipo D sensível a borda de subida.

Como pode-se observar este circuito tem a mesma forma do mestre-escravo

estudado anteriormente, porém a latch mestre é substituída por uma tipo D e um

inversor é adicionado.

Com a latch mestre do tipo D este flip-flop exibe um comportamento de

disparo sensível a borda ao invés de nível (mestre-escravo).

Quando a entrada de clock é igual a zero, a latch mestre é habilitada e transfere

o valor da entrada D, enquanto que a latch escravo esta desabilitada fazendo com que

a saída não mude.

Quando uma transição positiva ocorre, a entrada de clock vai para 1. Isto

desabilita o mestre e habilita a latch escravo para que esta transfira para a saída do

flip-flop o valor do mestre. Assim o valor da saída do flip-flop é o valor da entrada

imediatamente anterior a transição de subida do sinal de clock. Enquanto a entrada de

clock estiver em nível alto a saída permanece inalterada, pois o mestre está

desabilitado e finalmente a transição negativa (1 para 0) , o escravo é desabilitado

mantendo a saída constante.

2.2.4. Flip-Flop JK Sensível a Borda de Subida

Figura 11 - Flip-flop tipo JK sensível a borda de subida.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

11

Equação de Estado

A = J ⋅ Q( n) + K ⋅Q( n)

2.2.5. Flip-Flop T

A T (toggle) flip-flop muda de estado a cada pulso de clock , pode ser

construído a partir de um flip-flop tipo T ou flip-flop JK.

Figura 12 - Flip-flop tipo T .

2.3.

Entradas Assíncronas

Flip-flops freqüentemente possuem entradas especiais para preset ou clear da

saída assincronamente ,isto é , independentemente da entrada de clock.

Também podem ser ativadas em nível alto ou baixo dependendo do dispositivo

utilizado, comercialmente existem uma grande variedade de flip-flops com entradas

diretas ativadas em nível alto ou baixo, que podem ser escolhidos convenientemente

conforme a aplicação. Afigura abaixo demonstra símbolo de um flip-flops JK com

entradas diretas de preset e clear ativas em nível baixo.(CI 7474).

2.4.

Glossário - Flip flops e Registradores

Active-Low (Ativo em baixo): A entrada ou a saída de um terminal deve possuir o

sinal LOW para estar habilitado ou ativo.

Asynchronous (Assíncrono): è a condição em que a saída de um dispositivo troca seu

estado instantaneamente com a mudança da entrada independente do sinal de

relógio.

Clock (relógio): Os dispositivos usam um sinal digital periódico, que altera seu estado

de LOW para HIGH, constantemente.

Combinational Logic (Lógica Combinacional): É usado por muitos componentes

básicos (AND, OR, NOR, NAND) para formar funções lógicas mais complexas.

Complement (Complemento): Estado digital oposto - 0 é o complemento de 1 e viceversa.

Digital State (Estado digital): Nível lógico de um circuito digital.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

12

Disabled (Desabilitado): Condição na qual a entrada e a saída de um circuito digital

não estão aptos a aceitar ou transmitir estados digitais.

Edge Triggered (Trigado pela borda): O dispositivo digital só estará habilitado a

aceitar entradas ou alterar saídas somente na borda positiva ou negativa do sinal

de controle ou de relógio.

Enabled (Habilitado): A condição na qual o circuito está apto a receber ou transmitir

estados digitais.

Flip Flop (Flip flop): Circuito capaz de armazenar nível lógico 0 ou 1 baseado em

níveis lógicos seqüenciais.

Function Table (Tabela verdade): Indica as combinações mais importantes de

entrada e saída dos estados de um dispositivo.

Latch (latch): Capacidade de armazenar um particular estado digital. O circuito

armazena o nível lógico mesmo depois de alterada a entrada.

Level Triggeres (nível trigado): veja Pulse Triggered.

Master-Slave (Mestre-Escravo): Dispositivo de controle constituído de duas seções:

seção Mestre, que recebe os dados enquanto o relógio é HIGH, e a seção

Escravo, que recebe os dados do Mestre quando o relógio vai a LOW.

Negative Edge (Borda negativa): Quando a borda do relógio ou o pulso do trigger

transita de HIGH para LOW.

Noise (Ruído): Qualquer flutuação na tensão geradora momento de chaveamento,

cargas eletrostáticas podem causam irregularidades nos níveis das tensões: HIGH

e LOW de um sinal digital. Pode provocar erros nas leituras dos níveis lógicos.

Octal (Óctuplo): Um grupo de oito. Um flip flop octal é constituído de 8 flip flops em

um encapsulamento.

Positive Edge (Borda positiva): Quando a borda do relógio ou pulso de trigger

transita de LOW para HIGH.

Pulse Triggered (Pulso trigado): O termo se dá ao dispositivo digital que pode aceitar

pulsos de entrada durante os sinais de controle ou de relógio.

Register (Registrador): Grupo de flip flops ou latches que são usados para armazenar

palavras binárias e são controlados por um relógio ou sinal de controle comum.

Reset (Reset): A condição que produz o estado digital LOW.

Sequential Logic (Lógica Seqüencial): Circuito digital que envolve o uso de

seqüências d pulso de tempo em conjunto com dispositivos de armazenamento

como flip flops e latches e CIs funcionais como contadores ou registradores de

deslocamento.

Set (Seta): A condição que produz o estado digital HIGH.

Setup Time (Tempo de Setup): Tempo duração da borda ativa do pulso de trigger

(sinal de controle), necessário para estabilizar o sinal de entrada do dispositivo

digital.

Store Register (Registro de armazenamento): Dois ou mais circuitos de

armazenamento de daos (como flip flops ou latches) usados em conjunto para

armazenar bits de informações.

Strobe Gates (Componentes de controle): Um componente de controle usado para

habilitar ou desabilitar entradas ou saídas de um dispositivo digital particular.

Synchronous (Síncrono): A condição na qual a saída de um dispositivo operará

somente em sincronismo com um pulso específico ou sinal de trigger - HIGH ou

LOW.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

13

Toggle (Troca): Em um flip flop, toggle é quando o nível lógico Q muda para Q e Q

muda para Q.

Transition (Trânsito): Instante da transição do estado digital HIGH para LOW ou

LOW para HIGH.

Transparent Latch (Latch transparente): Dispositivo assíncrono no qual as saídas

armazenarão os estados mais recentes das entradas. A saída imediatamente segue

os estados das entradas sem esperar a chegada do pulso de trigger e mantêm os

estados mesmo depois das entradas serem removidas ou desabilitadas.

Trigger (Disparo): O sinal de controle de entrada de um dispositivo digital é usado

para especificar o instante em que o dispositivo aceita as entradas ou muda as

saídas.

2.5.

Aplicações e Exercícios

2.5.1. Uso do flip flop octal do tipo D em uma aplicação com Microcontrolador

Muitos dos latches e flip-flops básicos estão disponíveis em CIs octais. Nesta

configuração, estão oito latches ou flip flops em um simples encapsulamento.

Se todos os oitos latches ou flip flops são controlados por um relógio comum,

isto é chamado de registrador de 8 bits. Um exemplo de registrador de 8 bits a base de

flip flops é o CMOS 74HCT273 de alta velocidade (disponível nas famílias TTL LS e

S). O 74273 contêm 8 flip flops do tipo D, todos controlados com por um relógio

comum (Cp) trigados pela borda. Na borda positiva do Cp, os 8 bits de dados de D0 a

D7 são controlados nos 8 D flip flops e a saída de Q0 a Q7. O 74273 possui um reset

mestre ( M r ) ativo em baixo (LOW), o qual proporciona um reset assíncrono para

todos os flip flops.

Uma aplicação do 74273 D flip flop é mostrada abaixo. É usado um

registrador update e hold. A cada 10s ele recebe um pulso de relógio do

microcontrolador 68HC11 da Motorola. Os dados estão em D0 - D7 e a cada borda

positiva do relógio são dirigidos para os registradores e saídas Q0 - Q7.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

14

O sensor de temperatura analógico é usado para fornecer uma tensão de saída

proporcional à temperatura em graus centígrados. O microcontrolador 68HC11 tem a

capacidade de ler valores de tensão analógica e converter em valor digital equivalente.

O software do microcontrolador converte a palavra digital em código BCD de saída

para o mostrador.

A saída BCD do 68HC11 está em constante atualização de acordo com as

flutuações da temperatura. Uma maneira de estabilizar essas flutuações dos dados é o

uso de um registrador controlado, como o 74HCT273. O registrador só envia os dados

para a saída a cada 10s, facilitando assim a leitura.

Exercício 10-2: Usando a ferramenta da Xilinx desenhe a forma de onda da saída Q

para um S-R flip flop.

G

S

R

Q

Exercício 10-15:

O símbolo lógico de meio flip flop dual tipo D 7474, é apresentado na figura

abaixo:

a) Usando a ferramenta da Xilinx, desenhe a saída Q com as entradas

indicadas no diagrama.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

2.6.

15

Glossário - Considerações Práticas para Projetos Digitais

Duty Cycle: (Razão Cíclica): A razão entre a duração de tempo em que a onda

periódica é HIGH pelo período total da onda.

Float (flutuação): A condição na qual a entrada ou a saída em um circuito não é nem

HIGH nem LOW devido ao fato de não estar conectado diretamente a um nível de

tensão high ou low.

Hold Time (Tempo de espera): A duração de tempo, depois da borda do clock estar

ativa, que deve ser respeitado até que os dados estejam seguros para o seu

reconhecimento.

Hystetesis (Histerese): Em digitais, especialmente nos CI´s Schmitt triggers,

Histerese é a diferença de tensão entre o nível positivo de chaveamento e o nível

negativo de chaveamento.

Jitter: Termo usado em eletrônica digital para descrever formas de onda que possuem

algum grau de ruído eletrônico, causando ruído na subida e queda entre e durante a

transmissão do nível.

Power-Up: Termo usado para descrever o evento ou estado inicial quando se “liga”

um CI ou sistema digital

Pull_Down Resistor: Resistor com uma terminação ligada a LOW e a outra conectada

na entrada ou saída de uma linha, tal que, quando a linha está flutuando, a tensão nesta

linha será instantaneamente colocada no estado LOW.

Pull_Up Resistor: Resistor com uma terminação ligada a HIGH e a outra conectada

na entrada ou saída de uma linha, tal que, quando a linha está flutuando, a tensão nesta

linha será instantaneamente colocada no estado HIGH.

Race Condition: A condição na qual o nível digital (1 ou 0) está mudando de estado

no mesmo instante em que a borda de clock de um dispositivo síncrono, faz com que

o nível do sinal de entrada neste tempo seje indeterminado.

SPST Switch (Chave SPST): Abreviação de polo simples, polo throw. Uma chave

SPST é usada para fazer ou interromper o contato com uma linha elétrica simples.

2.6.

REGISTRADORES

Grupo de flip flops que tem por função armazenar bits.

1 flip flop armazena 1 bit

n flip flops armazenam n bits

2.6.1. Registradores de Deslocamentos Síncronos

Função: Deslocamento da informação contida para a esquerda ou para a

direita.

Aplicação:

- Transmissão Serial

- Conversão série paralela

- Multiplicação e Divisão por 2

Diagrama Lógico de um registrador de deslocamento universal.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

16

Função de Entrada dos Flip flops:

DA0 = ILSL + X0 P + A1 SR

DA1 = A0 SL + X1 P + A2 SR

DA2 = A1 SL + X2 P + A3 SR

DA3 = A2 SL + X3 P + IRSR

Pode ser acrescentado algo dos livros.

Introdução:

Registradores são necessários em sistemas digitais para armazenar

temporariamente um grupo de bits. Bits de dados (1´s ou 0´s) necessitam em sistemas

digitais ser temporariamente copiados, movidos, deslocados para a direita, deslocados

para a esquerda uma ou mais posições.

Um registrador de deslocamento facilita a manipulação desses bits de dados.

Muitos registradores de deslocamento podem lidar com movimento paralelo de bits,

assim como movimento serial, e podem ser usados para a conversão paralela e serial

paralela.

Tipos de Registradores de Deslocamento:

Conversão paralela para serial

Registrador Recirculante

Conversão serial para paralela

Contador em anel e Contador Johnson Shiff

Registrador de deslocamento 74164 8 bits entrada serial, saída paralela.

O 74164 possue duas entradas seriais (DSa e DSp ), lidas em sincronismo com a

borda positiva do clock (C P ). Cada borda do pulso positivo deslocará os bits de dados

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

17

uma posição para a direita. O MR é ativo em LOW, isto é, ele reseta todos os flip

flops quando possui pulso LOW.

Das

Dsb

Cp

MR

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

Exercício: Montar o circuito com a ferramenta Xilinx usando o diagrama

lógico e desenhe a forma de onda para uma conversão de serial para paralela do

número binário 11010010 usando o 74161, usando os seguintes sinais.

MR

Clk

0

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

9

Strobe

Cp

DSb

3.

1

1

0

1

0

0

1

0

Análise de Circuitos Seqüênciais

3.1.

Características e Estrutura das Máquinas Seqüências

Síncronas

Um circuito seqüencial caracteriza-se por ter a sua saída, ou uma amostra da

saída, realimentada para a entrada.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

10

ELC 419 - Sistemas Digitais A

Figura 1

18

- Diagrama de blocos de um sistema seqüencial.

Em outras palavras isto quer dizer que a próxima saída de uma máquina

seqüencial depende das entradas atuais e da saída atual desta máquina seqüencial. A

figura1 mostra um diagrama característico de um sistema seqüencial.

Nos circuitos seqüenciais podemos encontrar duas diferenças com relação a

figura acima:

1) A lógica de saída pode não existir. Neste caso a saída da máquina

seqüencial é o “Estado Atual” que corresponde a saídas dos flip-flops ou memória.

2) A saída também é função das entradas e não função única e exclusiva do

estado atual.

A estrutura de uma máquina seqüêncial ( ou de estados) é dividida em blocos

de lógica combinacional e de elementos de memória (flip-flops). Os blocos

combinacionais por sua vez geram os sinais de saída e as funções de entrada (ou

excitação) para os blocos de memória que fornecerão o próximo estado da máquina.

As máquinas de estado podem ser classificadas em dois tipos, conforme a

geração das saídas, Máquina de Mealy e Máquina de Moore.

3.2.

Tipos de Máquinas Seqüenciais

Quando a saída de uma máquina seqüencial é função apenas do estado atual

esta máquina é chamada de Moore, e quando a saída é função das entradas e do

estado atual a máquina é chamada de Mealy.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

19

As máquinas de Moore podem ser representadas por diagramas de estado

onde um círculo representa o estado atual, e uma seta representa a transição entre dois

estados (atual e futuro).

Neste caso, dentro de cada círculo, que representa o estado, coloca-se uma

letra ou número que identifique o estado e o valor das saídas correspondentes a este

estado, e em cada flecha que representa uma transição, coloca-se o valor das entradas

do circuito.

As máquinas de Mealy podem ser representadas por diagramas de estado

onde um circulo representa o estado atual, e uma seta representa a transição entre dois

estados (atual e futuro).

Neste caso dentro de cada círculo, que representa o estado, coloca-se uma

letra ou número que identifique o estado, e em cada flecha, que representa uma

transição, coloca-se o valor das entradas e das saídas.

Com estas máquinas seqüenciais síncronas (MSS) é possível fazer contadores

de qualquer seqüência, inclusive contadores tipo “up/down”, que contam

incrementando ou decrementando. Neste tipo de contador uma entrada indica o

sentido correto de contagem.

Na figura 2, abaixo podemos ver o diagrama de estados para um contador “up/down”

de 2 bits.

Figura 2 - Diagrama de estados para um contador “up/down”

Diagrama de estados de um contador “up/down” de 2 bits. “ud” é uma entrada

que determina o sentido da contagem.

Repare que cada estado da MSS está associado a saída dos flip-flops. Apesar

disto os nomes dos estados poderiam ser qualquer número ou letra.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

20

Neste exemplo, apenas como função mnemônica, o nome dos estados e o

valor de saída do contador são os mesmos. No caso de contadores os estados

costumam não ter nomes ficando definido apenas pelas saídas dos flip-flops.

Na prática podemos projetar máquinas com conjuntos de saídas Mealy e

Moore, porém esta distinção é necessária em projetos com dispositivos de lógica

programável.

O bloco de memória de estado pode ser construído com qualquer dos flipflops estudados no capítulo 2.

3.2.1. Procedimento para Análise de uma MSS

Considere a definição formal abaixo

PE = F (EA,X)

Z = G (EA,X) ou Z = G (EA)

Onde:

PE – próximo estado

EA – estado atual

X – entradas

Z – saídas

Lembrando que o conceito de estado implica no conhecimento do passado do

circuito. A análise de máquinas de estado pode ser dividida em três passos básicos.

1) Identificar as funções de próximo estado e saída F e S, respectivamente.

2) Através de F, G e da equação de estado do flip-flop usado no bloco de

memória, montar a tabela de estado que especifica completamente o

próximo estado e saídas do circuito para qualquer possível combinação de

estado atual e entradas.

3) Opcionalmente o diagrama de estado pode ser construído. Este diagrama

fornece a mesma informação da tabela de estado em uma forma gráfica,

conforme figura 3.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

21

Figura 3 - Tabela de estado em forma gráfica

As equações de entrada ou excitação são dadas por:

Do = Qo ⋅ EN + Qo ⋅EN

D1 = Q1⋅ EN + Q1 ⋅Qo ⋅ EN + Q1⋅ Qo ⋅ EN

Para o flip-flop tipo D temos que as equações de estado ou transição são dadas

por:

Qo (n + 1) = Do = Qo ( n) ⋅ EN + Qo ( n) ⋅ EN

Q1( n + 1) = D1 = Q1( n) ⋅ EN + Q1( n) ⋅Qo (n ) ⋅ EN + Q1(n ) ⋅ Qo ( n) ⋅ EN

Assim podemos montar a tabela de transição do bloco de memória como:

EA

Qo

Q1

0

0

1

1

0

1

0

1

Prof. José Renes Pinheiro, Dr.Eng.

PE/EN=0

Qo(n+1)

Q1(n+1)

0

0

0

1

1

0

1

1

PE/EN=1

Qo(n+1)

Q1(n+1)

0

1

1

0

1

1

0

0

[email protected]

ELC 419 - Sistemas Digitais A

22

A equação de saída é dada por : MAX = Q1⋅Qo⋅EN

E finalmente a tabela de estado que fornecerá o comportamento do sistema

seqüêncial é obtida convencionalmente chamando os estados atuais por letras como:

A para Qo(n) +0 e Q1(0) = 0, B para 0 1,C para 1 0 , D para 1 1.

EA

----------A

B

C

D

PE

EN=0

A

B

C

D

EN=1

B

C

D

A

Z

-----------0

0

0

1

Para termos uma representação gráfica podemos construir o diagrama de

estados. A flecha entre um estado e outro representa uma transição do sinal de clock,

enquanto que os valores das entradas e saídas são representados ao lado de cada

transição no formato Entrada/Saída.

Assim o diagrama de estados para o exemplo proposto é dado na figura 4:

Figura 4 - Diagrama de Estados

Como podemos observar a máquina de estado proposta foi construída com

arquitetura Mealy. O diagrama da figura 5 abaixo, mostra a representação de uma

máquina similar com arquitetura Moore, onde dentro de cada estado temos o fator de

saída.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

23

Figura 5 - Diagrama da Máquina de Moore

Portanto uma análise completa de um sistema seqüêncial engloba os seguintes

passos:

1) Determinar as equações de excitação para as entradas de controle dos flipflops.

2) Substitua as equações de excitação nas equações características (ou de

estado) dos flip-flops para obter as equações de transição.

3) Construa a tabela de transição com as equações de transição.

4) Determine as equações de saída.

5) Adicionar os valores de saída à tabela de transição, para cada estado

(Moore) ou estado/entrada (Mealy) criando a tabela de estado.

Opcionalmente pode-se dar nomes aos estados ao invés do código binário

das saídas dos flip-flops.

6) Desenhe o diagrama de estado.

A figura 6, mostra uma máquina de estados com flip-flops JK.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

24

Figura 6 - Máquina de estados com flip-flops JK.

O procedimento para análise é o mesmo só lembrando que agora a equação

característica do flip-flop é :

Q( n + 1) = J ⋅ Q( n) + K ⋅Q( n)

1) EQUAÇÕES DE EXCITAÇÃO

Jo = X ⋅ Y

Ko = X ⋅ Y + Y ⋅ Q1

J 1 = X ⋅ Qo + Y

K1 = Y ⋅ Qo + X ⋅Y ⋅Qo

2) EQUAÇÕES DE TRANSIÇÃO

Qo(n + 1) = J ⋅ Qo + Ko ⋅ Qo

Qo( n + 1) = X ⋅ Y ⋅ Qo + ( X ⋅ Y + Y ⋅ Q1) ⋅ Qo

Qo( n + 1) = X ⋅ Y ⋅ Qo + ( X ⋅ Y ⋅ Y ⋅ Q1) ⋅ Qo

Qo( n + 1) = X ⋅ Y ⋅ Qo + ( X + Y )(Y + Q1) ⋅ Qo

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

25

Qo( n + 1) = X ⋅ Y ⋅ Qo + X ⋅ Y ⋅ Qo + X ⋅ Q1⋅ Qo + Y ⋅ Q1 ⋅ Qo

Qo( n + 1) = X ⋅ Y ⋅ Qo ( n) + X ⋅ Y ⋅ Qo ( n) + X ⋅ Q1( n) ⋅ Qo + Y ⋅ Q1( n) ⋅ Qo

Q1(n + 1) = J1 ⋅ Q1(n ) + K1 ⋅ Q1

Q1(n + 1) = ( X ⋅ Qo + Y ) ⋅ Q1(n) + (Y ⋅ Qo(n) + X ⋅ Y ⋅ Qo) ⋅ Q1

Q1( n + 1) = X ⋅ Q1⋅ Qo + Y ⋅ Q1 + X ⋅ Y ⋅ Q1 + Y ⋅ Q1⋅ Qo + X ⋅ Q1 ⋅ Qo + Y ⋅ Q1⋅ Qo

3) EQUAÇÕES DE SAÍDA

Z = X ⋅ Q1 ⋅ Qo + Y ⋅ Q1 ⋅ Qo

4) TABELA DE TRANSIÇÃO

EA

Q1(n) Qo(n)

0

0

0

1

1

0

1

1

X

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Y

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

PE / Saída

Entradas X Y

0 0

0 1

1 0

0 0 /0

1 0 /1

0 1 /0

0 1 /0 1 1 /0

1 0 /0

1 0 /0

0 0 /0

1 1 /0

1 1 /0

1 0 /0

0 0 /1

Q1(n)

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

Prof. José Renes Pinheiro, Dr.Eng.

Qo(n)

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

J1

0

0

0

0

1

1

1

1

0

1

0

1

1

1

1

1

K1

0

0

0

0

1

0

1

0

0

1

0

1

1

1

1

0

1 1

1 0 /1

1 1 /0

0 0 /0

1 0 /1

Jo

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

Ko Q1(n+1) Qo(n+1)

0

0

0

0

0

1

0

1

0

0

1

1

0

1

0

0

1

1

1

0

0

1

1

0

1

0

1

1

1

0

1

1

1

1

0

0

0

1

0

0

1

1

1

0

0

1

0 (1)

0

[email protected]

ELC 419 - Sistemas Digitais A

26

Q1* = X ⋅ Q1 ⋅ Qo + Y ⋅ Q1 + X ⋅ Y ⋅ Q1 + Y ⋅ Q1 ⋅ Qo + X ⋅ Q1 ⋅ Qo + Y ⋅ Q1 ⋅ Qo

Qo* = X ⋅ Y ⋅ Qo + X ⋅ Y ⋅ Qo + X ⋅ Q1 ⋅ Qo + Y ⋅ Q1 ⋅ Qo

J 1 = X ⋅ Qo + Y

J

0

0

1

1

K1 = Y ⋅ Qo + X ⋅Y ⋅Qo

Jo = X ⋅ Y

K

0

1

0

1

Q*

Q

0

1

Q

Ko = X ⋅ Y + Y ⋅ Q1

5) TABELA DE ESTADO PARA : A= 0 0 ; B= 0 1 ;C= 1 0;D= 1 1

EA

A

B

C

D

PE / Z

Entradas X Y

0 0

0 1

A /0

C /1

B /0

D /0

C /0

A /0

D /0

C /0

1 0

B /0

C /0

D /0

A /1

1 1

C /1

D /0

A /0

C /1

Figura 7 - Diagrama da Máquina de estado

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

3.3.

27

PROCEDIMENTO PARA PROJETO DE MÁQUINAS DE

ESTADO

Os passos para projeto de uma MSS tem início em uma descrição ou

especificação de trabalho e ordem inversa ao procedimento de análise

estudado no capítulo anterior, como:

1) Construa a tabela e/ou diagrama de estados utilizando a descrição ou

especificação de trabalho desejada ao sistema digital.

2) Se possível minimize o número de estados na tabela de estados.

3) Selecione um conjunto de variáveis de estados [Qx(n),Qx(n+1)] e

relacionando as combinações destas com os estados da tabela de estados.

4) Substitua as combinações das variáveis das variáveis de estado na tabela de

estados para criar a tabela de transição, que mostra a próxima combinação

desejada para a variável de estado e para cada combinação da entrada.

5) Escolha um tipo de flip-flop para a memória de estado.

6) Construa a tabela de excitação que mostra os valores de excitação em

função das entradas e estados atuais.

7) Calcule as equações de excitação que satisfazem a tabela de excitação

(mapas de Karnaught ou outro método de simplificação.

8) Desenhe o diagrama lógico do circuito

3.4.

TABELA DE ESTADO

Existem várias maneiras de descrever uma máquina de estado, como

mapas ASM(Assembler) e linguagem de descrição de máquina de estados que

especifica indiretamente a tabela de estado. Porém aqui estudaremos apenas tabelas

que especificam diretamente o funcionamento da máquina.

A construção da tabela de estado ou diagrama de estado parte de uma

especificação ou descrição de trabalho, portanto utilizaremos um exemplo para

descrever o procedimento.

Exemplo1: Seja uma máquina seqüêncial que receba através de um par de

fios uma seqüência de pulsos e sinalize com nível lógico "1" sempre que os três

últimos bits forem 1. (OBS.: O clock da máquina e da transmissão serial são

iguais)

Figura 8 - Máquina Seqüêncial

A figura 9, mostra o diagrama de estados a) por Moore e b) por Mealy

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

28

Figura 9 - Diagrama de estados a) por Moore e b) por Mealy

Claramente observando os diagramas de estado observamos que por

Mealy é possível obtermos uma redução no número de estados, porém em alguns

casos a característica assíncrona das saídas Mealy pode trazer problemas. Nas

tabelas abaixo são mostrados os estados para ambos os diagramas acima

representados para o exemplo1.

EA

X=0

A

A

A

A

A

B

C

D

PE / Z

X=1

B

C

D

D

Z

0

0

0

1

(a) Tabela para Moore

EA

A

B

C

PE / Z

X=0

A /0

A /0

A /0

X=1

B /0

C /0

C /1

(b) Tabela para Mealy

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

3.5.

29

EXERCÍCIOS DE DIAGRAMA DE ESTADOS

Exercício 1

Projete um circuito sequencial observando o diagrama de estados e atribuição.

Use a tabela de estado reduzida, com atribuição binária - Atribuição 1. Use flip flop

JK. Apresentar o circuito lógico.

Tabela de Excitação do flip flop JK

Q(t) Q(t+1)

0

0

0

1

1

0

1

1

J

0

1

X

X

K

X

X

1

0

Tabela de Atribuições de Estados Binários reduzido

Estados

a

b

c

d

e

Atribuição

1

001

010

011

100

101

Atribuição

2

000

010

011

101

111

Diagrama de Estado da Atribuição 1

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

30

Tabela de Excitação - Atribuição 1

Est. Atual

A

0

0

0

0

0

0

1

1

1

1

B

0

0

1

1

1

1

0

0

0

0

Ent.

C

1

1

0

0

1

1

0

0

1

1

Próx.Estado

X

0

1

0

1

0

1

0

1

0

1

A

0

0

0

1

0

1

1

1

0

1

B

0

1

1

0

0

0

0

0

0

0

Saída do Circ. Comb. - Ent. FF´s

C

1

0

1

0

1

0

1

0

1

0

JA

0

0

0

1

0

1

X

X

X

X

KA

X

X

X

X

X

X

0

0

1

0

JB

0

1

X

X

X

X

0

0

0

0

KB

X

X

0

1

1

1

X

X

X

X

JC

X

X

1

0

X

X

1

0

X

X

KC

0

1

X

X

0

1

X

X

0

1

Saíd

a

Y

0

0

0

0

0

0

0

1

0

1

Mapas de Karnaught - Funções de entrada e saída

AB

JA

00

01

11

10

00

X

X

X

CX

01 11

X

1

1

X

X

X

X

10

AB

X

X

JA = BX

AB

KB

00

01

11

10

00

X

X

X

00

X

X

CX

01 11

X X

1

1

X X

X X

CX

01 11

X X

X X

X X

10

X

1

X

X

AB

JC

00

01

11

10

00

X

1

X

1

CX

01 11

X X

X

X X

X

JC = x

CX

01 11

X

X

1

00

X

X

X

10

X

X

X

1

X

1

JB =

10

X

X

X

X

CX

01 11 10

X 1

X X X

X X X

JB 00

00 X

AB 01 X

11 X

10

KA = C X

KB = C + X

Y

00

AB 01

11

10

KA

00

01

11

10

AB

KC

00

01

11

10

A

00

X

X

X

X

CX

01 11 10

X 1

X 1

X X X

X 1

KC = X

10

X

Y = AX

Desenhe o diagrama lógico do circuito 1:

Prof. José Renes Pinheiro, Dr.Eng.

X

[email protected]

ELC 419 - Sistemas Digitais A

31

Exercício 2

Repetir o exercício número 1 com Atribuição 2. Apresentar o circuito lógico.

Diagrama de Estado da Atribuição 2

Tabela de Excitação - Atribuição 2

Est. Atual

Ent.

A B C X

0

0

0

0

0

0

0

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

1

0

1

0

1

1

1

1

1

0

1

1

1

1

Próx.Estado

A

B

C

0

0

0

0

1

0

0

1

1

1

0

1

0

0

0

1

0

1

1

1

1

1

0

1

0

0

0

1

0

1

JA

0

0

0

1

0

1

X

X

X

X

Saída do Circ. Comb. - Ent. FF´s

KA

JB

KB

JC

KC

X

0

X

0

X

X

1

X

0

X

X

X

0

1

X

X

X

1

1

X

X

X

1

X

1

X

X

1

X

0

0

1

X

X

0

0

0

X

X

0

1

X

1

X

1

0

X

1

X

0

Saída

Y

0

0

0

0

0

0

0

1

0

1

Mapas de Karnaught - Funções de entrada e saída

JA

00

AB 01

11

10

00

X

X

CX

01 11

1

X

X

10

X

1

X

X

X

JA = B + CX

Prof. José Renes Pinheiro, Dr.Eng.

K

A

00

AB 01

11

10

00

CX

01 11

X

X

X

X

X

X

X

X

KA = B x

X

X

10

JB

X

X

1

00

AB 01

11

10

00

CX

01 11

10

X

X

X

1

X

X

X

X

X

X

1

JB = C X

[email protected]

X

X

X

ELC 419 - Sistemas Digitais A

KB

00

AB 01

11

10

00

X

X

X

CX

01 11

X

X

1

1

X

1

X

X

10

X

1

1

X

JC

00

AB 01

11

10

KB = X + C

Y

00

AB 01

11

10

00

1

X

X

32

CX

01 11

X

1

X

X X

X X

10

X

X

X

X

KC 00

00 X

AB 01 X

11 X

10 X

JC = B

00

CX

01 11

X

X

X

X

X

CX

01 11

X X

X

X

X

KC = x

10

X

1

1

Y = AX

Desenhe o diagrama lógico do circuito 2:

Exemplo 3:

Um somador completo, conforme figura abaixo, recebe duas entradas externas

X e Y, a terceira entrada Z vem de uma saída de um flip flop D. A saída carry (vaium) é transferida para o flip flop a cada pulso de clock. A saída externa S resulta da

soma de X, Y e Z. Assuma que X e Y varie após a transição de descida do pulso de

clock.

X

Somador

Y

Completo

Z

S

C

C

Q

D

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

10

X

1

1

ELC 419 - Sistemas Digitais A

33

Exemplo 4:

Projete um circuito sequencial com dois flip flops e uma entrada. Quando a

entrada for igual a 1, a saída do flip flop repete a seqüência 00, 01, 10. Quando a

entrada for igual a zero, eles repetem as seguintes seqüências: 11,10,01. Projete o

circuito com:

a) Flip flop tipo T

b) Flip Flop tipo D

Exemplo 5:

Projete um circuito com um flip flop e duas entradas conforme mostrado no

diagrama de temporização abaixo. A saída do flip flop é setada quando A=1 e B=0, e

é limpada quando A=1 e B=1 e é deixada no mesmo estado nos outros casos.

Clock

t

A

t

B

t

Q

t

Exemplo 6:

Projete um circuito seqüencial cujo diagrama de estados é dado. Use flip flops

tipo RS.

11/ 0

00 / 0

01 / 1

10 / 1

0

1

01 / 0

10 / 0

11 / 1

00 / 1

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

3.6.

34

SELEÇÃO DAS VARIÁVEIS DE ESTADO

A seleção das variáveis de estado consistem em determinarmos o código

binário de cada estado que será formado pelas saídas dos flip-flops. Ambos os

exemplos 1(a) e 1(b) necessitam no mínimo de 2 flip-flops para que possamos

representar todos os estados, pois temos

combinações possíveis ( onde n é o

número de flipflops).

Convenientemente podemos selecionar um outro tipo de código para os

estados utilizando mais flip-flops, isto resultará em um número menor de portas para

gerarmos os sinais de excitação dos flip-flops (equação de excitação menor). A tabela

abaixo mostra alguns códigos usuais onde o projetista deve escolher conforme a

necessidade e aplicação.

Estados

A

B

C

D

BCD

00

01

10

11

One-Hot

0001

0010

0100

1000

Quase One-Hot

000

001

010

100

Como pode ser observado os códigos da terceira e quarta coluna da tabela

exigem um número maior que o mínimo expressado na segunda coluna, porém estes

resultaram em um número menor de portas para construir a equação de excitação. A

diferença entre os códigos ONE-HOT e QUASE ONE-HOT está no estado inicial

"A", para nosso circuito, pois a inicialização do sistema é facilmente obtida através

das entradas diretas de clear (000) e preset (111) dos flip-flops.

Em alguns casos o número de estados é menor que o número de combinações

possíveis das saídas dos flip-flops

, com isto existirão estados não usados (ou

ilegais) como exemplo 1(b) por Mealy. Nestes casos existem duas aproximações:

-

-

Mínimo risco - Esta aproximação assume que o sistema pode ir para um

estado ilegal por motivo de falha no hardware, ou uma entrada insperada

ou erro no projeto, Então todas as combinações não usadas são

identificadas e se caso qualquer destas ocorrerem imediatamente o sistema

será levado ao estado inicial ou qualquer estado de segurança.

Mínimo custo - esta aproximação assume que a máquina de estados jamais

encontrará um estado ilegal, com isto as combinações não utilizadas

podem ser indicadas como "tanto faz" (X) na tabela de transição e assim

resultando em simplificações nas equações de excitação. Por outro lado

caso um estado ilegal ocorra um comportamento indefinido surgirá.

3.7.

TABELA DE TRANSIÇÃO

Para construirmos a tabela de transição basta substituirmos os nomes dos

estados pelas combinações escolhidas para as variáveis de estados como mostram as

tabelas a) e b) para os exemplos 1(a) e 1(b) respectivamente.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

EA

00

01

10

11

X=0

00

00

00

00

35

PE / Z

X=1

01

10

11

11

Z

0

0

0

1

(a) Máquina de Moore

EA

00

01

10

PE / Z

X=0

X=1

0 0 /0

0 1 /0

0 0 /0

1 0 /0

0 0 /0

1 1 /1

(a) Máquina de Mealy

(b)

3.8.

TABELA DE EXCITAÇÃO

Estando com a tabela de transição concluída o próximo passo é escolher o tipo

de flip-flop a ser usado e montar a tabela de excitação que na verdade é a tabela

de transição acrescida dos sinais de entrada dos flip-flops necessários para que o

próximo estado seja alcançado no próximo disparo (trigger).

As tabelas a) e b) abaixo ilustram o procedimento para nosso exemplo1,

utilizando flip-flops do tipo JK e D, respectivamente.

X

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Y

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Q1(n)

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

Qo(n)

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Prof. José Renes Pinheiro, Dr.Eng.

J1

0

0

0

0

1

1

1

1

0

1

0

1

1

1

1

1

K1

0

0

0

0

1

0

1

0

0

1

0

1

1

1

1

0

Jo

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

Ko Q1(n+1) Qo(n+1)

0

0

0

0

0

1

0

1

0

0

1

1

0

1

0

0

1

1

1

0

0

1

1

0

1

0

1

1

1

0

1

1

1

1

0

0

0

1

0

0

1

1

1

0

0

1

0 (1)

0

[email protected]

ELC 419 - Sistemas Digitais A

3.9.

36

EQUAÇÕES DE EXCITAÇÃO E DE SAÍDA

Agora utilizando mapas de Karnaught ou outro método de simplificação

podemos retirar as equações de excitação através das tabelas de excitação.

J1

Jo

K1

Ko

Exemplo 1b

D1

Prof. José Renes Pinheiro, Dr.Eng.

Do

[email protected]

ELC 419 - Sistemas Digitais A

37

3.10. Procedimento de Projeto através das Equações de Estado

Uma outra maneira para projeto de um circuito seqüencial, consiste em retirar-se as equações de excitação diretamente das equações de estado. Ao contrário do

método gráfico através da tabela de excitação, vista anteriormente, no método de

projeto por equações de estado as equações de excitação são obtidas analiticamente

através da equação característica do flip-flop utilizado no projeto. Portanto neste

método o ponto inicial para o projeto são as equações de estado que o descrevem,

estas equações por sua vez contem a mesma informação que a tabela de estado.

Exemplo1 - Projete um circuito seqüencial que tenha um comportamento

descrito pelas equações de estado abaixo:

QA n +1 = QC ⋅ QD + QC ⋅ QD

QB n+1 = QA

QC n+1 = QB

QD n +1 = QC

Como pode-se observar as equações descrevem o comportamento de um

circuito com quatro flip-flops (A,B,C e D). Este circuito é chamado de registrador de

deslocamento realimento do (feedback shift-register). Onde, a cada transição do sinal

de CLK, cada flip-flop desloca seu conteúdo para o próximo flip-flop e o estado de

determinados flip-flops determinarão o estado do primeiro flip-flop.

Neste tipo de procedimento a utilização de flip-flop tipo "D" é conveniente,

pois a equação característica (1), implica que as equações de excitação são iguais as

equações de estado.

Q n +1 = D

Equação característica do flip-flop "D"

Portanto para o exemplo temos:

DA = C D + CD

DB = A

DC = B

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

38

DD = C

E o circuito fica:

Exemplo 2 - Projete um circuito seqüencial com flip-flop JK que satisfaça as

seguintes equações:

A n+1 = A BCD + A BC + ACD + A C D

B n+1 = AC + C D + AB C

C n+1 = B

D n+1 = D

Agora com um flip-flop tipo JK é necessário a realização de um processo de

casamento entre as equações de estado acima com a equação característica do flipflop "JK" abaixo:

Q n+1 = J Q + K Q

Prof. José Renes Pinheiro, Dr.Eng.

equação do flip-flop JK

[email protected]

ELC 419 - Sistemas Digitais A

39

O processo de casamento consiste em arranjar e manipular as equações de

estado para que estas fiquem no formato da equação característica. Assim podemos

extrair as equações de excitação J e K. Desta forma temos

-

Para o flip-flop A

A n+1 = ( BCD + BC ) ⋅ A + (CD + C D ) ⋅ A

JA = BCD + BC = BC ( D + 1)

JA = BC

KA = CD + C D = (C + D) ⋅ (C + D )

KA = C ⋅ D + D ⋅ C

- Para o flip-flop B

B n+1 = ( AC + C D ) ⋅ (B + B ) + AB C

B n+1 = A BC + ABC + BC D + BC D + AB C

B n+1 = ( AC + C D ) ⋅ B + ( AC + C D + AC ) ⋅ B

JB = AC + C D

KB = AC + C D + AC = ( A + C ) ⋅ (C + D ) ⋅ ( A + C )

KB = A ⋅ (C + D )

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

40

- Para o flip-flop C

C n+1 = B = B (C + C ) = B C + BC

JC = B

KC = B

-

Para o flip-flop D

D n+1 = D = 1 ⋅ D + 0 ⋅ D

Logo:

JD = K D = 1

Exemplo 3 - Resolva o exemplo 1a pelo método de equações de estado.

Tabela de Estado

X

0

0

0

0

1

1

1

1

EA

Q1 Q0

0 0

0 1

1 0

1 1

0 0

0 1

1 0

1 1

Prof. José Renes Pinheiro, Dr.Eng.

PE

Q1(n+1) Q0(n+1)

0

0

0

0

0

0

0

0

0

1

1

0

1

1

1

1

Z

0

0

0

0

1

1

1

1

[email protected]

ELC 419 - Sistemas Digitais A

41

Equações de Estado

Q 1n+1

X \ Q1Q0

0

1

0 0

0

0

0 1

0

1

1 1

0

1

1 0

0

1

0 1

0

0

1 1

0

1

1 0

0

1

Q1 n+1 = X ⋅ Q 0 + X ⋅ Q1

Q 0 n+1

X \ Q1Q0

0

1

0 0

0

1

Q 0 n+1 = X ⋅ Q 0 + X ⋅ Q1

Aplicando o método de casamento para o flip-flop JK, temos:

Q1 n+1 = X ⋅ Q 0 + X ⋅ Q1

Q1 n+1 = X ⋅ Q 0(Q 1 + Q 1) + X ⋅ Q1

Q1 n+1 = X ⋅ Q 0 ⋅ Q 1 + X ⋅ Q 0 ⋅ Q1 + X ⋅ Q1

Q1 n+1 = X ⋅ Q 0 ⋅ Q 1 + ( X ⋅ Q 0 + X ) ⋅ Q1

J1 = X ⋅ Q0

K 1 = XQ0 + X = X (Q0 + 1)

K1 = X

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

42

Q 0 n+1 = X ⋅ Q 0 + X ⋅ Q1

Q 0 n+1 = X ⋅ Q 0 + X ⋅ Q 1(Q 0 + Q 0)

Q 0 n+1 = X ⋅ Q 0 + X ⋅ Q1Q 0 + XQ 1Q 0)

Q 0 n+1 = ( X + XQ1) ⋅ Q 0 + X ⋅ Q1Q 0

J 0 = X + XQ1 = X (Q1 + 1)

J0 = X

K 0 = XQ1

3.11. Simplificações na Máquina de Estados

Na maioria das vezes o diagrama de estados pode ser simplificado, pois

muitos estados ou são idênticos ou são equivalentes. Um estado é dito idêntico

quando conduz aos mesmos próximos estados, e produz as mesmas saídas. No

exemplo 3.1, a simplificação de estados redundantes foi deita pela eliminação direta

de estados idênticos.

Tabela 1.1: Tabela da verdade para o

exemplo 3.1.

Exemplo 3.1: Simplifique a tabela 1.1.

Na tabela 1.1, que representa uma

MSS, os estados “B” e “D” são

idênticos. Neste caso, esta tabela pode

ser reescrita substituindo-se a letra

“D” pela letra “B”.

Fazendo-se

as

substituições

necessárias na tabela 1.1 (os estados

“D” são trocados pelo estado “B”)

ainda existem estados idênticos como

podemos perceber na tabela 1.2. O

estados “A” e “E” podem ser

condensados em um único estado “A”.

Prof. José Renes Pinheiro, Dr.Eng.

E.A

A

B

C

D

E

P.E.

X=0

B/0

C/0

D/1

C/0

D/0

P.E.

X=1

C/1

A/1

B/0

A/1

C/1

Tabela 1.2: Tabela da verdade já

simplificada para o exemplo 1.3.

E.A.

A

B

C

P.E.

X=0

B/0

C/0

B/1

P.E.

X=1

C/1

A/1

B/0

E

B/0

C/1

[email protected]

ELC 419 - Sistemas Digitais A

43

Finalmente não há mais o que simplificar. A MSS original que possuia cinco estados e

necessitaria de três flip-flops para ser implementada, ficou com apenas três estados,

necessitando de apenas dois flip-flops. A tabela 1.3 corresponde a tabela 1.51simplificada ao

máximo.

Tabela 1.3: Tabela da verdade do exemplo 3.1. simplificada ao máximo.

E.A.

A

B

C

P.E.

X=0

B/0

C/0

B/1

P.E.

X=1

C/1

A/1

B/0

Note que na tabela 1.1. não foi possível identificar a igualdade entre os estados “A” e

“E”. Algumas vezes isto acontece de tal forma que não é possível reconhecer estados iguais

pela simples análise visual das tabelas da verdade. Nestes casos pode ser utilizada a técnica da

partição para se efetuar a simplificação destas tabelas.

Nesta técnica, todos os estados que conduzem as mesmas saídas são agrupados em

classes iguais. O nome dos novos estados será formado pelo seu nome original e um número

que indica a classe a qual pertence este estado. A partir deste ponto, sempre que estados de

uma mesma classe conduzirem a próximos estados em classes diferentes, estes estados atuais

serão divididos em outras classes. Este procedimento é repetido até que não existam mais

classes a serem criadas.

Exemplo 3.1: Simplifique a tabela 1.4 usando partição.

Tabela 1.4: Tabela da verdade de uma MSS hipotética.

E.A.

A

B

C

D

E

F

G

H

P.E.

X=0

B

D

G

H

G

G

D

H

P.E.

X=1

C

E

E

F

A

A

C

A

Z

X=0

0

0

0

0

0

1

0

0

Z

X=1

0

0

0

0

0

0

0

0

A principio todos os estados fazem parte da classe 1. O estado “F”, porém, possui

saída diferente dos demais, portanto vai formar a classe 2.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

E.A.

A1

B1

C1

D1

E1

F2

G1

H1

P.E. X=0

B1

D1

G1

H1

G1

G1

D1

H1

44

P.E. X=1

C1

E1

E1

F2

A1

A1

C1

A1

Como “F2” faz parte da classe 2, a classe 2 será formada apenas pelo estado F2 até o

fim da simplificação. Na classe 1, “D1” conduz a estados de diferentes classes (com relação

aos demais estados da classe 1) então fará parte da classe 3.

E.A.

A1

B1

C1

D3

E1

F2

G1

H1

P.E.

X=0

B1

D3

G1

H1

G1

G1

D3

H1

P.E.

X=1

C1

E1

E1

F2

A1

A1

C1

A1

Como “D3” é o único elemento da classe 3, a classe 3 será formada apenas por “D3”

até o fim da simplificação. Mas na classe 1, “B1” e “G1” conduzem a próximos estados da

classe 3 e 1 nesta ordem ao passo que “A1”, “C1”, “E1” e “H1” conduzem a estados da classe

1 e 1. Logo “B1” e “G1” farão parte da classe 4.

E.A.

A1

B4

C1

D3

E1

F2

G4

H1

P.E.

X=0

B4

D3

G4

H1

G4

G4

D3

H1

P.E.

X=1

C1

E1

E1

F2

A1

A1

C1

A1

Como “B4” e “G4” formam a classe 4, a classe 4 será formada apenas por “B4” e

“G4”. Porém nota-se que “A1”, “C1” e “E1” conduz a classes diferentes de “H1” o que

implica na criação da classe 5 para “A1”, “C1” e “E1”.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

E.A.

A5

B4

C5

D3

E5

F2

G4

H1

P.E.

X=0

B4

D3

G4

H1

G4

G4

D3

H1

45

P.E.

X=1

C5

E5

E5

F2

A5

A5

C5

A5

Nesta fase da simplificação não há mais o que mudar. Todos os estados de uma mesma

classe conduzem a estados de classes iguais. Logo, todos os estados que pertencem a uma

mesma classe são estados semelhantes e serão agrupados juntos. Então retomaremos a tabela

1.8 substituindo seus estados por:

Estados A, C e E serão representados por

Estados B e G serão representados por

Estado D será representado por

Estado F será representado por

Estado H será representado por

“a”

“b”

“c”

“d”

“e”

Desta forma obteremos a simplificação da tabela 1.4 (tabela 1.6).

Tabela 1.6: Tabela da verdade 1.4 simplificada ao máximo.

E.A.

a

b

c

d

e

P.E.

X=0

b/0

c/0

e/0

b/1

e/0

P.E.

X=1

a/0

a/0

d/0

a/0

a/0

Note que todos os estados que pertencem a uma mesma classe conduzem a estados que

pertencem a mesma classe quando X=0 e quando X=1. Entretanto a classe 2 e a classe 5

conduzem a classe 4 quando X=0 e a classe 5 quando X=1 mas não são iguais pois suas

saídas são diferentes!

Estas inúmeras tabelas de partição poderiam ter sido agrupadas lado a lado conforme

podemos ver na tabela 1.7.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

46

Tabela 1.7: Simplificação da tabela 1.4 colocando todas as tabelas de partição lado a lado.

C.S. quer dizer classe de saída e P.C.S. quer dizer próxima classe de saída.

E.A P.E. P.E. Z

.

X= X= X=

0

1

0

A

B

C

0

B

D

E

0

C

G

E

0

D

H

F

0

E

G

A

0

F

G

A

1

G

D

C

0

H

H

A

0

Z

C.S

P.C.

S

X=1

C.S

-

P.C.

S

X=0

X=

1

0

0

0

0

0

0

0

0

P.C.

S

X=1

C.S

-

P.C.

S

X=0

1

1

1

1

1

2

1

1

1

1

1

1

1

1

1

1

1

1

1

2

1

1

1

1

P.C.

S

X=1

C.S

-

P.C.

S

X=0

1

1

1

3

1

2

1

1

1

3

1

1

1

1

3

1

1

1

1

2

1

1

1

1

1

4

1

3

1

2

4

1

4

3

4

1

4

4

3

1

1

1

1

2

1

1

1

1

5

4

5

3

5

2

4

1

-

Uma outra forma de fazer a simplificação é por carta de implicação. Nesta carta são

evidenciadas todas as condições para que dois estados sejam iguais. Para exemplificar vamos

usar a mesma MSS usada anteriormente. A tabela 1.8 é uma cópia da tabela 1.6.

Na carta de implicação montamos uma espécie de mapa onde são anotadas todas a

condições para que um estado seja igual a outro estado. Para isto construímos um mapa onde

na primeira coluna e na última linha são colocados os estados da MSS. Na interseção de cada

uma destas linhas e colunas são anotadas as condições para que estes estados sejam iguais.

Aos poucos surgirão condições que não podem ser satisfeitas o que impede a igualdade de

vários estados. Estas impossibilidades vão sendo anotadas até que não existam mais. Neste

momento devemos anotar quais estados tem condição de serem iguais.

Tabela 1.8: Cópia da tabela 1.6.

E.A.

A

B

C

D

E

F

G

H

Prof. José Renes Pinheiro, Dr.Eng.

P.E.

X=0

B

D

G

H

G

G

D

H

P.E.

X=1

C

E

E

F

A

A

C

A

Z

X=0

0

0

0

0

0

1

0

0

Z

X=1

0

0

0

0

0

0

0

0

[email protected]

ELC 419 - Sistemas Digitais A

47

Passo 1)

B

F

BD

CE

BG

CE

BH

CF

BG

AC

X

G

BD

CE

H

BH

AC

A

DH

AE

B

C

D

E

DG

DH

EF

DG

AE

X

GH

EF

AE

DG

CE

GH

AE

C

X

GH

AF

X

X

DH

CF

AF

DG

AC

GH

X

D

E

F

X

DH

AC

G

Para montar esta carta de implicação devemos proceder da seguinte maneira:

-Na interceção da coluna “A” com a linha “B” vamos anotar o que é necessário para

que o estado “A” seja igual ao estado “B”: O estado “B” deve ser igual ao estado “D” e o

estado “C” deve ser igual ao estado “E”. Isto vem do fato de que os próximos estados e as

saídas de “A” e “B” devem ser iguais.

-Na interseção da coluna “B” com a linha “C” vamos anotar o que é necessário para

que o estado “B” seja igual ao estado “C”: O estado “D” deve ser igual ao estado “G” e o

estado “E” deve ser igual ao estado “E”.

-Na interseção da linha “F” com as outras colunas vamos anotar o que é necessário

para que o estado “F” seja igual aos demais estados: “F” não pode ser igual a ninguém. Isto se

deve ao fato de que as saídas do estado “F” são diferentes das saídas de todos os demais

estados. Desta forma, esta linha é marcada com a impossibilidade de simplificação - X.

-Devemos continuar preenchendo a carta de implicação desta maneira até que todas as

possibilidades tenham sido completadas.

-Todas as impossibilidades são anotadas com um X. Cada quadradinho marcado com

X é pintado para facilitar a visualização das impossibilidades.

Passo 2)

B

DH

EF X

DG

AE

X

GH

EF X

AE

F

BD

CE

BG

CE

BH

CF X

BG

AC

X

X

GH

AF X

X

G

BD

CE

H

BH

AC

A

DH

AE

B

DG

CE

GH

AE

C

DH

CF X

AF

X

D

C

D

E

Prof. José Renes Pinheiro, Dr.Eng.

DG

X

DG

AC

GH

X

E

F

X

DH

AC

G

[email protected]

ELC 419 - Sistemas Digitais A

48

Da primerira para a segunda carta de implicação continuamos marcando todas as

impossibilidades. Neste caso todos as condições que dependiam do estado “F” são marcadas

com impossibilidade pois “F” não pode ser simplificado com ninguém.

Passo 3)

B

C

D

E

F

G

H

BD

CE X

BG

CE

X

DG

X

X

BG

AC

X

DG

AE X

X

AE

X

X

X

X

BD

X

BH

AC

A

CE

DG

CE X

GH

AE

C

X

X

X

DG

AC X

GH

D

E

F

DH

AE X

B

X

X

DH

AC X

G

Nesta tabela constata-se que o estado “D” também não pode ser igual a nenhum outro

estado, todas as possibilidades de igualdade entre estados que dependam do estado “D”

também ficam impossibilitadas e são marcadas com um “X”.

Passo 4)

B

X

C

BG

CE

X

X

X

X

X

AE

X

F

BG

AC

X

X

X

X

X

G

X

CE

X

X

X

X

H

BH

AC X

A

X

GH

AE X

C

X

GH

X

E

X

X

F

G

D

E

B

D

Nesta carta nota-se que todas as combinações que dependam da igualdade entre os

estados “B” e “H” ou entre os estados “G” e “H” ficam impossibilitadas e são marcadas com

um “X”.

Não havendo mais nada para simplificar podemos dizer que todas as possibilidades

representam estados iguais. No nosso caso o estado “A” é igual ao estado “C” e ao estado “E”

pois a interseção entre a coluna “A” e as linhas “C” e “E” não foram marcadas com “X”. Da

mesma forma podemos dizer que o estado “C” é igual ao estado “E”, o que já era de se

esperar pois “A” é igual a estes dois estados.

Prof. José Renes Pinheiro, Dr.Eng.

[email protected]

ELC 419 - Sistemas Digitais A

49

Desta forma podemos montar uma tabela simplificada se substituirmos os estados da

tabela 1.9 por:

Estados A, C e E serão representados por

Estados B e G serão representados por

Estado D será representado por

Estado F será representado por

Estado H será representado por

“a”

“b”

“c”

“d”

“e”

Tabela 1.10: Tabela da verdade 1.9 simplificada ao máximo.

E.A.

a

b

c

d

e

4.

P.E.

X=0

b/0

c/0

e/0

b/1

e/0

P.E.

X=1

a/0

a/0

d/0

a/0

a/0

MEMÓRIAS

As memórias são circuitos eletrônicos capazes de reter informações sob a forma digital.

Elas podem reter “1” bit e neste caso especial podem ser constituidos, por exemplo, de um

Flip-Flop ou armazenar vários bits formando palavras ou dados. Se este dado possui “8”bits é

chamada “BYTE”, se possui “16”bits é chamada “WORD” mas também pode conter qualquer

outra quantidade de bits.