Relatório de Trabalho: atividades e análises

Diego Figueiredo

CERN, 2 de Julho de 2013

1

Introdução

•

GBTX: testes de performance do Chip (~70%)

– Learner Card

• Entendendo o mapeamento dos pinos da máquina IC Tester;

• Programando em linguagem STIL, XML e Java a máquina IC Tester (enviando e recebendo

sinais). Uso comercial.

– GBTX-LTB

• Contém FPGA. Utilizada para serializar e deserializar sinais (IC Tester é mais lento que o

GBTX);

• Testes na LTB (FPGA foi programada com counter)

– Enviamos e recebemos sinais do Tester para a LTB.

– Interface de Configuração do GBTX (I2C)

• Desenvolvendo interface em Java entre o IC Tester e o GBTX para envio de dados on-line

aos registros do chip. Será utilizado para configurar o GBTX durante os testes.

– GBTX-ICT

• Placa com soquete do GBTX. Utilizada para comunicar o IC Tester com o chip

(configuração do chip).

•

Análises Difrativas (~30%)

– Produção Central de Di-jatos Exclusivos;

– Produção Inclusiva de Z Difrativo.

2

Relatório: projeto chip GBTX

3

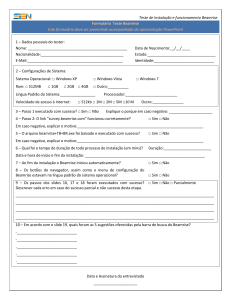

IC-Tester Setup

GBTX-LTB

Learner Card

VHDL/Verilog

representation of the

ASIC

Test vectors generated

from the simulations

Create/load the test

vectors onto the IC

tester

IC Tester

Perform the test

Validade the

ASIC

performance

4

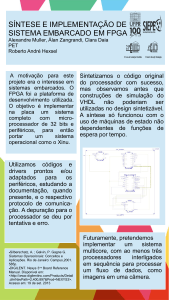

GBTX TX/RX Test

Optical link

@ 4.8 Gb/s

GBTX-ICT

Conn. D

Conn. C

GBTX-LTB

Conn. B

Load board 2012

Sapphire IC Tester

Conn. A

@ 320 Mb/s

5

GBTX TX/RX Test

GBTX Socket

GBTX LTB

GBTX ICT

IC Tester Loadboard

6

Relatório: análises

7

Análise Difrativa: Produção inclusiva de Z difrativo

https://twiki.cern.ch/twiki/bin/viewauth/CMS/DiffractiveZAnalysis

• Análise dos dados de 2010 RunA e RunB, canais de elétrons e múons.

– Software

• Informações de RECO e PAT de candidatos múons e elétrons. Isolamentos, variáveis

cinemáticas, variáveis difrativas e informações do CASTOR. Utilizando pacote PAT

FWD.

– Amostras

• Ntuples de múons criadas (dados e monte carlo).

– Status

• Resultados compatíveis com nota de análise do grupo de Electroweak (CMS EWK10-005) no canal de múons. Mesmos cortes aplicados.

• Processando amostras de elétrons (Julho).

– Planejamento

• Análise de Energy Flow para definir os gaps (Julho);

• Seleção difrativa “a La Hera” ou utilizando ηmax e ηmin e CASTOR (Julho/Agosto).

8

9

Análise Difrativa: Produção Central de Di-jatos Exclusivos

https://twiki.cern.ch/twiki/bin/view/CMS/FwdPhysicsExclusiveDijetsAnalysis

•

Análise dos dados de 2010 RunB

– Software

• Macros de Análise foram atualizadas. Fatores de escala, pile-up reweight, correções do

trigger e das eficiências podem ser aplicados on-line. Utilizando pacote PAT FWD.

• Necessário Update em alguns métodos que estão repetidos em diferentes módulos.

– Status

• Amostras serão reprocessadas com nova variável: traços não associados aos jatos e

CASTOR tagged.

– Planejamento

• Refazer análise com novos cortes (Julho/Agosto);

• Estabelecer limites estatísticos nos excessos dos dados(Agosto/Setembro);

• Escrever AN (Julho/Agosto/Setembro).

10

11

Backup Slides

12

Learner Card I/O Loopback

Orange: programmed

Yellow: input

Blue: output

13

GBTX-LTB I/O FPGA Loopback

Yellow: inputs

Blue: outputs

H5 appears

stuck at one

14

GBTX-LTB 4-bit counter Test – Direct SE clock input

Yellow: inputs

Blue: outputs

Clock_in

Carry

Out [3:0]

15