ESTUDO DO EFEITO DA ESPESSURA DA CAMADA DE ÓXIDO

ENTERRADO NOS PARÂMETROS ELÉTRICOS DE TRANSISTORES

SOI DE MÚLTIPLAS PORTAS

Érika Harumi Yamanaka1, Rodrigo Trevisoli Doria1

Departamento de Engenharia Elétrica - Centro Universitário da FEI

[email protected] ; [email protected]

Resumo: Este trabalho apresenta o efeito da variação

da espessura das camadas de silício (tSi) e de óxido

enterrado (tbox) nas principais características elétricas de

transistores SOI de porta tripla. A análise feita a partir das

simulações computacionais teve como objetivo obter os

gráficos de tensão de limiar (Vt) por tensão de substrato

(Vs) e de corrente Ion e Ioff em função de Vs.

0,68

0,64

0,52

0,48

0,44

0,40

-3

-2

3. Resultados

0

Vs (V)

1

2

3

Ion/Ioff (A/A)

1E9

1E8

2. Metodologia

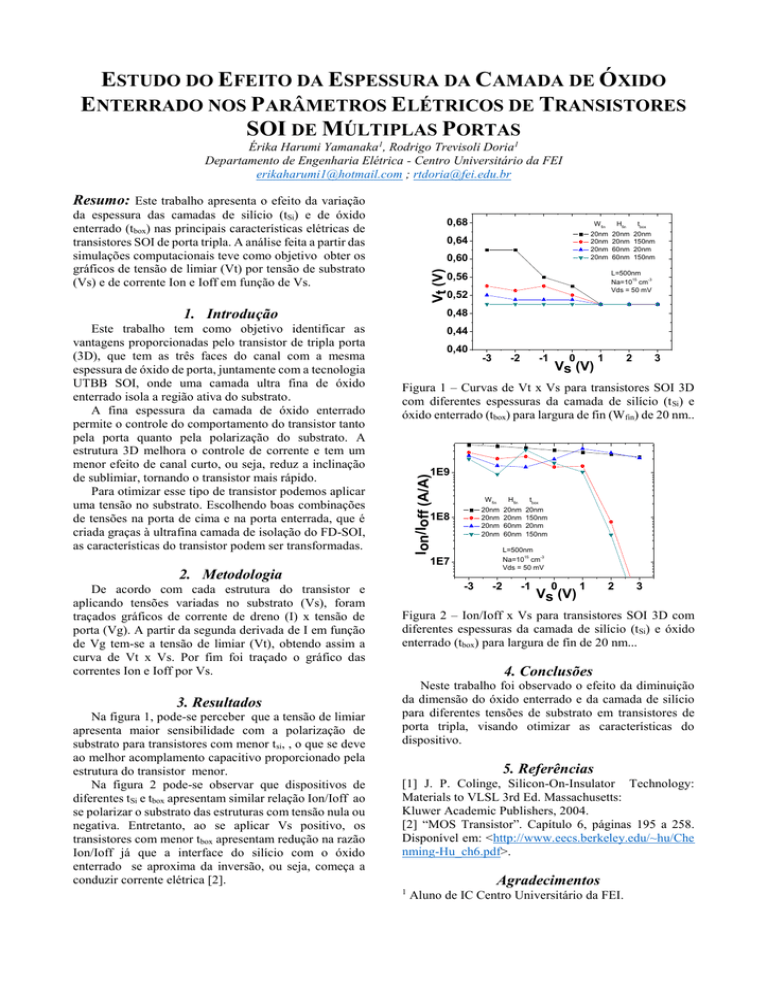

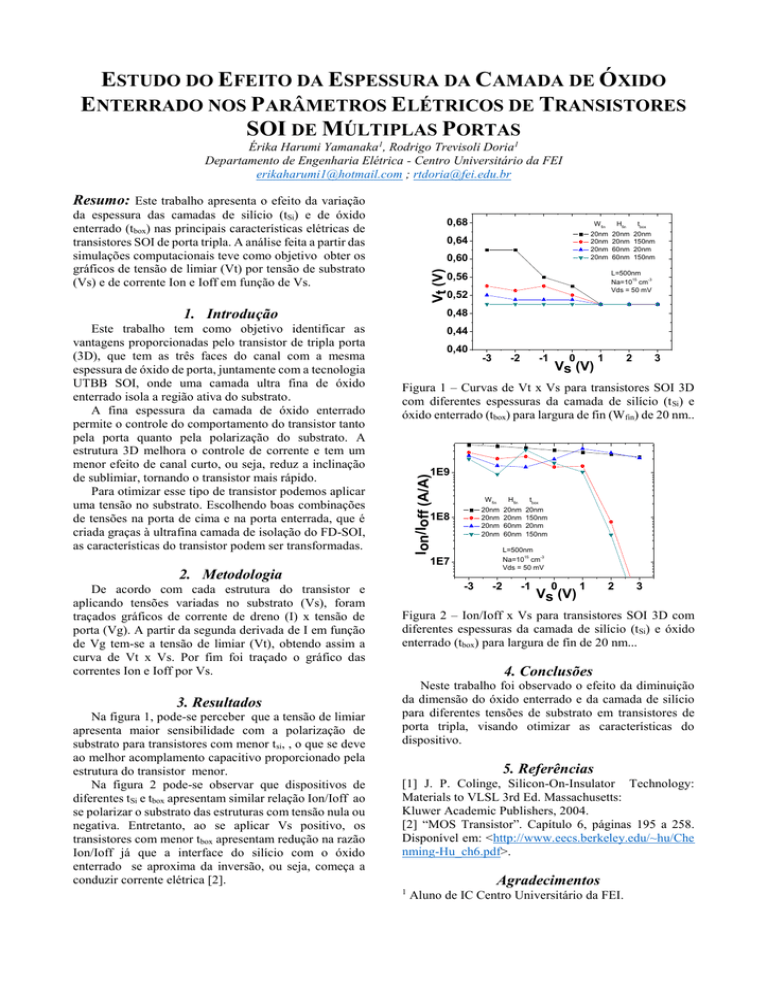

Na figura 1, pode-se perceber que a tensão de limiar

apresenta maior sensibilidade com a polarização de

substrato para transistores com menor tsi, , o que se deve

ao melhor acomplamento capacitivo proporcionado pela

estrutura do transistor menor.

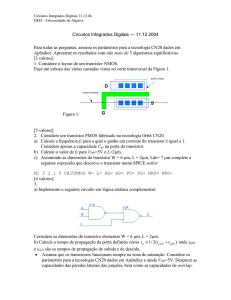

Na figura 2 pode-se observar que dispositivos de

diferentes tSi e tbox apresentam similar relação Ion/Ioff ao

se polarizar o substrato das estruturas com tensão nula ou

negativa. Entretanto, ao se aplicar Vs positivo, os

transistores com menor tbox apresentam redução na razão

Ion/Ioff já que a interface do silício com o óxido

enterrado se aproxima da inversão, ou seja, começa a

conduzir corrente elétrica [2].

-1

Figura 1 – Curvas de Vt x Vs para transistores SOI 3D

com diferentes espessuras da camada de silício (t Si) e

óxido enterrado (tbox) para largura de fin (Wfin) de 20 nm..

W fin

Hfin

20nm

20nm

20nm

20nm

20nm

20nm

60nm

60nm

tbox

20nm

150nm

20nm

150nm

L=500nm

15

-3

Na=10 cm

Vds = 50 mV

1E7

De acordo com cada estrutura do transistor e

aplicando tensões variadas no substrato (Vs), foram

traçados gráficos de corrente de dreno (I) x tensão de

porta (Vg). A partir da segunda derivada de I em função

de Vg tem-se a tensão de limiar (Vt), obtendo assim a

curva de Vt x Vs. Por fim foi traçado o gráfico das

correntes Ion e Ioff por Vs.

tbox

20nm

150nm

20nm

150nm

L=500nm

15

-3

Na=10 cm

Vds = 50 mV

0,56

1. Introdução

Este trabalho tem como objetivo identificar as

vantagens proporcionadas pelo transistor de tripla porta

(3D), que tem as três faces do canal com a mesma

espessura de óxido de porta, juntamente com a tecnologia

UTBB SOI, onde uma camada ultra fina de óxido

enterrado isola a região ativa do substrato.

A fina espessura da camada de óxido enterrado

permite o controle do comportamento do transistor tanto

pela porta quanto pela polarização do substrato. A

estrutura 3D melhora o controle de corrente e tem um

menor efeito de canal curto, ou seja, reduz a inclinação

de sublimiar, tornando o transistor mais rápido.

Para otimizar esse tipo de transistor podemos aplicar

uma tensão no substrato. Escolhendo boas combinações

de tensões na porta de cima e na porta enterrada, que é

criada graças à ultrafina camada de isolação do FD-SOI,

as características do transistor podem ser transformadas.

Hfin

20nm

20nm

60nm

60nm

Vt (V)

0,60

W fin

20nm

20nm

20nm

20nm

-3

-2

-1

0

Vs (V)

1

2

3

Figura 2 – Ion/Ioff x Vs para transistores SOI 3D com

diferentes espessuras da camada de silício (tSi) e óxido

enterrado (tbox) para largura de fin de 20 nm...

4. Conclusões

Neste trabalho foi observado o efeito da diminuição

da dimensão do óxido enterrado e da camada de silício

para diferentes tensões de substrato em transistores de

porta tripla, visando otimizar as características do

dispositivo.

5. Referências

[1] J. P. Colinge, Silicon-On-Insulator Technology:

Materials to VLSL 3rd Ed. Massachusetts:

Kluwer Academic Publishers, 2004.

[2] “MOS Transistor”. Capítulo 6, páginas 195 a 258.

Disponível em: <http://www.eecs.berkeley.edu/~hu/Che

nming-Hu_ch6.pdf>.

Agradecimentos

1

Aluno de IC Centro Universitário da FEI.