4/5/2010

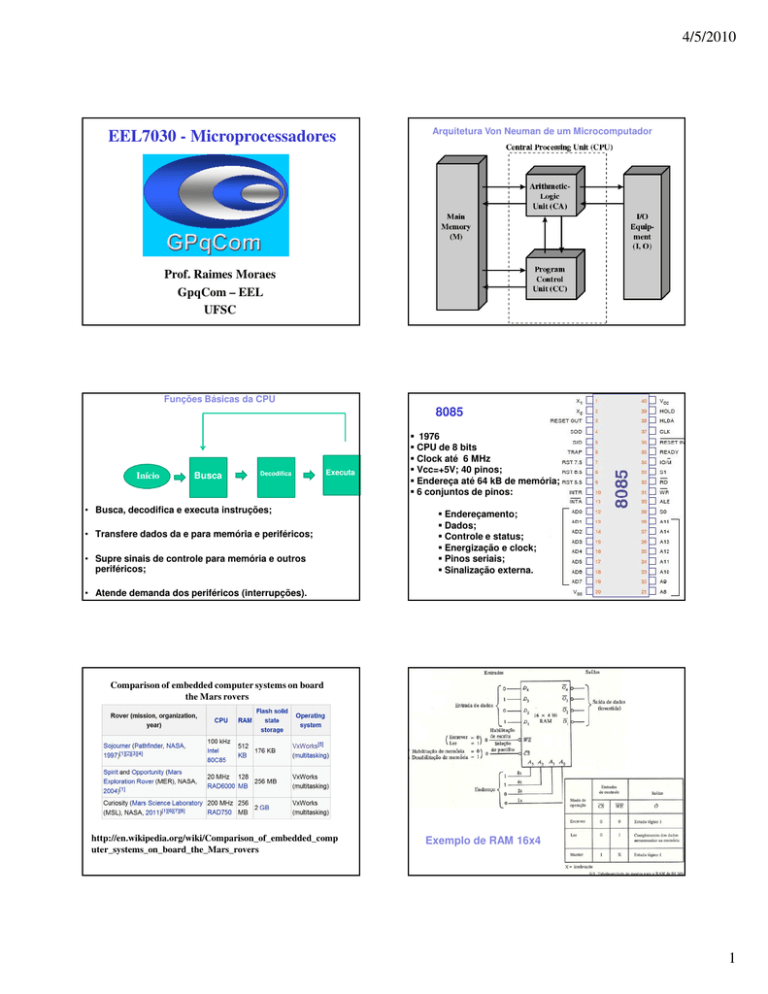

EEL7030 - Microprocessadores

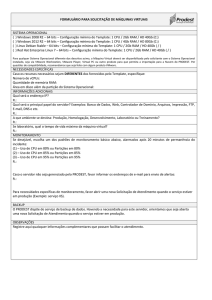

Arquitetura Von Neuman de um Microcomputador

Prof. Raimes Moraes

GpqCom – EEL

UFSC

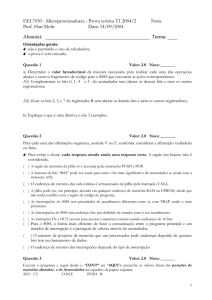

Funções Básicas da CPU

8085

Início

Busca

Decodifica

Executa

• Busca, decodifica e executa instruções;

• Transfere dados da e para memória e periféricos;

• Supre sinais de controle para memória e outros

periféricos;

1976

CPU de 8 bits

Clock até 6 MHz

Vcc=+5V; 40 pinos;

Endereça até 64 kB de memória;

6 conjuntos de pinos:

Endereçamento;

Dados;

Controle e status;

Energização e clock;

Pinos seriais;

Sinalização externa.

• Atende demanda dos periféricos (interrupções).

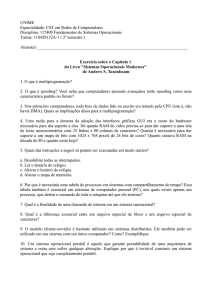

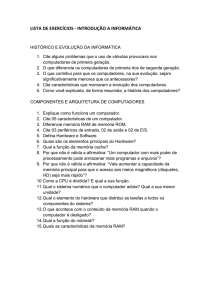

Comparison of embedded computer systems on board

the Mars rovers

http://en.wikipedia.org/wiki/Comparison_of_embedded_comp

uter_systems_on_board_the_Mars_rovers

Exemplo de RAM 16x4

1

4/5/2010

Exemplo de Escrita em RAM 16x4

DADO

ADn

Interface do

Microprocessador

Com

Memória

DADO

ADn

Dn

74HC373

74HC373

8085

RAM

Latch

G

LE

ALE

An

ADDR

8085

Interface do

Microprocessador

Com

Memória

Dn

RAM

Latch

G

LE

ALE

An

ADDR

Exemplo de Acesso à Memória

Escrita

WR

RD

WR

RD

WR

RD

WR

RD

Passos para execução de instrução

ADn

DADO

74HC373

8085

Dn

RAM

Latch

ALE

An

WR

RD

G

LE

ADDR

WR

RD

Exemplo de Acesso à Memória

Leitura

1) Endereço inicial (0000H) contido em PC é colocado no

barramento de endereços (AD0-AD7) & (A8_A15). PC é

incrementado.

2) Unidade de Controle (UC) coloca ALE (Address Latch Enable)

em ‘1’ durante metade do ciclo de clock. Colocado em ‘0’ no

restante do ciclo de leitura. Utilizado para salvar endereço em

AD0-AD7 no latch.

3)

Unidade de Controle coloca pino RD em ‘0’ .

4) Memória coloca dado no barramento de dados (AD0-AD7)

5) Valor em (AD0-AD7) é transportado para decodificador de

instrução (Instruction Register). Controlado por RD.

6) Após decodificar a instrução, UC emite sinais de controle

para executar tarefa demandada.

2

4/5/2010

Arquitetura simplificada de uma CPU

Registradores do 8085

Arquitetura

Simplificada

do 8085

Arquitetura Simplificada do

8085

PINOS de STATUS

S0

S1

ESTADO

0

0

RETENÇÃO

0

1

ESCRITA

1

0

LEITURA

1

1

INTERRUPÇÃO

Utilizados para testes de sistemas em desenvolvimento

Interface do 8085 com

demultiplexador e

decodificador

3

4/5/2010

REGISTRADOR

A

B

C

D

E

H

L

M

Algumas Instruções do 8085

PAR REGISTRADORES

MOV r1,r2

Instrução

3 bits

1o. Operando

3 bits

2o. Operando

0

D

S

D

Instrução

D

RP

BC

00

DE

01

HL

10

SP

11

Exercício: Obter o código das instruções abaixo

2 bits

Opcode

1

DDD ou SSS

111

000

001

010

011

100

101

101

S

S

MVI A,07

MVI B, 01

ADD B

LDAX rp

2 bits

Opcode

2 bits

4 bits

0

RP

1010

OBS: ADD r; 10000sss

0

Exercício: Solução

MVI A,07; 3EH (0011 1110B) 07H

MVI B, 01; 06H (0000 0110B) 01H

ADD B; 80H

4

4/5/2010

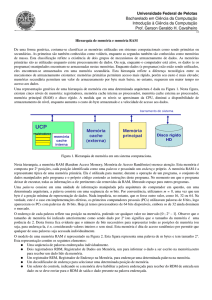

Configuração Básica de Sistema Microprocessado

Kit

Telemática

8085

Console

de

Controle

CPU

Memória

RAM

Memória

ROM

8279

8155A

Dispositivos

de Entrada

e Saída

8155B

2716B

Barramento

2716A

Diagrama de Blocos Kit Telemática

Endereçamento Kit Telemática

Endereço

ATRIBUIÇÃO

0000H a 07FFH

ROM BÁSICA

0800H a 0FFFH

EXPANSÃO DE ROM

1800H e 1900H

CONTROLADOR 8279

2000H a 20FFH

RAM BÁSICA

2800H a 28FFH

EXPANSÃO DE RAM

Organização da

Memória

ABACUS

•ROM: 0000 a 1FFFH

•RAM: 2000 a 23FFH

5

4/5/2010

Exercício

1: B = N, soma = 0

2: soma = soma + B, B = B - 1

3: IF B ≠ 0 then GOTO 2 (?)

4: total = soma

REGISTRADOR de FLAGS

S

Z

0

FLAG

AC

0

P

1

C

SETADO SE OPERAÇÃO TEM RESULTADO :

S (SINAL)

NEGATIVO

Z (ZERO)

ZERO

AC (CARRY AUXILIAR)

VAI ou VEM 1 do BIT3 para o BIT4 do Acc

P (PARIDADE)

PARIDADE PAR (NRO DE ‘1’s no Acc é PAR)

C (CARRY)

VAI ou VEM 1 (Operações aritméticas)

FLAGS no Livro Ziller

Auxiliary Flag & BCD (Binary Coded Decimal)

Instrução DAA & ADD r

Instrução DCR r

Z

S

P

C

A

*

*

*

-

*

Soma BCD

Supondo flags atuais como

FLAG

MODIFICADO PELA INSTRUÇÃO

*

SIM

-

NÃO

Z

S

P

C

A

*

*

*

*

*

Z

S

P

C

A

0

0

0

0

0

[A]=98H; [B]=08H

ADD B

0

1

1

0

1

[A]=A0H; [B]=08H

DAA

0

0

1

1

0

[A]=06H; [B]=08H

6

4/5/2010

Exercício

Loop:

N:

total:

LDA N

MOV B, A

XRA A

ADD B

DCR B

JNZ Loop

STA total

JMP $

DB 5

DB 0

i=n

soma = A ⊕ A = 0

soma = soma + i

i=i-1

IF i ≠ 0 THEN GOTO Loop

total = soma

7