Experiência 01

Oscilador e Sequenciador Binário - Decimal

Thiago Valentin de Oliveira

29/09/2010

1

Introdução

Esta experiência consta basicamente da união dos ramos analógico e digital da Eletrônica. Abordamos

a construção de um oscilador astável utilizando um chip LM555 e o estudo analógico por trás desse

processo. Como aplicação, utilizaremos um contador, decodificadores, display e LED’s para criar um

sequenciamento numérico binário e decimal, constituindo o sistema digital do projeto.

Em suma, criamos uma onda quadrada que irá alimentar um circuito lógico. Este último realizará

uma contagem decimal (0 a 9), mostrando de três formas diferentes o valor da contagem: representação

binária através de LED’s, representação decodificada em decimal através de LED’s e representação do

algarismo correspondente em display de sete segmentos. As três exibições são independentes e qualquer

uma delas pode ser omitida sem comprometer o funcionamento do circuito.

Como teste, adicionaremos um circuito simples anti-bouncing, isto é, um circuito anti-trepidação. Ele

será usado para testar a implementação digital do circuito de forma manual, independente do oscilador

que estamos utilizando.

Se você é engenheiro formado, aluno de graduação ou mesmo um desconhecido no assunto, não

deverá encontrar dificuldades ao realizar este projeto, já que tentarei expor as ideias da forma mais

clara possı́vel. Por outro lado, se você é estudante da área e gostaria de aprofundar um pouco mais o

conhecimento da Eletrônica, além do Cálculo e da Fı́sica por trás desta, este texto pretende cumprir tal

papel.

2

Material Necessário

Antes de prosseguirmos, devemos tomar nota do material necessário para executar esse projeto. Cito

abaixo a relação do material que foi utilizado por mim, mas deve ficar claro que outros componentes

podem ser usados.

• 1 Protoboard de 1680 pinos

• 1 Fonte DC - 5,0 V - 1,0 A

• 1 CI LM 555

• 1 CI TTL 7490 - Contador de década

• 1 CI TTL 7442 - Decodificador BCD - Decimal

• 1 CI TTL 7448 - Decodificador BCD - 7 segmentos

• 1 CI TTL 7400 - 4 portas Nand de 2 entradadas cada

• 24 Resistores de 330 Ω ou 470 Ω

• 2 Resistores de 10 KΩ

1

• 2 Resistores de 100 KΩ ou 1 MΩ *

• 1 Capacitor de 10 nF a 1 µF

• 1 Capacitor de 100 µF

• 1 Capacitor de 10 µF *

• 1 Capacitor de 1 µF *

• 15 LED´s

• 1 Display de Sete Segmentos Catodo Comum

• Fios para conexão na Protoboard

Os itens marcados com um asterisco (*) são dispensáveis em um primeiro momento, mas eles serão

utilizados para fazer algumas mudanças após a montagem do circuito e verificar como varia seu comportamento.

Seria interessante, se possı́vel, ter um multı́metro digital em mãos (ou mesmo um voltı́metro analógico

ou digital) para que você possa fazer alguns testes e medidas e corrigir possı́veis erros durante o processo.

Mas se não tiver tal material, não se preocupe: realizando o passo-a-passo indicado, nenhum problema

deverá ocorrer.

3

LM 555

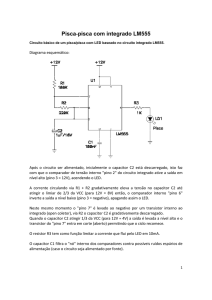

Neste projeto, estamos interessados em construir um oscilador astável à partir de um CI 555, de modo

que estudar um pouco o funcionamento desse chip se faz necessário.

O circuito integrado LM 555 (e outros como NE 555, CA 555 e MC 1455) é um temporizador

ou timer que opera em dois modos básicos: o modo monoestável e o modo astável. O primeiro

consiste em um pequeno pulso controlado, que é ativado por uma das entradas do chip; a saı́da produzida

é um sinal em nı́vel lógico 0, que muda para nı́vel lógico 1 e permanece por um intervalo de tempo prédeterminado, depois voltando ao nı́vel lógico 0 e assim permanecendo até que outra entrada chegue ao

chip. Neste caso, ocorre apenas um estado estável: o nı́vel baixo.

O segundo modo é o que vamos utilizar e consiste numa modificação do primeiro: vamos gerar o

mesmo pulso que o monoestável, mas o próprio pulso servirá para realimentar o circuito, de modo que

este pulso será seguido por outro e por outro, indefinidamente. Em outras palavras, obtemos uma onda

retangular e, por isso, não ocorre nenhum estado estável, já que se trata de um sinal periódico.

3.1

Circuito Interno do 555

Abaixo ilustramos a pinagem (figura 1) e o circuito interno (figura 2) de um CI 555. Observe o

diagrama dos pinos e as interligações entre os amplificadores operacionais, o flip-flop, o transistor, os

resistores e os pinos de entrada e saı́da.

Figura 1: Pinagem do Chip 555

2

Figura 2: Circuito Interno do 555

O funcionamento interno do circuito será estudado nos modos de operação do temporizador, bem

como as conexões externas que devem ser feitas aos pinos do chip.

A tabela 1 mostra os oito pinos disponı́veis no chip, os nomes e a função de cada um. O pino #RESET

com uma tralha à esquerda indica que o sinal ativo é o de nı́vel baixo.

1

2

3

4

5

6

7

8

GND

TRIG

OUT

#RESET

CONT

THRES

DISCH

VCC

Ground - Terra: nı́vel lógico 0

Trigger - Entrada de disparo

Saı́da do sinal onda quadrada

Resetar flip-flop SR com nı́vel lógico 0

Control - Controle do amplificador operacional ligado ao Set do SR (default: 2Vcc /3)

Thereshold - Limiar: quando a voltagem em THR supera a de CTRL, o pulso acaba

Discharge - Descarga: saı́da em coletor aberto; é usado para descarregar o capacitor

Nı́vel lógico 1

Tabela 1: Pinagem do CI 555

3.2

Operação Monoestável

A figura 3 ilustra a conexão externa que deve ser feita ao 555 para permitir seu funcionamento como

monoestável. São necessários um resistor e um capacitor (R = 10 KΩ e C = 100 µF, respectivamente),

além de um capacitor de capacitância bem pequena (indicado entre 10 nF e 1 µF).

O pino 8 está em nı́vel alto (Vcc ) e o pino 1 está em nı́vel baixo (GND). Entre eles, há uma linha de

Vcc

três resistores em série, de modo que, em cada um, há uma queda de tensão de

. Assim, a entrada

3

2

inversora do operacional superior está fixa em Vcc e a entrada não inversora do operacional inferior

3

Vcc

está fixa em

.

3

Inicialmente, o SR está com saı́da Q alta (já que Q está baixo). O transistor está ON e o terra é

transmitido ao pino 7, fazendo com que o capacitor se mantenha descarregado. Quando um disparo

chega no pino 2, o operacional inferior é ativado, emitindo um sinal de reset ao SR. A saı́da Q se torna

baixa e Q se torna alta; é o inı́cio do pulso na saı́da 3. Como Q = 0, o transistor corta, desconectando o

pino 7. Assim, uma corrente flui através do resistor R, passando pelo capacitor e carregando-o. A tensão

2

no capacitor é usada como limiar no pino 6, de modo que ao atingir cerca de Vcc , o operacional superior

3

emite um sinal de set ao SR, fazendo Q voltar a nı́vel alto e Q a nı́vel baixo. Novamente em modo de

3

Figura 3: Operação Monoestável

saturação, o transistor conduz nı́vel baixo ao pino 7, descarregando o capacitor. Assim, o circuito volta

à sua estabilidade inicial.

O que interessa como projetista é poder calcular o tempo T1 em que a saı́da está em nı́vel lógico 1. Da

explicação acima, vimos que esse perı́odo equivale ao tempo de carga do capacitor. Não vamos considerar

os atrasos do amplificador operacional e do flip-flop SR, já que eles são da ordem de nanossegundos e

seus efeitos se compensam com um atraso na transição 0 → 1 em Q e depois na transição 1 → 0 em Q.

No intervalo de tempo que o capacitor está se carregando temos o seguinte modelo: uma fonte

contı́nua de tensão Vcc associada em série com um resistor de resistência R e um capacitor de capacitância

C, ligado ao terra.

Devemos lembrar, agora, algumas fórmulas de circuitos elétricos. A Lei de Ohm fornece a relação

entre voltagem, resistência e corrente para o resistor: VR = R.I. A equação equivalente para o capacitor

relaciona carga armazenada, capacitância e voltagem: q = C.VC .

Por fim, traduzindo o modelo como uma malha única e aplicando a Lei de Kirchoff das Malhas,

obtemos Vcc − VR − VC = 0 ou R.I + VC = Vcc . Mas a corrente é a derivada, em relação ao tempo, da

dq

quantidade de carga que flui pelo sistema, isto é, I =

. Assim, escrevendo a equação para VC , fazemos

dt

d

dVC

dVC

I=

(C.VC ) = C

e, substituindo, obtem-se RC

+ VC = Vcc e a equação diferencial se torna

dt

dt

dt

dVC

1

Vcc

+

VC =

dt

RC

RC

(1)

que é uma equação diferencial linear de primeira ordem.

R 1

t

Para resolvê-la, multiplicamos ambos os membros pelo fator integrante µ(t) = e RC dt = e RC , obtendo

t

t

dVC (t) t

1

Vcc

.e RC +

VC .e RC =

.e RC

dt

RC

RC

que equivale a

t

t

d Vcc

VC (t).e RC =

.e RC

dt

RC

Integrando ambos os membros em relação à t, obtemos

Z

t

t

Vcc

.e RC dt

VC (t).e RC =

RC

4

ou

h

i

t

t

VC (t) = e− RC . Vcc .e RC + K

ou

t

VC (t) = Vcc + K.e− RC

(2)

Agora, observamos que independente do valor da constante K, lim VC (t) = Vcc , como já se esperava;

t→∞

isto é, para um intervalo de tempo muito grande, a voltagem nos terminais do capacitor se torna igual

à voltagem da fonte que alimenta o circuito.

Adicionando a condição fı́sica inicial VC (0) = 0 encontramos 0 = Vcc + K ou K = −Vcc . Portanto, a

solução da equação (1) é dada por (3).

t

(3)

VC (t) = Vcc 1 − e− RC

2

Como estamos interessados em carregar o capacitor até cerca de Vcc , calculamos T1 de modo

3

T1

T1

T1

2

2

2

que VC (T1 ) = Vcc . Assim VC (T1 ) = Vcc 1 − e− RC ⇒ Vcc = Vcc 1 − e− RC ⇒ = 1 − e− RC ⇒

3

3

3

T1

T1

1

T1

1

= ln ⇒

= ln 3 ⇒ T1 = RC ln 3. Assim:

e− RC = ⇒ −

3

RC

3

RC

T1 ≈ 1, 1RC

(4)

Conclusão: o perı́odo T1 vale aproximadamente 1,1RC. Assim, ao escolhermos um resistor com

R = 10KΩ e um capacitor com C = 100µF , obtemos T1 ≈ 1, 1s.

Uma observação que deve ser feita é que define-se a constante de tempo τ = RC de modo que quando

temos t = τ , o argumento da exponencial na equação (3) torna-se −1, isto é, VC (τ ) = Vcc 1 − e−1 ou

VC (τ ) = 0, 632Vcc . Assim, decorre da definição que τ é o tempo necessário para que o capacitor atinja

2

entre seus terminais 63,2 % da voltagem da fonte que o carrega. Como Vcc = 0, 667Vcc ou 66,7% de

3

2

Vcc , conclui-se que o tempo necessário para o capacitor atingir Vcc nos seus terminais é pouco mais

3

que uma constante de tempo τ .

Com essa nomenclatura, as equações (1), (2), (3) e (4) se tornam

1

Vcc

dVC

+ VC =

dt

τ

τ

(5)

t

3.3

VC (t) = Vcc + K.e− τ

(6)

t

VC (t) = Vcc 1 − e− τ

(7)

T1 ≈ 1, 1τ

(8)

Operação Astável

Para implementar o oscilador astável à partir do 555, é preciso fazer uma ligeira modificação do projeto

anterior. Basicamente, precisaremos de mais um resistor para conectar o pino 7 aos pinos 6 e 2. A função

desse resistor é descarregar o capacitor quando o transistor transmitir o terra ao pino de descarga (7).

O pino de limiar (6) é ligado ao pino disparador (2) para que o processo de descarga do capacitor sirva

Vcc 2

e Vcc .

de disparo para um próximo pulso. Com isso, a voltagem do capacitor oscilará entre

3

3

Vamos chamar o primeiro resistor de R1 e o segundo, o que adicionamos por último, de R2 . A figura

4 ilustra as conexões externas que devem ser feitas para o 555 operar como oscilador astável, segundo

o descrito acima. Como na carga do capacitor, a corrente flui através dos dois resistores, a constante

5

Figura 4: Operação Astável

de tempo na carga do capacitor é τ1 = (R1 + R2 )C. Já durante a descarga do capacitor, a corrente flui

através do resistor R2 somente, de modo que a constante de tempo na descarga do capacitor é τ2 = R2 C.

O modelo da equação de carga e descarga do capacitor é semelhante ao modelo anterior para o

monoestável, alterando apenas alguns parâmetros. Para a carga do capacitor, a equação diferencial é

semelhante à (5), ajustando a constante de tempo para τ1 = (R1 + R2 )C e obtendo (9).

dVC

1

Vcc

+ VC =

dt

τ1

τ1

(9)

A solução geral é dada pela equação (6), ajustando, também, a constante de tempo, obtendo a

equação geral (10).

t

VC (t) = Vcc + K.e− τ1

(10)

Vcc 2

Sendo T1 o perı́odo de carga do capacitor (entre os referidos valores

e Vcc ), onde a saı́da fica

3

3

Vcc

em nı́vel lógico 1, consideramos a condição inicial VC (0) =

. Neste caso, excluı́mos apenas o primeiro

3

perı́odo de execução, já que ao ligar o circuito, o capacitor terá voltagem inicial nula. Obtemos, então,

2

Vcc

= Vcc + K ou K = − Vcc . Substituindo, obtemos a solução dada pela equação (11).

VC (0) =

3

3

t

2

VC (t) = Vcc 1 − e− τ1

(11)

3

2

2

2 − Tτ 1

2

2 T1

2 T1

1

Sendo VC (T1 ) = Vcc , segue que Vcc = Vcc 1 − e 1

⇒

= 1 − e− τ1 ⇒ e− τ1 =

⇒

3

3

3

3

3

3

3

T1

1

T1

1

T1

e− τ 1 = ⇒ −

= ln ⇒

= ln 2 ⇒ T1 = τ1 ln 2

2

τ1

2

τ1

Assim, segue que

T1 ≈ 0, 693(R1 + R2 )C

(12)

2

O modelo de descarga (perı́odo T2 ) é exatamente o oposto: a voltagem inicial é Vc (0) = Vcc e a

3

Vcc

voltagem final é Vc (T2 ) =

. O equação diferencial, agora, não admite uma fonte externa; basta fazer

3

Vcc = 0 e tomar a constante de tempo τ2 , obtendo a equação (13).

6

dVC

1

+ VC = 0

dt

τ2

(13)

Para resolvê-la, escrevemos a equação na forma

dVC

1

= − VC

dt

τ2

o que fornece uma solução geral

t

VC (t) = K.e− τ2

(14)

2

2

Adicionando a condição inicial do problema Vc (0) = Vcc obtemos K = Vcc . Assim, a solução é

3

3

dada pela equação (15).

t

2

Vcc .e− τ2

(15)

3

T2

1

T2

1

T2

⇒ e− τ2 = ⇒ −

= ln ⇒

= ln 2 ⇒ T2 = τ2 ln 2

2

τ2

2

τ2

VC (t) =

Sendo Vc (T2 ) =

e, portanto,

T2

Vcc

2

Vcc

, temos

= Vcc .e− τ2

3

3

3

T2 ≈ 0, 693R2 C

(16)

Agora, podemos definir o perı́odo total do pulso como sendo T = T1 + T2 ou T = τ1 ln 2 + τ2 ln 2 ou

T = (τ1 + τ2 ) ln 2. Desse modo, resulta a equação (17).

T ≈ 0, 693(R1 + 2R2 )C

(17)

Diretamente da equação anterior, podemos encontrar a frequência de oscilação do sinal através da

equação (18).

f=

1, 443

1

≈

T

(R1 + 2R2 )C

(18)

A figura 5 ilustra o comportamento da saı́da em função do tempo, simultaneamente com o processo

de carga e descarga do capacitor.

Figura 5: Saı́da do Oscilador e Voltagem no Capacitor

Por fim, observamos que o perı́odo T1 deve ser, por definição, maior que o perı́odo T2 . Desta forma

pode ser interessante estudar o comportamento da relação entre os dois perı́odos. Chamamos de duty

7

cycle a razão entre o perı́odo T2 e o perı́odo total T . Ela varia de 50 % a 100 %. Da equação (19),

observamos que para R1 << R2 , D ≈ 50%. Já para R1 >> R2 , D ≈ 100%.

D=

T2

R2

=

T

R1 + 2R2

(19)

No nosso projeto, utilizaremos dois resistores com resistências R1 = R2 = 10KΩ e um capacitor

de capacitância C = 100µF . Dessa forma, teremos T1 ≈ 1, 4s, T2 ≈ 0, 7s e T ≈ 2, 1s. Como estamos

interessados apenas no perı́odo de oscilação do sinal (T ), não nos importamos com a distribuição entre

T1 e T2 e o duty cycle.

4

TTL 7490 ou TTL 74LS90

O CI 7490 da famı́lia TTL é entitulado em seu data sheet original como Decade counter, isto é,

trata-se de um contador de década. A figura 6 ilustra a arquitetura interna do CI, constituı́da por quatro

flip-flops (três JK e um SR). As saı́das de contagem são Q3 , Q2 , Q1 e Q0 , do bit mais significativo para

o menos significativo; isto é o número é representado por Q3 Q2 Q1 Q0 .

Figura 6: Arquitetura interna do 7490

O flip-flop correspondente ao bit menos significativo (Q0 ) tem uma entrada de clock denominada

CP0 e este bit é independente dos demais, de modo que o flip-flop correspondente ao segundo bit menos

significativo (Q1 ) apresenta uma entrada de clock denominada CP1 . Trabalhando de forma independente

CP0 exibe em Q0 um contador de módulo 2 e CP1 exibe em Q3 Q2 Q1 um contador de módulo 5, através

dos outros flip-flops. Para montador o contador módulo 10 basta conectar Q0 (pino 12) a CP1 (pino 1)

e utilizar CP0 (pino 14) como entrada de clock.

Figura 7: Representação Lógica e Pinagem do 7490

8

As entradas M R1 e M R2 são controladores de Master Reset e ambos precisam estar em nı́vel lógico

1 para resetar o contador (Q3 Q2 Q1 Q0 = 0000, isto é, 0). As entradas M S1 e M S2 são controladores de

Master Set e ambos precisam estar em nı́vel lógico 1 para setar o contador (Q3 Q2 Q1 Q0 = 1001, isto

é, 9). Ambos os clocks são ativados por transição negativa e todos esses detalhes podem ser observados

na figura 7.

Para simplificar, na figura 6, as entradas J e K estão em nı́vel lógico 1 quando nada for explicitado

(quando elas estiverem em aberto). Além disso, alguns pinos deste chip não são utilizados internamente.

Denotamos seus nomes por NC: Not Connected (Não Conectado). A pinagem completa também

pode ser observada na figura 7.

Para melhor explicar seu funcionamento as tabelas 2 e 3 mostram como as saı́das se exibem em função

das entradas de controle. As entradas com um X são os chamados don’t cares, isto é, podem assumir

qualquer valor, seja nı́vel lógico 0 ou nı́vel lógico 1.

MR1

1

1

X

0

X

0

X

ENTRADAS

MR2 MS1 MS2

1

0

X

1

X

0

X

1

1

X

0

X

0

X

0

X

X

0

0

0

X

Q3

0

0

1

SAÍDAS

Q2 Q1 Q0

0

0

0

0

0

0

0

0

1

CONTAGEM

CONTAGEM

CONTAGEM

CONTAGEM

Tabela 2: Modos de operação do 7490

Q3

0

0

0

0

0

0

0

0

1

1

Q2

0

0

0

0

1

1

1

1

0

0

Q1

0

0

1

1

0

0

1

1

0

0

Q0

0

1

0

1

0

1

0

1

0

1

Valor

0

1

2

3

4

5

6

7

8

9

Tabela 3: Contagem do 7490

5

TTL 7442 ou TTL 74LS42

O CI 7442 da famı́lia TTL é um decodificador BCD para decimal. Ele recebe quatro bits codificados

em BCD (Binary Coded Decimal ) e ativa uma de suas dez saı́das correspondente ao valor decimal (0 a

9). A figura 8 ilustra sua arquitetura interna.

O princı́pio de funcionamento do decodificador é bem simples: as entradas A3 , A2 , A1 e A0 e seus

complementos A3 , A2 , A1 e A0 são combinadas em diversas posições para ativar sempre apenas uma das

dez portas NAND’s (nı́vel lógico 0) que estão conectadas às saı́das do circuito. Isso faz com que todas

as outras saı́das permaneçam inativas (nı́vel lógico 1).

9

Figura 8: Arquitetura interna do 7442

O sı́mbolo lógico deste CI pode ser observado na figura 9, bem como a sua pinagem. As entradas A3 ,

A2 , A1 e A0 representam os quatro bits de entrada BCD, do mais significativo para o menos significativo.

Neste caso, serão as próprias saı́das Q3 , Q2 , Q1 e Q0 do contador, respectivamente.

Os sı́mbolos que se apresentam em todas as dez saı́das do circuito, pequenos cı́rculos entre o chip

e os pinos, são utilizados para indicar que a saı́da é invertida, isto é, a saı́da ativa deve estar em nı́vel

lógico 0, ao passo que a inativa esteja em nı́vel lógico 1.

Figura 9: Representação Lógica e Pinagem do 7442

A tabela 4 ilustra a Tabela Verdade do CI 7442, mostrando qual saı́da está ativa para as dez entradas

diferentes. Os últimos seis casos são inválidos, pois não há código BCD maior que 1001, ou 9. Nesses

casos, todas as saı́das estão inativas (nı́vel lógico 1).

Os valores inválidos não serão utilizados pois este CI será alimentado pelas saı́das do contador de

década. Assim, apenas valores entre 0 e 9 ocorrerão.

10

ENTRADAS

A3 A2 A1 A0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

3

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

SAÍDAS

4 5 6

1 1 1

1 1 1

1 1 1

1 1 1

0 1 1

1 0 1

1 1 0

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

7

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

8

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

9

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

Tabela 4: Tabela Verdade do 7442

6

TTL 7448 ou TTL 74LS48

Assim como o CI 7442, o 7448 também é um decodificador, mas trata-se de um decodificador BCD - 7

segmentos. Ele é usado para decodificar o código em BCD para uma de suas sete saı́das, que representam

os sete filamentos de um display de sete segmentos. A figura 10 ilustra sua arquitetura interna e a figura

11 mostra seu sı́mbolo lógico e seu diagrama de pinos.

Figura 10: Arquitetura interna do 7448

O CI 7448 apresenta uma entrada LT : Lamp Test (pino 3) que força todas as saı́das para nı́vel

lógico 1 se ela estiver em nı́vel lógico 0. Já os pinos 5 e 4, RBI e BI/RBO, respectivamente, são usados

para cascateamento de CI´s. Se RBI = 1, o decodificador opera normalmente. Se RBI = 0 então as

saı́das operam normalmente somente se ele não estiver mostrando o número zero. Se o número a ser

11

exibido for zero, as saı́das são desativadas (quando conectado ao display, ele apaga) e BI/RBO = 0.

A tabela 5 representa a Tabela Verdade de funcionamento desse chip, quando RBI = 1 e LT = 1.

Para os casos em que o número é maior que 9, atribuiu-se alguns sı́mbolos para serem formados no

display. Como esse decodificador será alimentado por um contador de década, isso nunca ocorrerá, pois

apenas valores entre 0 e 9 surgirão nas entradas do decodificador.

Figura 11: Representação Lógica e Pinagem do 7448

As saı́das do decodificador são conectadas aos pinos correspondentes no display de sete segmentos

tipo catodo comum através de um resistor. Assim, quando a saı́da do decodificador está em nı́vel lógico

1, o filamento correspondente no display está aceso.

ENTRADAS

A3 A2 A0 A1

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

a

1

0

1

1

0

1

0

1

1

1

0

0

0

1

0

0

b

1

1

1

1

1

0

0

1

1

1

0

0

1

0

0

0

SAÍDAS

c d e

1 1 1

1 0 0

0 1 1

1 1 0

1 0 0

1 1 0

1 1 1

1 0 0

1 1 1

1 0 0

0 1 1

1 1 0

0 0 0

0 1 0

0 1 1

0 0 0

f

1

0

0

0

1

1

1

0

1

1

0

0

1

1

1

0

g

0

0

1

1

1

1

1

0

1

1

1

1

1

1

1

0

Tabela 5: Tabela Verdade do 7448

6.1

Display de Sete Segmentos

O display de sete segmentos apresenta sete segmentos (a, b, c, d, e, f, g) e um ponto decimal. Ele

é ligado às respectivas saı́das do 7448 através de um resistor. A saı́da alta do decodificador ativa o

filamento correspondente já que o display é do tipo catodo comum (todos os LED’s dos filamentos estão

ligados ao terra pelo catodo). A figura 12 mostra a pinagem e a estrutura deste display. Observe que

dois pinos devem ser conectados ao terra. O pino correspondente ao ponto decimal (pino 5) não será

usado nesta experiência.

12

Figura 12: Display de sete segmentos

7

Circuito Antitrepidação

Um circuito antitrepidação é muito simples de ser feito. Usando um CI TTL 7400 (composto por

quatro portas NAND de 2 entradas cada), montamos o circuito ilustrado abaixo.

Figura 13: Circuito antitrepidação

A chave do lado esquerdo está ligada ao terra e indica que devemos fazer manualmente a conexão

do terra com um pino do NAND superior (4) e depois com um pino do NAND inferior (9). Enquanto

a conexão está em aberto, ambos os pinos ficam polarizados em nı́vel lógico 1. O NAND superior é

responsável por setar a saı́da e o inferior por resetá-la. O circuito funciona como um pequeno flip-flop

SR modificado.

Em ambos os NAND´s a numeração é indicada, mas pode-se usar outros pinos do mesmo CI, conforme

ilustra a figura 14. Não esqueça de conectar o pino 1 ao terra e o pino 14 ao Vcc .

Figura 14: Circuito interno e pinagem do 7400

13

Esta parte do projeto é extremamente dispensável. Ela só é feita para criar um clock manual, que

será conectado ao contador de década. Uma vez verificado que o contador e os decodificadores estão

operando corretamente e o oscilador astável também funciona, a saı́da do oscilador substituirá o clock

manual.

8

Execução

Agora que todos os detalhes foram explicados e todas as demonstrações foram feitas, basta concluir o

projeto unindo todas as partes. A lista à seguir indica a ordem de execução das tarefas. Mãos à obra!

• Monte e teste o oscilador astável como descrito na seção 3

• Se desejar, monte o circuito antitrepidação descrito na seção 7 para utilizá-lo como clock para o

contador

• Monte e teste o contador de década como descrito na seção 4, incluindo LED’s para mostrar o

estado atual do contador

• Monte e teste o decodificador BCD - Decimal como descrito na seção 5, incluindo LED’s para

verificar seu funcionamento

• Monte e teste o decodificador BCD - 7 segmentos como descrito na seção 6, incluindo LED’s para

verificar seu funcionamento

• Conecte a saı́da do oscilador à entrada de clock do contador e verifique o funcionamento do projeto

como um todo

Depois de tudo pronto, troque as resistências e a capacitância do oscilador astável e observe as mudanças que ocorrem. Segundo nossas contas, o perı́odo total de oscilação da saı́da do astável é dado pela

equação (17)

T ≈ 0, 693(R1 + 2R2 )C

e para R1 = R2 = 10KΩ e C = 100µF , obtivemos T ≈ 2, 1s (vide página 7).

Se você utilizar por exemplo capacitores com C = 10µF e C = 1µF , irá diminuir o perı́odo em 10 e

em 100 vezes, respectivamente. Observe o efeito que isso cria.

Para pensar: se você trocar os resistores de resistências R1 = R2 = 10KΩ por R1 = R2 = 100KΩ e

o capacitor de capacitância C = 100µF por C = 10µF ou mesmo se trocar os resistores por R1 = R2 =

1M Ω e o capacitor por C = 1µF , o perı́odo de oscilação se mantém inalterado. O que muda então nessa

situação?

As imagens (15) e (16), mostram, respectivamente, o projeto completo e o resultado que eu obtive ao

realizá-lo em minha protoboard. O projeto não inclui o circuito antitrepidação apresentado na seção 7.

Na foto do meu projeto, o oscilador está no canto superior esquerdo, ligado a um LED para verificar

sua atividade. Ao lado dele está o contador de década, ligado a quatro LED’s que verificam seu estado

atual. No lado direito, encontra-se o decodificador BCD - decimal, que aciona um dos dez LED’s dispostos

no canto inferior direito. No centro da plataforma inferior está o decodificador BCD - 7 segmentos e,

ao seu lado esquerdo, o display de sete segmentos em atividade. Finalmente, no canto inferior esquerdo

está o clock manual, o circuito antitrepidação.

14

15

Figura 15: Projeto Completo

16

Figura 16: Resultado do projeto executado