JOÃO INÁCIO DA SILVA FILHO

IMPLEMENTAÇÃO DE CIRCUITOS

LÓGICOS FUNDAMENTADOS EM

UMA CLASSE DE LÓGICAS

PARACONSISTENTES ANOTADAS

Dissertação apresentada à Escola Politécnica da

Universidade de São Paulo para obtenção do título

de Mestre em Engenharia.

São Paulo

1997

JOÃO INÁCIO DA SILVA FILHO

IMPLEMENTAÇÃO DE CIRCUITOS

LÓGICOS FUNDAMENTADOS EM

UMA CLASSE DE LÓGICAS

PARACONSISTENTES ANOTADAS

Dissertação apresentada à Escola Politécnica da

Universidade de São Paulo para obtenção do título

de Mestre em Engenharia.

Área de Concentração :

Microeletrônica

Orientador : Prof. Dr. Pedro Luís Próspero Sanchez

São Paulo

1997

2

da Silva Filho, João Inácio

Implementação de Circuitos lógicos

Fundamentados em uma classe de

Lógicas Paraconsistentes Anotadas.

São Paulo, 1997.

131 p.

Dissertação (Mestrado) - Escola Politécnica da

Universidade de São Paulo. Departamento de

Engenharia Eletrônica.

1.Circuitos Lógicos 2.Lógica não-Clássica 3.Lógica

Paraconsistente 4. Lógica Paraconsistente Anotada

5.Circuitos CMOS I. Universidade de São Paulo.

Escola Politécnica. Departamento de Engenharia

Eletrônica II.t

3

À minha esposa

Maristela

e aos meus filhos

Mônica e Marcelo

pelo apoio,

dedicação

e incentivo

necessários

à elaboração

deste trabalho.

4

AGRADECIMENTOS

Ao Prof. Doutor Pedro Luís Próspero Sanchez, pelo apoio constante e

orientação valiosa no desenvolvimento deste trabalho.

Ao Prof. Doutor Jair Minoro Abe, pela ajuda, comentários e sugestões na

elaboração deste trabalho.

Ao Prof. Doutor Wilhelmus A. M. Van Noije pelo incentivo e colaboração.

Ao Professor Luiz Carlos Moreira pela dedicação e amizade demonstrada ao

longo destes anos.

Aos amigos do Laboratório de Sistemas Integráveis :

Soraya Rita Mont’Alegre,

José Henrique P. Andrade,

Marcio Toma,

João Navarro

Fábio Luís Romão

Rogério A. Neves Tenório

pela ajuda e sugestões técnicas de grande valia.

5

SUMÁRIO

CAPÍTULO 1 - APRESENTAÇÃO

1.1

Introdução ..............................................................................11

1.2

Objetivos do trabalho............................................................ 12

1.3 Justificativa da elaboração da pesquisa...................................13

1.4 Organização do trabalho...........................................................14

CAPÍTULO 2 - INTRODUÇÃO E NOTA HISTÓRICA

2.1 Introdução................................................................................16

2.2 Nota Histórica ..........................................................................18

CAPÍTULO 3 - APRESENTAÇÃO DA LÓGICA PARACONSISTENTE

3.1 A lógica Paraconsistente.........................................................22

3.2 A Lógica Paraconsistente Anotada Pτ ....................................24

CAPÍTULO 4 - ELABORAÇÃO DAS TABELAS-VERDADES À PARTIR

DA LÓGICA PARACONSISTENTE ANOTADA

4.1- Elaboração das tabelas-verdades...............................................30

4.2- Tabelas-verdades dos Operadores Unários n............................42

4.3- Tabela-verdade do Operador COMPLEMENTO.....................44

4.4- Tabela-verdade da Conjunção- Conectivo AND .....................44

4.5- Tabela-verdade da Disjunção - Conectivo OR.........................45

CAPÍTULO 5 - IMPLEMENTAÇÃO DOS CIRCUITOS DAS PORTAS

LÓGICAS PARACONSISTENTES

5.1 - Implementação dos circuitos lógicos........................................47

5.1.1 - Introdução...................................................................47

6

5.2 - Circuito detetor de nível de tensão .........................................49

5.3 - Circuitos dos Operadores n ...................................................52

5.3.1- Operador i ...................................................................52

5.3.2- Operador j ...................................................................53

5.3.3- Operador k ...................................................................54

5.3.4 - Operador L ...................................................................55

5.3.5- Operador m ..................................................................55

5.3.6- Operador T ..................................................................56

5.4-Circuito do Operador COMPLEMENTO ..................................57

5.5-Circuito do Conectivo AND Paraconsistente...............................60

5.6-Circuito do Conectivo OR Paraconsistente.................................63

5.7-Conclusão.....................................................................................65

CAPÍTULO 6 - EXEMPLO DE APLICAÇÕES DAS PORTAS LÓGICAS

PARACONSISTENTES

6.1 - Introdução..................................................................................66

6.2 - Implementação do circuito MAP ( Módulo Analisador

Paraconsistente)..........................................................................69

6.3 - Implementação do circuito MFP ( Módulo Finalizador

Paraconsistente)..........................................................................81

6.4 - Conclusões.................................................................................82

CAPÍTULO 7 - PROJETO E CONSTRUÇÃO DAS PORTAS LÓGICAS

PARACONSISTENTES

7.1 -introdução..................................................................................84

7.2 - Características Construtivas .....................................................85

7

7.3 - Diagramas dos circuitos definitivos das portas lógicas

paraconsistentes....................................................................... 88

7.4- Layouts dos circuitos das portas lógicas

paraconsistentes.......................................................................98

7.4.1- Circuito do detetor de nível de tensão............................98

7.4.2- Circuito dos Operadores Unários n.................................99

7.4.3-Circuito do Operador COMPLEMENTO.......................107

7.4.4- Circuito da porta lógica AND paraconsistente...............109

7.4.5- Circuito da porta lógica OR paraconsistente..................110

CAPÍTULO 8 - RESULTADOS DAS SIMULAÇÕES DOS CIRCUITOS

DAS PORTAS LÓGICAS PARACONSISTENTES

8.1 -Introdução......................................................................................114

8.2 - Resultados das simulações...........................................................115

8.2.1 - Operadores unários n........................................................117

8.2.2 - Operador COMPLEMENTO...........................................125

8.2.3 - Porta lógica AND paraconsistente....................................126

8.2.4 - Porta lógica OR paraconsistente.......................................130

8.3 - Conclusões..................................................................................135

8.4 - Referências bibliográficas...........................................................137

8

RESUMO

Neste trabalho é apresentada uma nova família de portas lógicas digitais projetadas

para receber e responder a sinais lógicos interpretados a partir da semântica das lógicas

Paraconsistentes Anotadas. As Lógicas Paraconsistentes pertencem ao grupo das chamadas

lógicas não-clássicas e diferem das lógicas convencionais por aceitarem a existência de

sinais contraditórios ou inconsistentes de um modo não trivial.

Nas lógicas paraconsistentes estas contradições ou inconsistências são

convenientemente tratadas, produzindo como resultante o sinal que mais se aproxima do

verdadeiro, dando a este, um certo grau de crença ou valoração.

As portas lógicas e os circuitos aqui apresentados, foram projetados especialmente

para que traduzam em sinais lógicos eletrônicos, os estudos desenvolvidos das lógicas

paraconsistentes: a “ Lógica Paraconsistente Anotada” e a “Lógica Paraconsistente Cn” .

Demonstra-se que os circuitos das portas lógicas paraconsistentes que foram

projetados são plenamente compatíveis a qualquer circuito que utilize a lógica

convencional binária. Portanto, os circuitos implementados com a Lógica Paraconsistente

não têm a pretensão de substituir os circuitos eletrônicos digitais convencionais, mas, a sua

principal aplicabilidade é nos casos em que a lógica binária se torna ineficiente, ou até

mesmo impossível de ser aplicada. A “compatibilidade” da Lógica Paraconsistente com a

lógica convencional binária possibilita o funcionamento em harmonia dos dois sistemas

digitais: o binário e o paraconsistente.

Com base na interpretação teórica da Lógica Paraconsistente Anotada foram

extraídas as tabelas-verdades, possibilitando que fossem implementados os circuitos das

portas lógicas paraconsistentes básicas. Estas portas lógicas primitivas foram denominadas

de: Operadores n, Operador COMPLEMENTO Paraconsistente, Conectivo AND

Paraconsistente e Conectivo OR Paraconsistente.

Utilizando-se as portas lógicas primitivas aqui implementadas é apresentado um

circuito, denominado Módulo Analisador Paraconsistente (MAP), que trata os sinais

paraconsistentes, conforme a proposta teórica básica das Lógicas Paraconsistentes

Anotadas. Este circuito é projetado utilizando-se principalmente das portas lógicas

primitivas.

Com a aplicação dos circuitos das portas lógicas paraconsistentes abrem-se

possibilidades de se projetar circuitos mais complexos, tratando convenientemente as

inconsistências que sempre aparecem em sistemas lógicos digitais.

Todos os circuitos aqui apresentados foram projetados utilizando-se a técnica full

custom para um processo digital CMOS de 1,2 µ m, e as simulações foram feitas para o

funcionamento numa freqüência típica de 50 Mhz.

9

ABSTRACT

In this work a new family of digital logic gate circuits designed to receive and to

answer logic signals based on the Paraconsistent Annotated Logic semantics is presented.

The Paraconsistent logic belongs to the group of the so-called non-classical logic,

which is different from classical logic, because it allows in its structure inconsistent signals

in a non trivial manner.

In Paraconsistent logics the contradiction or inconsistency is treated and results in

one signal very close to the true signal, together with a measurement of the degree of belief

on the result.

The logic gate and circuits presented were especially designed to translate into

electronic logic signals the studies of a the “Paraconsistent Annotated Logic” and

“Paraconsistent Logic Cn”.

The logic gate circuits here presented were quite compatible with any circuit that

uses the usual logic. Therefore, these designed circuits with Paraconsistent logic, do not

intend to substitute the digital electronic circuits, on the contrary, the main application is

where the binary logic is not adequate or even impossible to apply.

By using Annotated Paraconsistent Logic the true-tables were extracted for the

implementation of the circuits of the Paraconsistent logic gates. The primitive

Paraconsistent logic gates were named: Operator n, Operator COMPLEMENT,

Paraconsistent Connective OR and Paraconsistent Connective AND.

One circuit named Paraconsistent Analyzer Module (PAM), was designed with these

basic Paraconsistent logic gates. This module (PAM) deals the signals in agreement with

the proposal of the Annotated Paraconsistent Logic.

Paraconsistent logic circuits have great possibility of use in complex systems to

process inconsistent signals, which are very common in everyday applications.

Every circuit presented was designed with a CMOS 1,2 µ m digital process and the

simulations were made for a typical frequency of 50 MHz.

10

CAPÍTULO 1 - APRESENTAÇÃO

1.1 - INTRODUÇÃO

Nos grandes centros industriais é grande a necessidade dos constantes aumentos da

produção e melhora na qualidade dos produtos manufaturados. As metas de bom

desempenho só são alcançadas através do avanço tecnológico, o que se traduz por meio de

uma crescente automação das máquinas.

Os bons resultados obtidos, face a esta demanda, devem-se em grande parte aos

avanços nas pesquisas e na aplicação da tecnologia que abrange as áreas de Robótica e

Inteligência Artificial.

Portanto, é clara a necessidade cada vez maior que o Brasil entre rapidamente no

processo de incrementar pesquisas nesta área, ou corre o risco de ficar definitivamente fora

desta nova revolução industrial.

11

É de extrema importância direcionar os esforços as pesquisas, tanto nas formas de

aplicação e implementação dos circuitos eletrônicos, como no intuito de se encontrar novos

processos tecnológicos.

A partir destas considerações definiu-se o objetivo deste trabalho, que é justamente

direcionado para pesquisa na área de eletrônica digital.

Os trabalhos prévios para a elaboração desta dissertação foram iniciados a partir do

curso “Introdução às Lógicas não-Clássicas”. Este curso faz parte do currículo para

obtenção dos créditos no programa de Pós-graduação Poli-USP, e como o próprio título

esclarece, aborda os estudos das lógicas não convencionais.

Entre os vários tipos de lógicas não-Clássicas estudadas, encontram-se as “Lógicas

Paraconsistentes”.

A pesquisa das lógicas Paraconsistentes teve até o momento um carácter

estritamente acadêmico, exceções feitas aos estudos da sua aplicabilidade demonstrada na

área de computação pela implementação dos sistemas computacional “Paralog” [18] e

“Paralog_e” [ 33 ]. Sendo assim, o trabalho desta dissertação, ao que se sabe, é o primeiro

que orienta as pesquisas para a sua aplicabilidade em têrmos de hardware.

1.2- OBJETIVOS DO TRABALHO

Estudar a Lógica Paraconsistente e sua aplicabilidade em circuitos eletrônicos

digitais.

Implementar blocos primitivos de Portas lógicas baseadas na Lógica

Paraconsistente Anotada .

Analisar o desempenho e funcionamento das portas lógicas paraconsistentes

utilizando programas computacionais simuladores de circuitos digitais .

Iniciar o desenvolvimento de circuitos eletrônicos e dispositivos específicos que

12

utilizem lógica paraconsistente, permitindo que pesquisas posteriores venham a

resultar em projetos de dispositivos mais complexos.

1.3 - JUSTIFICATIVA DA ELABORAÇÃO DA PESQUISA

Este trabalho se justifica, principalmente, por ser o pioneiro nesta área de lógicas

paraconsistentes. De uma maneira geral se propõe a :

I - Obtenção de significativo avanço nas pesquisas da aplicabilidade das lógicas

paraconsistentes em circuitos digitais, como complemento da lógica binária .

II -Obter blocos lógicos primitivos que respondam as tabelas-verdades

fundamentadas na lógica paraconsistente, abrindo possibilidades de aplicações futuras em

circuitos digitais que requeiram maior complexidade.

III - Expandir a aplicação da lógica paraconsistente em circuitos eletrônicos digitais

demonstrando a vantagem desta aplicação em partes do sistema onde a lógica binária é

inoperante.

IV -Comprovar a aplicabilidade da lógica Paraconsistente em sistemas lógicos

digitais, abrindo caminho para investigações mais amplas, o que concorrerá para um avanço

na tecnologia que trata de Sistemas Lógicos, Robótica e Inteligência Artificial.

13

1.4 - ORGANIZAÇÃO DO TRABALHO

O texto desta dissertação é organizado da seguinte forma:

CAPÍTULO 2 - INTRODUÇÃO E NOTA HISTÓRICA

Este capítulo apresenta uma introdução onde é exposta a origem dos estudos das

lógicas paraconsistentes. Neste capítulo também se descreve históricamente, de modo

resumido, como foi desenvolvida a teoria da Lógica Paraconsistente, bem como uma breve

menção aos cientistas que a idealizaram.

CAPÍTULO 3 -APRESENTAÇÃO DA LÓGICA PARACONSISTENTE .

Neste capítulo é apresentado um resumo das principais equações que moldam a

Lógica Paraconsistente Anotada. É dada uma idéia parcial dos estudos matemáticos que

estruturam a Lógica Paraconsistente Anotada. As equações e a semântica apresentadas

sucintamente neste capítulo são suficientes para se fazer a extração das tabelas-verdades

para implementação das portas lógicas paraconsistentes.

CAPÍTULO 4 - EXTRAÇÃO

DAS

TABELAS-VERDADES

A

PARTIR

DA

LÓGICA

PARACONSISTENTE ANOTADA.

Este capítulo apresenta o método para a obtenção das tabelas-verdades dos blocos

primitivos da Lógica Paraconsistente, utilizando-se das equações e do raciocínio

matemático intuitivo apresentado no capítulo 2. Todas as tabelas-verdades dos principais

blocos lógicos estão expostas neste capítulo.

14

CAPÍTULO 5 - IMPLEMENTAÇÃO DOS CIRCUITOS DAS PORTAS LÓGICAS

PARACONSISTENTES.

Neste capítulo são apresentados todos os diagramas dos circuitos das portas lógicas

primitivas.

As portas lógicas:

Operadores n,

Operador COMPLEMENTO

Paraconsistente, Conectivo AND Paraconsistente e Conectivo OR Paraconsistente têm os

seus funcionamentos descritos.

CAPÍTULO 6 - EXEMPLO DE

APLICAÇÕES

DAS

PORTAS LÓGICAS

PARACONSISTENTES .

Neste capítulo é apresentado um circuito composto por blocos lógicos primitivos

Paraconsistentes implementados no capítulo 5. O circuito projetado é denominado Módulo

Analisador Paraconsistente (MAP), cujo funcionamento obedece a teoria básica da Lógica

Paraconsistente Anotada.

CAPÍTULO 7 - PROJETO

E CONSTRUÇÃO

DAS

PORTAS

LÓGICAS

PARACONSISTENTES.

Este capítulo apresenta os principais aspectos do projeto das portas lógicas

paraconsistentes, mostrando as características construtivas e os layouts obtidos a partir do

detalhamento dos circuitos mostrados no capítulo 5.

CAPÍTULO 8 - RESULTADOS

DAS

SIMULAÇÕES

DOS

CIRCUITOS DAS

PORTAS LÓGICAS PARACONSISTENTES

Os resultados obtidos através de simulações e os layouts das portas lógicas são

apresentados neste capítulo. Os gráficos provenientes das simulações foram obtidos

utilizando o software AIM-SPICE 1.5a.

No final deste capítulo são apresentadas as conclusões finais, onde se discute as

limitações e projeções para futuras pesquisas originadas por este trabalho.

15

CAPÍTULO 2 -

INTRODUÇÃO E NÓTA HISTÓRICA

2.1- INTRODUÇÃO

Os circuitos eletrônicos utilizados em sistemas digitais, funcionam baseados na

lógica binária, desde a época em que foram primeiramente projetados.

As primeiras máquinas eletromecânicas construídas na década de 40, precursoras

dos atuais computadores eletrônicos, já utilizavam o sistema binário porque com apenas

dois símbolos podiam efetuar seus cálculos. Esta particularidade da lógica binária facilita a

sua representação por sinais elétricos.

Com o aparecimento dos dispositivos semicondutores, por volta de 1950, ocorreu

um aumento significativo de projetos de circuitos digitais que utilizam a lógica binária. Este

aumento deve-se principalmente ao fato dos dispositivos semicondutores, utilizados nos

16

circuitos digitais serem facilmente polarizados e transformados em chaves do tipo On-Off .

Estas chaves em determinado momento deixam passar corrente elétrica, e no instante

seguinte podem impedir a passagem da corrente.

Nos sistemas digitais encontramos sinais variáveis que são especiais, porque só

podem assumir dois valores possíveis. Idealmente considera-se que as transições que

ocorrem entre estes dois valores, são tão abruptas, que não existe nenhum outro valor

intermediário. Portanto, as palavras “Falso” (F) e “Verdadeiro” (V) são usadas para definir

estes dois valores.

O sinal verdadeiro é em geral representado por um certo nível de tensão (V1) de

polaridade positiva, e o sinal falso é representado por um nível de tensão (V2) de

polaridade negativa. A lógica que adota esta convenção é chamada de lógica binária

positiva.

A lógica clássica ou lógica convencional elabora o cálculo proposicional utilizandose de valores binários que permitem obter com facilidade as tabelas-verdades do Conectivo

da Negação e dos Conectivos AND e OR das sentenças lógicas [30].

A lógica clássica foi convenientemente tratada e formulada algebricamente,

apresentando resultados satisfatórios, e como é plenamente sabido, isto permitiu a

implementação e elaboração de projetos de sistemas lógicos binários de grande porte e alto

desempenho.

No entanto, há algumas situações onde a lógica clássica não é capaz de tratar

adequadamente os sinais lógicos envolvidos. Uma destas situações relevantes é quando

aparecem sinais conflitantes nas entradas de um circuito lógico. Nestes casos, os circuitos

lógicos que utilizam a lógica binária, ficam impossibilitados de qualquer ação e não podem

ser aplicados.

Um caso muito comum é quando um sinal que é esperado como verdadeiro se

apresenta como falso, criando uma situação de inconsistência nas entradas do circuito. O

circuito binário, que trabalha com apenas dois estados de saída não tem condições de

apresentar uma resposta satisfatória,

optando quase sempre por um desligamento do

sistema, ou travando-o, para em seguida acionar um alarme.

17

Por conseguinte, necessitamos buscar sistemas lógicos em que se permitam

manipular diretamente o conceito de contradição.

A lógica paraconsistente, que admite proposição com valores lógicos contraditórios

como válidos, apresentada nos estudos da “Lógica Paraconsistente Anotada” [14] e na

“Lógica Paraconsistente Cn” [16] é aplicável nestes casos, além de ser plenamente

compatível com a lógica convencional ou binária.

O objetivo central deste trabalho é estudar a aplicabilidade da Lógica

Paraconsistente Anotada e da Lógica Paraconsistente Cn , em questões de teoria dos

circuitos eletrônicos onde justamente ocorram inconsistências em circuitos. Como

resultado, foram obtidos circuitos que tratam das situações de inconsistências. Estes

circuitos funcionam com sinais lógicos que respondem as sinais inconsistentes, conforme

estabelecidos

pelas

Lógicas

Paraconsistentes,

mais

especificamente

as

Lógicas

Paraconsistentes Anotadas.

2.2- NOTA HISTÓRICA

Conforme a classificação dada em [4 ], o estudo geral da Lógica se divide em dois

grandes campos, a saber: a Lógica Dedutiva e a Indutiva. O campo da Lógica Dedutiva

inclui dois tipos de lógicas: as Lógicas Clássicas e as não-Clássicas. O ramo das Lógicas

não-Clássicas por sua vez se divide no grupo das lógicas complementares da Clássica e no

grupo das lógicas rivais ou heterodoxas.

18

As Lógicas Polivalentes (multivaloradas), as Lógicas Difusas (Fuzzy) e as Lógicas

Paraconsistentes, pertencem ao grupo das lógicas rivais ou heterodoxas, e estão atualmente

sendo objetos de grande interesse nos principais centros de pesquisas [ 27 ].

O principal objetivo nestas pesquisas é a aplicação de uma lógica que difere em

muitos aspectos da lógica convencional. Em alguns casos, procura-se uma lógica que seja

aplicável naquelas áreas onde a lógica clássica não se apresenta de modo eficiente, e até

mesmo em áreas onde a lógica convencional seja impossibilitada de ser aplicada por ser

uma lógica binária.

As Lógicas Paraconsistentes têm atraído a atenção de um número crescente de

pesquisadores com o objetivo de equacionar suas sintaxes e semânticas. Como resultado,

vários trabalhos de carácter teóricos sobre as lógicas paraconsistentes foram publicados

conforme atesta as referências bibliográficas no final deste trabalho.

As Lógicas Paraconsistentes têm como característica principal a aceitação de

proposições conflitantes ou contraditórios. Portanto, um sinal lógico pode ser admitido

como verdadeiro apesar de se apresentar como falso. Quando o circuito receber dois sinais

logicamente diferentes, onde deveriam ser iguais, deve-se analisar suas anotações e tomar

uma decisão, estabelecendo-se qual é o valor lógico do sinal verdadeiro evitando a

paralização do sistema.

Esta análise é feita basicamente através de consultas a outras fontes, para que

se verifique a veracidade das informações, apresentando como resultado um sinal que

expresse a situação verdadeira acompanhado com um certo grau de crença simbolizado por

anotações.

A aplicabilidade prática da lógica paraconsistente resulta numa análise profunda no

ponto de vista da engenharia eletrônica no que tange a vários fatores, como: potência

dissipada do circuito, área útil e dimensões do circuito integrado (CI), juntamente com a

potenciabilidade de aplicações em sistemas eletrônicos digitais.

Dentro da família das Lógicas Paraconsistentes temos dois importantes estudos. São

os “Sistemas Cn , 1 ≤ n <

ω”,

introduzidos por da Costa [15] e as “Lógicas Anotadas

Paraconsistentes” [ 6 ], estudadas principalmente por da Costa, Subrahmanian, Abe, Vago

19

e outros. Os projetos dos circuitos das portas lógicas paraconsistentes, são originados dos

resultados apresentados principalmente nestes dois trabalhos.

Os precursores do estudo da Lógica Paraconsistente foram :

Nikolaj A. Vasil’év, nascido na Rússia em 1860 e Jan Lukasiewics, nascido na

Polônia em 1878 .

Independentemente, os dois publicaram em 1910 trabalhos aos quais tratavam da

possibilidade de uma lógica que não eliminasse, ab initio, as contradições. No entanto estes

estudos, no que se refere à paraconsistência, se restringiram à lógica aristotélica tradicional .

Em 1948 e 1954 o lógico polonês S.Jàskowski (1906-1963) e o brasileiro Newton

C.A.da Costa (1929-

), respectivamente, embora independentemente, edificaram a

Lógica Paraconsistente.

S.Jàskowski formalizou um cálculo proposicional paraconsistente denominado

Cálculo Proposicional Discursivo.

O lógico brasileiro Newton C. A. da Costa desenvolveu vários sistemas

paraconsistentes contendo todos os níveis lógicos usuais: cálculo proposicional , cálculo de

predicados, cálculo de predicados com igualdade, cálculo de descrições e linguagem de

ordem superior ( na forma de teoria dos conjuntos). Referências para esta parte são [16

] e [17 ].

Em 1976 o filósofo peruano Francisco Miró Quesada introduziu o nome

Paraconsistente a estes estudos, sendo rapidamente adotado pela comunidade científica

mundial.

Em 1992 o lógico brasileiro J. M. Abe apresentou na Universidade de São Paulo

um estudo aprofundado com resultados relevantes da lógica paraconsistente anotada Qτ ,

com a tese “Fundamentos da Lógica Anotada” [1 ].

Em 1996 é apresentado por B. C. Ávila uma aplicação da Lógica Paraconsistente em

sistemas de Frames com a implementação de um raciocinador de herança denominado

Paralog_e [8].

Também em 1996,

J.P.Almeida Prado implementou uma arquitetura para

Inteligência Artificial Distribuída baseada em Lógica Paraconsistente Anotada [33].

20

Como pode ser verificado nas referências bibliográficas no final deste trabalho,

existem inúmeras publicações de âmbito internacional envolvendo resultados de pesquisas

em Lógica Paraconsistente, demonstrando que hoje em dia este é um tema de pesquisa

corrente entre muitos investigadores de renome mundial.

Devido ao significativo crescimento da importância desses estudos, em meados de

1997 vai acontecer o primeiro congresso mundial sobre Lógica Paraconsistente na

Universidade de Ghent, na Bélgica.

Neste congresso serão apresentados os mais recentes resultados de diversas

pesquisas desenvolvidas na área da Lógica Paraconsistente, inclusive os resultados do

presente trabalho [21] e [22].

21

CAPÍTULO 3 - APRESENTAÇÃO DA LÓGICA PARACONSISTENTE

3.1- A LÓGICA PARACONSISTENTE

Neste capítulo apresenta-se um resumo da linguagem formal que compõe a Lógica

Proposicional Paraconsistente Anotada (Pτ ). A teoria aqui apresentada, de forma sucinta

contém as principais definições, e é suficiente para a elaboração das tabelas-verdades dos

blocos lógicos primitivos paraconsistentes. Em [1] é feito um amplo estudo destas lógicas

onde o autor demonstrou teoremas de correção e completeza para os cálculos Qτ

(lógicamente de primeira ordem), e é utilizado como principal referência para as notações e

convenções utilizadas neste trabalho.

Como o trabalho está fortemente baseado no conceito de paraconsistência é

conveniente a apresentação de algumas considerações sobre estas lógicas.

Comecemos com as seguintes definições: seja T uma teoria fundada sobre uma

lógica L , e suponha-se que a linguagem de L e T contenha um símbolo para a negação (se

houver mais de uma negação, uma delas deve ser escolhida, pelas suas características

22

matemáticas ). A teoria T diz-se inconsistente se ela possuir teoremas contraditórios, i.e.,

tais, que uma é a negação da outra; caso contrário, T diz-se consistente . A teoria T diz-se

trivial se todas as fórmulas de L ( ou todas as fórmulas fechadas de L ) forem teoremas de

T; em hipótese contrária, T chama-se não trivial.

As seguintes definições são importantes para o entendimento da proposta

apresentada neste trabalho. São elas :

Uma lógica L chama-se Paraconsistente se puder servir de base para teorias

inconsistentes mas não-triviais [16].

Uma lógica L é chamada de Paracompleta se ela puder ser a lógica subjacente a

teorias nas quais se infringe a lei do terceiro excluído na seguinte forma: de duas

proposições contraditórias, uma delas é verdadeira.

De modo preciso, uma lógica se diz paracompleta se nela existirem teorias nãotriviais maximais às quais não pertencem uma dada fórmula e sua negação.

Finalmente, uma lógica L denomina-se Não-Alética se L for Paraconsistente e

Paracompleta.

Verifica-se que, a não adequação da Lógica Clássica ao tratamento das

inconsistências deve-se ao fato de que na Lógica Clássica, se T é uma axiomatização de

uma teoria inconsistente, então toda a fórmula F da linguagem subjacente a tal teoria é uma

consequência lógica de T.

É facilmente demonstrável que a presença de uma contradição na Lógica Clássica,

trivializa qualquer teoria baseada na lógica clássica. Por conseguinte, a Lógica Clássica é

impotente para manipular diretamente o conceito de inconsistência, não podendo fazer um

tratamento não trivial na presença de contradições

No entanto, a inconsistência, que se pode apresentar como a discordância entre duas

propostas, é de extrema importância, porque pode trazer informações que não podem ser

desprezadas [33]. A existência da inconsistência é que induz ao sistema buscar novas

informações ou evidências, por exemplo, consultar outros informantes, resultando numa

conclusão mais adequada.

A busca de novas evidências até que as dúvidas causadas pela inconsistência sejam

diluídas transforma o sinal resultante em um sinal extremamente confiável.

23

Baseados nos conceitos das definições apresentadas, fica claro que os circuitos

eletrônicos digitais, funcionando com base na Lógica Paraconsistente Anotada, melhoram a

precisão nas respostas, evitando por exemplo erros ou paralisação de suas atividades,

causados pelo aparecimento de sinais inconsistentes ou contraditórios .

Portanto, a aplicação da lógica paraconsistente tem como objetivo principal, a

melhora no desempenho de circuitos lógicos utilizados em várias áreas da engenharia

eletrônica, principalmente sistemas digitais de Inteligência Artificial, onde é comum se

deparar em situações em que dois sinais de valores lógicos distintos são verdadeiros, mas

não se tem certeza no que se refere às conclusões que deverão ser tomadas pelo circuito.

Em [ 11 ] são apresentados vários exemplos de aparecimento de sinais contraditórios nesta

área.

3.2- A LÓGICA PARACONSISTENTE ANOTADA Pτ

Em [ 1 ] é feito um estudo aprofundado com demonstrações exaustivas, onde se tem

um apanhado geral sobre a Lógica Paraconsistente Anotada, inclusive com muitos

exemplos ilustrativos de inconsistências em vários campos, principalmente na área da

Ciência da Computação.

Nesta seção é apresentado um resumo da linguagem e o vocabulário que compõem a

Lógica Proposicional Paraconsistente Anotada (Pτ ) com base na referência acima.

Esta apresentação de forma sucinta, com as principais definições é suficiente para

ser utilizada na elaboração das tabelas-verdades dos blocos lógicos primitivos. Para um

estudo mais completo, ver referência [1] já citada.

Inicialmente, fixamos um reticulado finito denominado de reticulado de valoresverdade, τ = < | τ | , ≤ > . Como se sabe, τ é um reticulado se :

1.

∀x ,

2.

Se x ≤ y

x≤x

(reflexividade).

e y ≤ x ⇒ x = y ( anti-simetria).

24

e y ≤ z ⇒ x ≤ z ( transitividade ).

3.

Se x ≤ y

4.

∀ x , y ∈ |τ | , existe o supremo de x e y que denotamos por x

5.

∀x , y ∈ |τ | , existe o ínfimo de x e y que denotamos por x ∧ y .

y.

Associamos a este reticulado os seguintes símbolos :

,

que indica o mínimo de τ ;

,

que indica o máximo de τ .

A representação de um reticulado finito se faz usualmente através do diagrama de

Hasse [ 2 ]; por exemplo :

= inconsistente

0 = Falso

1= verdadeiro

= desconhecido

Figura 3.1 - Reticulado finito “quatro”.

Fixamos, também, um operador :

~ : |τ | → |τ |

que terá, intuitivamente o “significado” da negação da lógica Pτ .

No exemplo anterior ele define-se como :

25

~(1)= 0

~(0)= 1

~(T)=T

~ (⊥ ) = ⊥

A linguagem de Pτ é composta do seguinte vocabulário :

1) Variáveis proposicionais: p1 , p2 , p3 , ... , pn ,...

2) Conectivos lógicos:

( Negação)

∧ ( Conjunção ou “E” )

∨ ( disjunção ou “OU” )

→ ( Implicação )

3) Constantes anotacionais: θ , λ , µ ,... (elementos do reticulado τ ).

4) Símbolos auxiliares : ( , ) .

As fórmulas de Pτ são definidas pela seguinte definição indutiva generalizada:

1- Se p é uma variável proposicional e λ é uma constante anotacional, então p λ

26

é uma fórmula (atômica).

2- Se A é uma fórmula então

A é uma fórmula .

3- Se A e B são fórmulas, então A ∧ B ,

A ∨ B e A → B são fórmulas.

4 - Uma expressão é uma fórmula se e somente se for obtida pela aplicação de uma

das cláusulas 1 , 2 , ou 3 acima.

A fómula

A é lida como “A negação de A”.

A fómula A ∧ B é lida como “A conjunção de A e B ”.

A fómula A ∨ B é lida como “A disjunção de A e B ”.

A fómula A →B é lida como “A implicação de B por A”.

Intuitivamente uma fórmula atômica

pµ

é lida como: “creio na proposição p

com grau de Crença de no máximo µ , ou até µ ( ≤ µ ).

Se p é uma letra proposicional e µ ∈ |τ |, então uma fórmula atômica do

tipo

k

p µ onde , k ≥ 0, denomina-se hiper-literal ( ou simplesmente literal ). As demais

fórmulas denominam-se fórmulas complexas.

O estudo da semântica das lógicas Pτ é apresentado de modo resumido da seguinte

forma:

Interpretação

Uma interpretação relativa às lógicas Anotadas Pτ é uma função I: P → |τ |

(onde P é o conjunto das variáveis proposicionais).

27

A cada interpretação I, associamos uma valoração, V I : F →{ 0 ,1 }, onde F é o

conjunto de todas as fórmulas.

A valoração V I é definida indutivamente por:

1) Se p é uma letra proposicional, então:

⇔ I (p) ≥ µ

VI ( p µ ) = 1

VI ( p µ )

VI (

k

⇔ I (p ) ≥ µ

=0

p µ ) = VI (

k -1

p~ µ ) onde , k ≥ 1

2) Se A e B são fórmulas quaisquer, então:

VI (A →B) = 1 se e somente se VI (A) = 0 ou VI (B) = 1

VI (A ∧ B ) = 1 se e somente se VI (A) = 1

VI (A ∨ B ) = 1 se e somente se

e VI (B) = 1

VI (A) = 1 ou

VI (B) = 1

Definições

Uma interpretação relativa a Pτ ,

p ∈ P

e

µ ∈|τ |

I : P → | τ | se diz inconsistente se existir

tal que:

VI (p µ ) = 1 = VI (

Uma interpretação relativa a Pτ , I : P → | τ |: se diz

p ∈ P e µ ∈ |τ |

tal que:

VI (p µ ) = 0

28

pµ)

não-trivial se existir

Uma interpretação relativa a Pτ , I :

P → | τ |: se diz paraconsistente se for

inconsistente e não-trivial.

A lógica Pτ se diz Paraconsistente se ela admitir uma interpretação paraconsistente.

A Lógica Paraconsistente apresenta nas suas valorações as características de uma

Lógica de Multivalores. Portanto, de acordo com os estudos apresentados por Rosser

&Turquette[38],

fica demonstrado que uma lógica multivalorada é funcionalmente completa

se existirem as funções unárias definidas como:

R

se x = k

0

se x = k

Jk (x) =

Onde: R é o valor distinguido.

29

CAPÍTULO 4 -ELABORAÇÃO DAS TABELAS-VERDADES A

PARTIR DA LÓGICA PARACONSISTENTE

ANOTADA

4.1- ELABORAÇÃO DAS TABELAS-VERDADES

As Lógicas Anotadas são lógicas paraconsistentes, e em geral paracompletas e nãoaléticas.

A partir da teoria das Lógicas Paraconsistentes Anotadas apresentada de modo

sucinto no capítulo 3, é feita a extração das tabelas-verdades, possibilitando assim, a

elaboração dos circuitos das principais funções lógicas paraconsistentes.

Um reticulado de Hasse como o proposto por Anand, Subrahmanian e Flog [6] é

apresentado conforme se segue:

Seja um reticulado finito τ = <|τ |, ≤ >, onde :

|τ |= { ⊥ ,t , f, lt, lf ,T}.

reticulado representam :

⊥

⇒

Indefinido

t

⇒

Verdadeiro

f

⇒

Falso

30

As constantes anotacionais do

lt

⇒

Quase - verdadeiro

lf

⇒

Quase - falso

T ⇒

Sobre-definido

Em uma lógica de 6 anotações,

pode ser visto de forma intuitiva como

inconsistente. A ordem ≤ subjacente é representada pelo diagrama de Hasse [6] conforme

figura a seguir:

Figura 4.1 - Diagrama de Hasse - reticulado “seis”.

~ : |τ | → |τ | ;

Considera-se, também, um operador unitário

segue pode ser imediatamente adaptada a um reticulado finito arbitrário.

O operador

~ : |τ | → |τ |

define-se como:

~(

~(

t ) = f ;

f ) = t

~ ( lf )

;

= lt ;

~ ( lt ) =

31

lf ;

a exposição que se

~(

~

⊥ ) =⊥

;

(T) = T

; onde o símbolo

~

tem o

significado de negação, como já se observou.

Em [ 43 ] as anotações são interpretadas como evidências. As evidências possuem

um papel importante na tomada de decisão quando o circuito recebe informações

contraditórias. Em um circuito de Inteligência Artificial, por exemplo, deve-se levar em

conta todas as possibilidades ou evidências antes de se tomar uma decisão.

No raciocínio evidêncial dois valores são associados a uma anotação do reticulado.

O primeiro valor representa a evidência favorável à proposição p, e o outro a evidência

contrária à proposição p.

A definição para as anotações e para o operador

Se p é uma fórmula básica e o operador

~ [( µ 1 , µ 2 )] = ( µ 2 , µ 1 )

~

é apresentada a seguir.

~ : |τ | → |τ | é definido como:

onde,

µ 1 , µ 2 ∈ { x ∈ ℜ | 0 ≤ x ≤ 1}, considera-se [ µ 1 , µ 2 ] como

uma anotação de p .

As coordenadas µ 1 e µ 2 podem ser lidas como “o grau de crença atribuído a p ”

e o “grau de descrença atribuído a p ”, respectivamente.

Neste trabalho, para melhor facilidade de manipulação dos sinais lógicos,

envolvidos nos circuitos eletrônicos, optou-se pela utilização de anotação de “uma”

coordenada.

Portanto, a anotação atribuída à proposição é composta por um único

elemento µ . Este elemento representará o grau de crença que será atribuído à proposição.

Com isto, o grau de descrença ficará subentendido como sendo o complemento do

grau de crença.

O circuito eletrônico reconhecerá o sinal da valoração da fórmula proposicional

como “verdadeiro” ou “falso” pela análise do sinal lógico do grau de crença, da seguinte

forma :

p (0) ⇒ O sinal da valoração da fórmula proposicional é Falso.

32

p(1/4) ⇒ O sinal da valoração da fórmula proposicional é Quase-falso .

p(1/2) ⇒ O sinal da valoração da fórmula proposicional é Indeterminado .

p(3/4) ⇒ O sinal da valoração da fórmula proposicional é Quase-verdadeiro.

p(1) ⇒ O sinal da valoração da fórmula proposicional é Verdadeiro.

p ( ) ⇒ O sinal da valoração da fórmula proposicional é Inconsistente

Nos limites, a valoração da fórmula proposicional é verdadeira, se o grau de crença

atribuída à proposição p for de valor “1”.

Por outro lado, a valoração da fórmula

proposicional é falsa, se o grau de crença atribuída à proposição p for de valor “0”.

Contudo, na prática, pode-se considerar o caso em que o circuito eletrônico analisa

apenas a anotação, e como resultado atribui-se um valor lógico à fórmula proposicional, da

seguinte forma :

Anotação

valoração da fórmula proposicional

0

sinal lógico

0

1/4

sinal lógico

1/4

1/2

sinal lógico

indeterminado

3/4

sinal lógico

3/4

1

sinal lógico

1

sinal lógico

inconsistente

A anotação ou grau de crença apresenta valores entre 0 e 1, portanto, aos valores

lógicos maiores que 1/2, se atribuirá uma conotação de “verdade” à valoração da fórmula

proposicional, e aos valores lógicos menores que 1/2 se atribuirá uma conotação de

“falsidade”.

Para que seja efetuada uma negação no sinal da valoração da fórmula proposicional,

basta fazer o complemento usual da anotação, ou seja, subtraído de 1.

33

Considerando-se o que foi exposto até agora, trataremos o valor lógico

paraconsistente sendo modelado por ( p , v ), onde :

p

⇒ proposição atômica

v

⇒ anotação ou grau de crença

Denominamos de valor lógico paraconsistente o sinal constituído do par ( p , v ),

que será interpretado pelo circuito eletrônico conforme determinadas características

elétricas.

Para elaboração das tabelas-verdades vamos utilizar semânticas paraconsistentes

denominadas de semânticas de maximização.

Nestas semânticas de maximização, a proposição p será verdadeira se o valor

máximo que o grau de crença v confere a p é 1. A negação de p será verdadeira se o

valor mínimo de p em v for 0.

Tratando a proposição e os graus de credibilidade que lhe são atribuídos como

sinais lógicos teremos a seguinte equivalência:

Proposição

p ⇒ verdadeiro = 1

p ⇒ falso

=0

anotação v

0 ≤ grau de crença

≤1

grau de descrença = 1 - grau de crença

A utilização de uma única anotação facilita a manipulação dos sinais lógicos pelo

circuito. Sendo assim, considera-se neste projeto a anotação atribuída à proposição

composta de um único elemento µ 1 .

O reticulado finito, proposto na figura 4.1, pode ser agora representado da seguinte

forma :

34

Figura 4.2 - Diagrama de Hasse - reticulado “seis” com valores lógicos paraconsistentes.

O reticulado com os valores lógicos paraconsistentes obedece a definição do diagrama de

Hasse, porque:

10 - O valor paraconsistente sobredefinido (

) representado como

anotação máxima, é um valor inconsistente, e intuitivamente é equivalente a um valor

maior que 1.

20 - O valor paraconsistente indefinido ( p, 1/2 ), representado como

anotação mínima, pode ser considerado ( 0 , 0 ).

Estas duas observações satisfazem plenamente a definição do diagrama de Hasse.

Os valores paraconsistentes do reticulado, também, satisfazem a negação porque:

~ (t)

= f

A negação de verdadeiro é falso.

Do reticulado com os valores lógicos paraconsistentes teremos:

~ (p,1)

35

= (p,0)

Considerando-se uma “identificação” da valoração da fórmula proposicional com a

proposição, pode-se afirmar que:

uma proposição de valor p com uma anotação de valor 1, é a negação de uma proposição

de valor p com uma anotação de valor 0.

~ (1,1)

= (1,0)

Podemos afirmar que:

uma proposição de valor “1” com 100% de crença (Verdade), é a negação de uma

proposição de valor “1” com 0% de crença (Falso).

A negação de falso é verdadeiro.

~ (1,0)

= (1,1)

Podemos afirmar que:

uma proposição de valor “1” com 0% de crença (falso), é a negação de uma proposição

de valor “1” com 100% de crença (verdadeiro).

~ ( lf ) = lt

A negação de quase-falso é quase-verdadeiro.

Do reticulado, com os valores lógicos paraconsistentes teremos:

~ (p,1/4)

uma proposição de valor “1” com

valor “1” com

= (p,3/4)

25% de crença, é a negação de uma proposição de

75% de crença, porque equivale a uma proposição “0”com 25% de

crença.

~ ( lt )

= lf

A negação de quase-verdadeiro é quase-falso .

Do reticulado, com os valores lógicos paraconsistentes teremos:

~ (p,3/4)

uma proposição de valor “1” com

= (p,1/4)

75% de crença, é a negação de uma proposição de

valor “1” com 25% de crença, porque esta equivale a uma proposição “0” com 75% de

crença.

~ (⊥ ) = ⊥

A negação de indefinido é indefinido.

Do reticulado, com os valores lógicos paraconsistentes teremos:

36

~ (p,1/2)

= (p,1/2)

Utilizando-se o mesmo processo de inversão das anotações pode-se afirmar que:

uma proposição de valor “0” com 50% de crença, é a negação de uma proposição de valor

“0” com 50% de crença.

~ (0,1/2)

= (0,1/2)

Neste caso, não se verifica mudanças no sinal lógico paraconsistente, tanto o valor

da proposição como o valores das anotações permanecem inalterados. Como a suas

anotações valem 1/2, tratam-se de sinais indefinidos, portanto, pode-se concluir que:

uma proposição de valor “0” com 50% de crença, equivale a uma proposição de valor

“1” com 50% de crença, satisfazendo a definição.

~ ( T) =T

A negação de sobre-definido é sobre-definido:

Como tratam-se de valores inconsistentes, as duas afirmações são verdadeiras. Isto

é: um valor “1” com grau de crença sobre-definido, é a negação de um valor “1” com

grau de crença sobre-definido.

Com isso é satisfeita a definição.

Neste modelo de reticulado pode-se acrescentar infinitas anotações. O acréscimo

destas anotações será limitado por condições físicas de projetos. Como exemplo, são

acrescentadas mais duas constantes anotacionais ao diagrama de Hasse as quais

denominamos:

llf → quase-quase falso

llt → quase-quase verdadeiro

Com a inclusão destas duas novas constantes anotacionais ao reticulado, o conjunto passa a

ser:

|τ | = { ⊥ ,t , f, lt, lf, llt, llf , }.

Cada constante anotacional tem agora as seguintes denominações :

⊥ ⇒

Indefinido

t

⇒

Verdadeiro

f

⇒

Falso

37

lt ⇒

Quase-verdadeiro

lf ⇒

Quase-falso

llt ⇒

Quase-quase verdadeiro

llf ⇒

Quase-quase falso

T

⇒

Sobre-definido ou inconsistente

O diagrama de Hasse com as novas contantes anotacionais fica da seguinte forma:

Figura 4.3 - Diagrama de Hasse - reticulado 8 .

O diagrama de Hasse da figura 4.3, com os respectivos valores paraconsistentes que

representam as constantes anotacionais, é apresentado na figura a seguir:

38

Figura 4.4 - Diagrama de Hasse - reticulado 8 -com valores lógicos paraconsistentes.

No diagrama de Hasse da figura 4.4, pelo “lado direito” temos os valores

paraconsistentes de proposição “falso”, portanto , representado pelo valor “0”. Pelo “lado

esquerdo” temos os valores paraconsistentes de proposição “verdadeiro”, representado pelo

valor “1”.

Verifica-se que o valor da anotação ou grau de crença, varia de um valor máximo de

1 até um valor mínimo de 1/2, pelo “lado esquerdo” (verdade), e pelo “lado direito” (falso)

os valores são o complemento.

Podem-se incluir N (infinitos) valores anotacionais diminuindo-se os intervalos

entre as valorações. O número N somente é limitado por características construtivas das

portas lógicas paraconsistentes.

No reticulado da figura 4.4 são definidos os valores paraconsistentes que expressam

equivalências como :

( 0 , 0 ) ≅ ( 1, 0 )

( 0 , 1/4 ) ≅ ( 1, 3/4 )

( 0 , 1/2 ) ≅ ( 1, 1/2 )

39

( 0 , 3/4 ) ≅ ( 1, 1/4 )

(1,0) ≅ (0,0)

( 1 , 1/4 ) ≅ ( 0 , 3/4 )

( 1 , 1/2 ) ≅ ( 0 , 1/2 )

( 1 , 3/4 ) ≅ ( 0 , 1/4 )

Com base no que foi proposto até agora e relacionando os valores das constantes

anotacionais com os valores paraconsistentes modelo ( p , v ), representados no reticulado

do diagrama de Hasse, podem-se enunciar as seguintes afirmativas :

1 - A valoração da fórmula proposicional representa-se por um valor

binário.

2 - A anotação ou grau de crença é um valor contido no intervalo

real fechado [ 0 , 1 ].

3 - A indeterminação na anotação (1/2) não define qual é o valor lógico

da fórmula proposicional.

4 - Dois valores iguais de fórmula proposicional que tem anotações

complementares são contraditórios (inconsistentes).

5 - Todas as vêzes que ocorrer inconsistência a anotação ou grau

de crença, atribui um valor resultante sobredefinido à fórmula proposicional.

6 - Uma complementação no sinal da anotação acarretará uma inversão

no sinal lógico da fórmula proposicional .

Outro meio de representar os valores lógicos paraconsistentes é através de um

diagrama, conforme a figura a seguir :

40

Figura 4.5 - Diagrama com valores lógicos paraconsistentes de anotação unitária.

Comparando-se dois sinais paraconsistentes originados de fontes distintas, teremos

4 situações de inconsistência. Este conflito de informação aparece quando os sinais se

apresentarem como :

1) Sinal 1 = (p, 0)

Sinal 2 = (p, 1)

2) Sinal 1 = (p, 1/4)

Sinal 2 = (p, 3/4)

3) Sinal 1 = (p, 1)

Sinal 2 = (p, 0)

4) Sinal 1 = (p, 3/4)

Sinal 2 = (p, 1/4)

41

A relação das constantes anotacionais da Lógica Paraconsistente Anotada com os

valores lógicos paraconsistentes obtidos através do modelo ( p,v ), nos permite a elaboração

das tabelas-verdades necessárias à implementação dos circuitos das portas lógicas

paraconsistentes.

A partir das propostas apresentadas, foram construídas as tabelas-verdades dos

Operadores n, Operador COMPLEMENTO e dos Conectivos AND ( ∧ ) e OR ( ∨ ).

4.2 -TABELAS-VERDADES DOS OPERADORES UNÁRIOS

n

Para os Operadores n as tabelas-verdades podem ser elaboradas a partir das

equações de Rosser-Turquette, apresentadas no capítulo 3, onde fica demonstrado que uma

lógica multivalorada subjacente é funcionalmente completa se satisfizer às funções unárias

definidas como:

R

se x = k

0

se x = k

Jk (x) =

Onde: R é o valor distinguido.

A saída será o valor destinguido “1” para um único valor paraconsistente aplicado

na entrada do circuito. Para todos os outros valores paraconsistentes aplicados na entrada a

saída do circuito será zero.

Quando uma entrada de valor lógico “0” apresenta na saída o valor distinguido “1”,

o circuito é denominado de Operador i.

Quando uma entrada de valor lógico “1/4” apresenta na saída o valor distinguido

“1”, o circuito é denominado de Operador j.

Quando uma entrada de valor lógico “1/2” apresenta na saída o valor distinguido

“1”, o circuito é denominado de Operador K.

Quando uma entrada de valor lógico “3/4” apresenta na saída o valor distinguido

“1”, o circuito é denominado de Operador L.

Quando uma entrada de valor lógico “1” apresenta na saída o valor distinguido “1”

o circuito é denominado de Operador m.

42

Quando uma entrada de valor lógico “T” apresenta na saída o valor distinguido “1”,

o circuito é denominado de Operador T.

Na figura 4.6 são apresentadas 6 tabelas-verdades relativas aos Operadores n

relacionados com o reticulado da figura 4.3. Os circuitos dos Operadores n são

implementados a partir destas tabelas.

Entrada

Operador k

Operador j

Operador i

Saída

Entrada

Saída

Entrada

Saída

0

1

0

0

0

0

1/4

0

1/4

1

1/4

0

1/2

0

1/2

0

1/2

0

3/4

0

3/4

0

3/4

1

1

0

1

0

1

0

0

0

Operador m

Operador T

0

Operador L

Entrada

Saída

Entrada

Saída

Entrada

Saída

0

0

0

0

0

0

1/4

0

1/4

0

1/4

0

1/2

1

1/2

0

1/2

0

3/4

0

3/4

0

3/4

0

1

0

1

1

1

0

0

0

1

Figura 4.6 - Tabelas-verdades dos Operadores unários n.

4.3 - TABELA-VERDADE DO OPERADOR COMPLEMENTO

Na figura 4.7 é apresentada a tabela-verdade do Operador COMPLEMENTO.

Como foi visto, quando se faz o complemento das anotações, se obtém uma inversão no

valor lógico da proposição.

43

O circuito do Operador COMPLEMENTO é implementado a partir desta tabela.

Saída

Entrada

0

1

1/4

3/4

1/2

1/2

3/4

1/4

1

0

Figura 4.7 - Tabela-verdade do Operador COMPLEMENTO.

4.4 -TABELA-VERDADE DA CONJUNÇÃO - CONECTIVO AND

No capítulo 3, onde é apresentado um resumo do estudo da Lógica Paraconsistente

Anotada de primeira ordem, o Conectivo AND se apresenta conforme a condição :

VI (A ∧ B) = 1 se e somente se VI (A) = 1 e VI (B) = 1

A partir desta condição (que é clássica), elaborada-se a tabela-verdade do Conectivo

AND.

Verifica-se que o sinal lógico de saída é sempre o menor sinal entre os que estão nas

entradas. A tabela-verdade do Conectivo AND é apresentada na figura 4.8.

44

Figura 4.8 - Tabela-verdade do Conectivo AND .

4.5 -TABELA-VERDADE DA DISJUNÇÃO - CONECTIVO OR

O Conectivo OR é caracterizado pela condição:

VI (A ∨ B) = 1 se e somente se VI (A) = 1 ou VI (B) = 1

45

Estas equação possibilita a elaboração da tabela-verdade do Conectivo OR, onde

verifica-se que o sinal lógico da saída é sempre o maior sinal entre os que estão aplicados

nas entradas. A tabela-verdade do Conectivo OR é apresentada na figura 4.9.

Figura 4.9 - Tabela-verdade do Conectivo OR.

46

CAPÍTULO 5 - IMPLEMENTAÇÃO DOS CIRCUITOS DAS PORTAS

LÓGICAS PARACONSISTENTES

5.1 - IMPLEMENTAÇÃO DOS CIRCUITOS LÓGICOS

5.1.1- INTRODUÇÃO

Com as tabelas-verdades elaboradas no capítulo 4 é feita a implementação dos

circuitos das portas lógicas paraconsistentes utilizando-se transistores CMOS.

Os circuitos das portas lógicas paraconsistente primitivas aqui apresentados foram

implementados a partir do circuito inversor de Kaniel [37 ] e [34] sugerido para aplicação

em lógicas multivaloradas ternárias.

Nos circuitos implementados é utilizada uma classe de Lógica Paraconsistente

Anotada onde cada variável proposicional é acompanhada por um único componente

47

anotacional. A constante anotacional sobredefinida, correspondente ao valor lógico

inconsistente pode aparecer como sinal de entrada ou ainda como sinal resultante.

O nível de tensão definido como inconsistente é de valor sobre-definido, portanto

maior que o nível lógico “1” (maior que +4V). Por esse motivo, o valor lógico para o sinal

inconsistente escolhido para o projeto das portas lógicas paraconsistentes é de amplitude de

tensão igual a +5V.

Nas simulações dos circuitos das portas lógicas utilizando-se o software Aim-Spice

1.5a, este nível de tensão é considerado como valor inconsistente.

Cada sinal lógico paraconsistente tem um nível de tensão definido. Estes valores

foram escolhidos por serem de amplitudes próximas as utilizadas nos circuitos

convencionais comumente usados.

Todos os circuitos projetados neste trabalho utilizam a técnica de implementação

dos transistores CMOS (Complementary Metal Oxide Silicon).

Esta tecnologia torna possível uma grande variedade de técnicas de projeto

envolvendo circuito digitais e se adequam perfeitamente a construção dos circuitos das

portas lógicas paraconsistentes desenvolvidos neste trabalho. Isto se deve ao fato que estes

transistores podem ser utilizados como chaves, tanto em sinais digitais como em sinais

analógicos, possibilitando projetos de circuitos para detetar níveis de tensão de qualquer

polaridade e transformá-los em sinais digitais de níveis diferentes.

No projeto dos circuitos das portas lógicas paraconsistentes a alimentação é feita

com uma fonte de tensão contínua simétrica de ± 6 Volts.

A fonte de alimentação simétrica com estas amplitudes é compatível com a faixa de

valores dos sinais lógicos envolvidos no funcionamento dos circuitos das portas lógicas

paraconsistentes.

As amplitudes de ±6V permitem também que os transistores CMOS sejam

convenientemente polarizados com uma boa margem de segurança.

Isto assegura ao

projeto um bom desempenho e funcionamento dos circuitos.

Os níveis de tensão do circuito relacionados com os valores lógicos paraconsistentes

estão apresentados nas tabelas da figura 5.1 :

48

Proposição

valor lógico

nível de tensão

0

- 4 Volts

1

+ 4Volts

Anotação ou grau de crença

valor lógico

nível de tensão

0

- 4 Volts

1/4

- 2Volts

1/2

0 Volts

3/4

+2 Volts

1

+4 Volts

+ 4Volts

T

Figura 5.1 - Relação entre níveis lógicos e níveis de tensão.

5.2 - CIRCUITO DETETOR DE NÍVEL DE TENSÃO

As portas lógicas paraconsistentes implementadas utilizam em sua maioria circuitos

detetores de nível de tensão que têm a finalidade de efetuar a seleção das tensões que são

aplicadas nas entradas dos circuitos.

Por este motivo o primeiro circuito apresentado é o detetor de nível de tensão que

foi projetado conforme circuitos sugeridos em [ 37 ].

49

Os circuitos detetores de nível de tensão são representados pelo bloco de linha

tracejada nos circuitos das portas lógicas paraconsistentes.

O detetor de nível de tensão é composto básicamente por um espelho de corrente e

um amplificador diferencial, ambos projetados com transistores CMOS, que fornecerá

corrente suficiente para polarizar os transistores alimentados com tensão de amplitudes ±

4V nos circuitos das portas lógicas.

Este circuito detetor de nível de tensão somente ativará os transistores polarizados

com amplitudes de ± 4V, quando receber nas suas entradas sinais com níveis de tensão com

estas amplitudes .

Se os sinais recebidos nas suas entradas forem de tensões ±2V, através dos detetores

de nível, os transistores alimentados com ± 4V ficam inativos.

Com isso, os transistores alimentados com tensões de ± 2V funcionam normalmente

e o circuito responderá somente a sinais de amplitudes ± 2V.

O circuito detetor de nível de tensão se apresenta conforme o diagrama da figura

5.2:

+6 Volts dc

M2

M6

M3

ES

In1

In2

M4

M1

M5

M7

M9

M8

-6 Volts dc

Figura 5.2 - Diagrama do circuito detetor de nível de tensão .

50

Aplicando-se uma tensão de amplitude constante de +3V na entrada In2 , na saída

Es se obtém uma tensão de amplitude +6V, enquanto a entrada In1 permanecer com níveis

de amplitude de tensão menores que +3V.

Quando na entrada In1 for aplicada uma tensão com amplitude maior que +3V, que

de acordo com a tabela apresentada na figura 5.1 é de valor lógico “1” (amplitude de +4V ),

a saída Es vai para a amplitude de -6V.

Por outro lado, mantendo-se uma tensão fixa de -3V na entrada In2 , a saída Es terá

uma tensão de amplitude -6V, enquanto a entrada In1 permanecer com níveis de amplitude

de tensão de polaridade negativa maior que -3V. Quando na entrada In1 for aplicada tensão

com amplitude de polaridade mais negativa que -3V, que nos circuitos é equivalente ao

valor lógico “0” ( amplitude de -4V ), a saída Es vai para a uma tensão de amplitude +6V.

Nos circuitos das portas lógicas paraconsistentes os transistores CMOS instalados

estrategicamente nas saídas dos circuitos detetores de nível de tensão, acionam os circuitos

alimentados com ±4V ao serem detetadas tensões destas amplitudes nas entradas dos

detetores, e ficam inoperantes quando estão aplicadas tensões de amplitudes ± 2V.

5.3- CIRCUITOS DOS OPERADORES n

Os circuitos dos operadores n implementados a partir das tabelas-verdades da figura

4.6 (capítulo 4), são apresentados nas próximas figuras. Nas tabelas-verdades dos

Operadores n, o sinal resultante na saída de cada operador é “1” para um único valor de

anotação, e “0” para os demais.

O valor da anotação cuja resposta é “1” difere para cada Operador.

No projeto de alguns dos Operadores utiliza-se circuito detetor de nível de tensão

para selecionar os níveis lógicos das anotações aplicados na entrada. Estes circuitos de

detecção estão simbolizados nos diagramas dos Operadores pelos blocos em linha tracejada.

51

Os diagramas dos circuitos dos Operadores unários estão expostos nas figuras 5.3,

5.4, 5.5, 5.6, 5.7 e 5.8.

5.3.1 - Operador i

+4volts

+6 Vdc Vss

-6 Vdc

T1

-3Vdc

Entrada

circuito

detector

de nível

de tensão

saída

T2

-4Volts

Figura 5.3 - Diagrama em blocos do Operador i.

Neste circuito, quando uma tensão de amplitude -4V que é equivalente ao nível

lógico “0”, for aplicada na entrada, o circuito detetor de tensão 1 apresentará em sua saída

uma amplitude de +6V. Com isso, o transistor T2 estará cortado e o transistor T1

conduzindo levando a saída do circuito a uma tensão de +4V ( nível lógico “1”).

Para qualquer outro sinal aplicado à entrada, o transistor T2 estará conduzindo e o

transistor T1 cortado.

Nestas condições,

na saída a tensão será de amplitude -4V,

equivalente ao nível lógico “0”.

52

5.3.2 - Operador j

+4volts

+6vdc

-3vdc

vss

-6vdc

circuito

detetor

de nível

de tensão 1

T1

T2

+6vdc vss

-1vdc

Entrada

-6vdc

saída

circuito

detetor

de nível

de tensão 2

T3

T4

-4Volts

Figura 5.4 - Diagrama em blocos do Operador j .

Neste circuito, quando uma tensão de amplitude -4V que é equivalente ao nível

lógico “0”, for aplicada na entrada, os circuitos detetores de tensão 1 e 2 apresentarão em

suas saídas tensões de amplitude -6V. Com isso, o transistor T4 estará conduzindo e os

transistores T1 e T2 estarão cortados levando a saída do circuito a tensão de -4V ( nível

lógico “0”).

53

Quando um valor de amplitude -2V (nível lógico “1/4”) estiver sendo aplicado na

entrada, os transistores T1 e T2 estarão conduzindo e os transistores T3 e T4 cortados,

fazendo com que a saída mantenha o nível lógico “1”, isto é, tensão de +4V. Para qualquer

outro sinal aplicado à entrada, o transistor T3 estará conduzindo e o transistor T2 cortado.

Nestas condições, na saída a tensão será de amplitude -4V, equivalente ao nível lógico “0”.

5.3.3 - Operador k

+4volts

+6vdc

-1vdc

vss

-6vdc

circuito

detetor

de nível

de tensão 1

T1

T2

+6vdc vss

+1vdc

Entrada

-6vdc

saída

circuito

detetor

de nível

de tensão 2

T3

T4

-4Volts

Figura 5.5 - Diagrama em blocos do Operador k .

54

Este circuito apresenta o funcionamento idêntico ao anterior, a única diferença é que

agora a amplitude de tensão que provocará o aparecimento na saída de tensão +4V,

equivalente ao nível lógico “1”, será a de 0V (nível lógico “1/2”).

5.3.4 - Operador L

+4volts

+6vdc

+1vdc

vss

-6vdc

circuito

detetor

de nível

de tensão 1

T1

T2

+6vdc vss

+3vdc

Entrada

-6vdc

saída

circuito

detetor

de nível

de tensão 2

T3

T4

-4Volts

Figura 5.6 - Diagrama em blocos do Operador L .

O funcionamento é idêntico ao anterior, a única diferença é que a amplitude de

tensão que provocará o aparecimento na saída de tensão +4V que é equivalente ao nível

lógico “1”, será de a de +2V (nível lógico “3/4”).

55

5.3.5 - Operador m

+4volts

+6vdc

+3vdc

vss

-6vdc

circuito

detetor

de nível

de tensão 1

T1

T2

+6vdc vss

+4.5v

dc

-6vdc

saída

circuito

detetor

de nível

de tensão 2

Entrada

T3

T4

-4Volts

Figura 5.7 - Diagrama em blocos do Operador m.

Este circuito apresenta o mesmo funcionamento do anterior, a única diferença é que

a amplitude de tensão que provocará o aparecimento na saída da tensão de +4V

(equivalente ao nível lógico “1”) será a de +4V (nível lógico “1”).

5.3.6 - Operador T

+4volts

+6 Vdc Vss

-6 Vdc

T1

Entrada

+4,5Vdc

circuito

detector

de nível

de tensão

saída

T2

Figura 5.8 - Diagrama em blocos do Operador T .

56

-4Volts

Quando na entrada deste circuito for aplicado um valor inconsistente, considerado

como sendo o de uma tensão de amplitude +5V, a saída será de +4V ( sinal lógico “1”).

Para qualquer outra tensão aplicada na entrada, a saída será de -4V (sinal lógico “0”).

5.4- CIRCUITO DO OPERADOR COMPLEMENTO

O circuito do operador COMPLEMENTO foi projetado com transistores CMOS, a

partir do circuito sugerido em [34], elaborado por Kaniel, indicado para lógicas

multivaloradas ternárias.

A seleção dos sinais que são aplicados na entrada Ve, é feita através dos circuitos

detetores de niveis de tensão estudados anteriormente.

O circuito que responde aos sinais de tensões de ± 2 Volts é mostrado na figura 5.9.

+2volts

R1

M4

M1

D1

R2

A

~A

D2

M2

M3

R3

-2volts

Figura 5.9- Diagrama do Operador COMPLEMENTO para os circuitos

alimentados com ± 2 Volts.

Os transistores M2 e M3 formam um detetor de limiar na entrada. Como os

transistores MOS funcionam no modo enriquecimento, nem M2 e nem M3 conduzem

57

corrente elétrica quando a entrada for zero volts (sinal lógico “1/2”). Portanto, M1 e M2

estarão desligados (não conduzem corrente elétrica), e a saída é estabilizada em zero volts

(sinal lógico “1/2”) em virtude do resistor R3.

Quando a entrada é de polaridade negativa, isto é, de tensão -4V (sinal lógico “0”), o

transistor M3 é desligado e o transistor M2 é ligado. Assim, uma corrente elétrica aparece

através de R1, ligando o transistor M1 e elevando a saída para tensão de +4V (sinal lógico

“1”), o que constitui um nível alto.

Desde que M2 e M3 conduz corrente elétrica um de cada vez, podem ocorrer 3

situações:

1) M1 ligado e M4 desligado .

2) M1 desligado e M4 ligado .

3) M1 e M4 desligados .

Adotando-se a relação dos valores lógicos com os níveis de tensão teremos:

Para uma entrada de -2 volts

= valor lógico “1/4”

Teremos uma saída de +2 volts

= valor lógico “3/4”

Para uma entrada de zero volts

= valor lógico “1/2”

Teremos uma saída de zero volts

= valor lógico “1/2”

Para uma entrada de +2 volts

= valor lógico “3/4”

Teremos uma saída de -2 volts

= valor lógico “1/4”

Para sinais de entrada com valores de amplitudes de tensão ± 4V o circuito anterior (figura

5.9) fica inoperante .

Para o acionamento dos circuitos alimentados com tensão de ±4V e tensão

equivalente ao sinal inconsistente de +5V, foram instalados circuitos detetores de nível de

tensão, que acionam os transistores apenas quando a entrada atingir a estes níveis.

58

O diagrama completo do circuito é o da figura 5.10 :

T

+4volts

+2volts

T7

circuito

detector de

nível de

tensão (3)

T5

R1

T4

D3

Valoração

T1

D1

Valoração

R2

Vs

Ve

D2

T2

T3

R3

circuito

detector

de nível

de tensão (2)

T6

-2Volts

-4Volts

Figura 5.10 - Diagrama em blocos do Operador COMPLEMENTO

No circuito do Operador COMPLEMENTO (figura 5.10), os blocos Detetores de

Nível de tensão (linha tracejada) acionam seus respectivos transistores (T5 e T6),

polarizados com amplitudes de ± 4V, para funcionarem como um inversor logo que uma

tensão elétrica desta amplitude seja detectada nas suas entradas. Se na entrada for aplicada

uma tensão de +5V, que equivale a um valor lógico inconsistente, o transistor T7 é

acionado e a saída será de +5V, conforme a tabela-verdade da figura 4.7 (capítulo 4).

59

Quando nas entradas estiverem aplicadas tensões de ± 2V, os blocos Detetores de

Nível mantém os transistores T5 , T6 e T7 desligados, liberando o circuito polarizado com

± 2V para funcionar normalmente .

No circuito polarizado com ± 2V, a saída será de 0V quando estiver sendo aplicada

uma tensão de 0V na sua entrada. A tensão de saída será de polaridade invertida quando na

sua entrada estiver sendo aplicadas simultaneamente tensões de amplitude de 2V.

Os diodos, instalados na saída do circuito alimentado com tensões ± 2V, servem

para isolar os circuitos alimentados com menor amplitude de tensão (± 2V), daqueles

alimentados com maior amplitude de tensão (± 4V e + 5V), quando estes estiverem ativos.

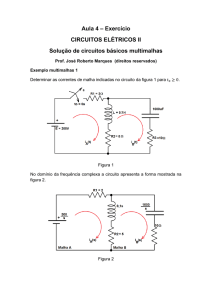

5.5- CIRCUITO DO CONECTIVO AND PARACONSISTENTE

O circuitos das porta AND paraconsistente é elaborado a partir da tabela-verdade do

conectivo AND da figura 4.8 (capítulo 4).

O circuito NAND que trata das valorações para níveis de tensão ± 2V, foi projetado

com base no circuito de Kaniel [35] já utilizado no circuito do operador COMPLEMENTO.

O circuito NAND que funciona para tensões de ± 2 V é apresentado na figura 5.11.

60

+ 2 Volts

R1

R2

m5

m6

m2

A

m1

R5

D1

C

B

D2

m4

m3

m7

R4

m8

R3

- 2 Volts

Figura 5.11 - Diagrama do conectivo NAND para os transistores

alimentados com ± 2V.

O circuito foi implementado desta forma porque as portas NAND convencionais não

respondem convenientemente quando se aplica tensões de amplitudes 0V (sinal de valor

lógico “1/2”) nas entradas A e B.

Nos circuitos convencionais, a saída obtida nesta

condição é uma tensão de amplitude +4V equivalente a uma valoração de “1”. Esta

amplitude de tensão não é compatível com o valor esperado na tabela-verdade.

O funcionamento do circuito é idêntico ao utilizado no Operador COMPLEMENTO

. A diferença consiste na instalação de um detetor de limiar para cada entrada, composto

pelos transistores m1, m2, m3 e m4. Os transistores de saída m6, m7 e m8 são os

componentes da função NAND.

O Operador COMPLEMENTO instalado na saída do circuito NAND, completa o

circuito transformando-o no Conectivo AND, e é apresentado na figura 5.12.

61

O circuito da porta AND paraconsistente é elaborado a partir da tabela-verdade do

conectivo AND. Veja a figura 4. 8 do capítulo 4.

+2Volt

s

+4Volts

+ 5Volts

Circuito

detector de

nível de

tensão (4)

Circuito

do

operador

COMPLEMENTO

V1

V2

vs

Circuito

detector de

nível de

tensão (2)

-2Volts

-4Volts

Figura 5.12 - Diagrama em blocos da Porta AND paraconsistente.

O circuito polarizado com tensão de amplitude +5V só funciona quando aparece

sinais inconsistentes nas entradas.

Os diodos, instalados nas saídas dos circuitos alimentado com tensões de ± 2V e

±4V servem para isolar os circuitos alimentados com menor amplitude de tensão, daqueles

alimentados com maior amplitude de tensão (±4V e +5V ), quando estes últimos estiverem

ativos.

Como foi visto, o circuito detetor de nível de tensão utilizado nos projetos é

composto por um espelho de corrente e amplificador diferencial implementado com

transistores CMOS, que fornecerá corrente suficiente para polarizar os transistores

alimentados com tensões de amplitudes ±4V e +5V. Este circuito somente ativará os

transistores polarizados com tensões de ± 4V e de +5V quando receber nas suas entradas

sinais com nível de tensão com estas amplitudes .

62

Se os sinais recebidos nas suas entradas forem de tensão ±2V, os transistores

alimentados com ± 4V e +5V ficam inativos, e o circuito responderá somente a sinais de

amplitudes de ±2V. Quando nas entradas estiverem presentes sinais Paraconsistentes o

circuito se apresentará conforme a tabela-verdade apresentada no capítulo 4 .

5.6 - CIRCUITO DO CONECTIVO OR PARACONSISTENTE

O circuitos das porta OR paraconsistente é elaborado a partir da tabela-verdade do

conectivo OR (Figura 4.9 - capítulo 4 ).

O circuito NOR que trata das valorações para níveis de tensão de ±2V, foi projetado com

base no circuito de Kaniel [35] já utilizado nos circuitos do Operador COMPLEMENTO e

Conectivo AND. O diagrama deste circuito é apresentado na figura 5.13

Figura 5.13 - Diagrama do Conectivo NOR para os transistores alimentados

com tensão de ± 2V.

No circuito da figura 5.13, temos um detetor de limiar para cada entrada composto pelos

transistores de m1, m2, m3 e m4, e os transistores de saída m6, m7 e m8 compõem a função

NOR.

63

Utilizando-se dos circuitos detetores de nível de tensão é implementada a parte que

aciona os transistores alimentados com tensão de ± 4V.

A porta NOR seguida do circuito do Operador COMPLEMENTO transforma o

circuito NOR em uma porta OR.

O circuito completo da porta OR paraconsistente é mostrado na figura 5.14.

+5Volts

+4Volts

+2Volt

Circuito

detetor de

nível de

tensão (4)

Circuito

do

operador

COMPLEMENT

O

v1

V2

vs

Circuito

detetor de

nível de

tensão (2)

-2Volts

-4Volts

Figura 5.14 - Diagrama em blocos da Porta OR paraconsistente.

O funcionamento básico da porta lógica OR paraconsistente é idêntico ao da porta

AND. O circuito detetor de nível de tensão é composto por um espelho de corrente e

amplificador diferencial, projetado com transistores CMOS, que fornecerá corrente

suficiente para polarizar os transistores alimentados com tensão de ± 4V. Somente os

transistores polarizados com ± 4V é que estarão ativos quando nas entradas A e B

aparecerem sinais com níveis de tensão com estas amplitudes. Se os sinais recebidos nas

entradas forem de tensões de ±2V, os transistores alimentados com ± 4V ficam inativos, e

o circuito responderá somente aos sinais de amplitudes de tensão ±2V. Na presença de um

64