X-1

A FAMÍLIA 8086

X.1 - INTRODUÇÃO

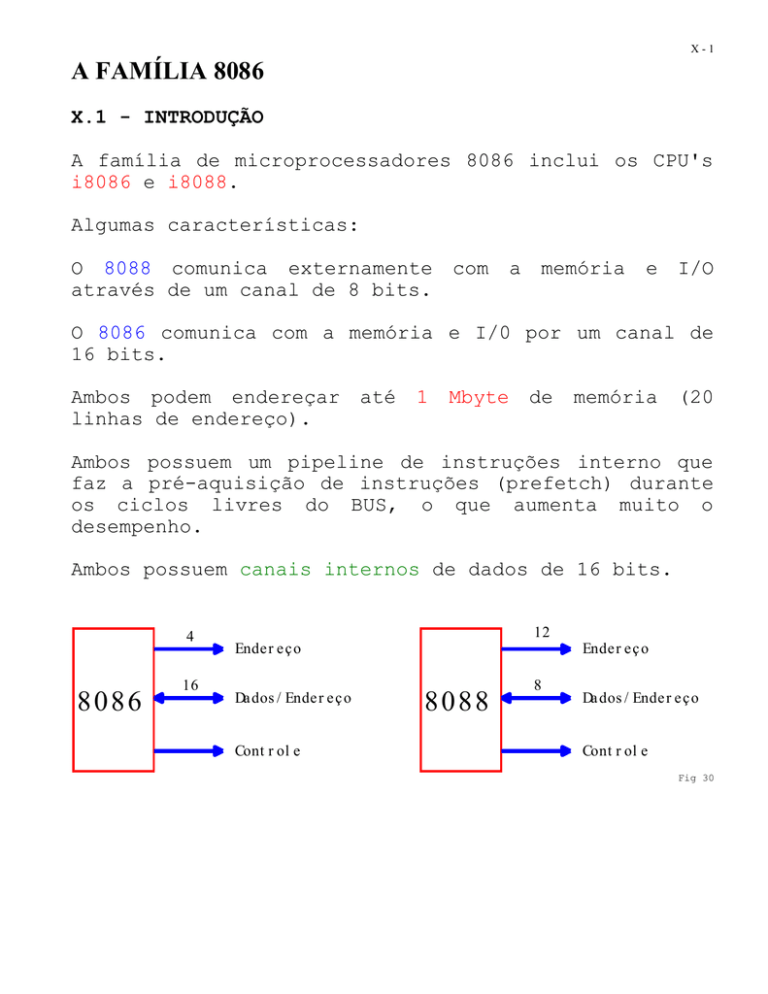

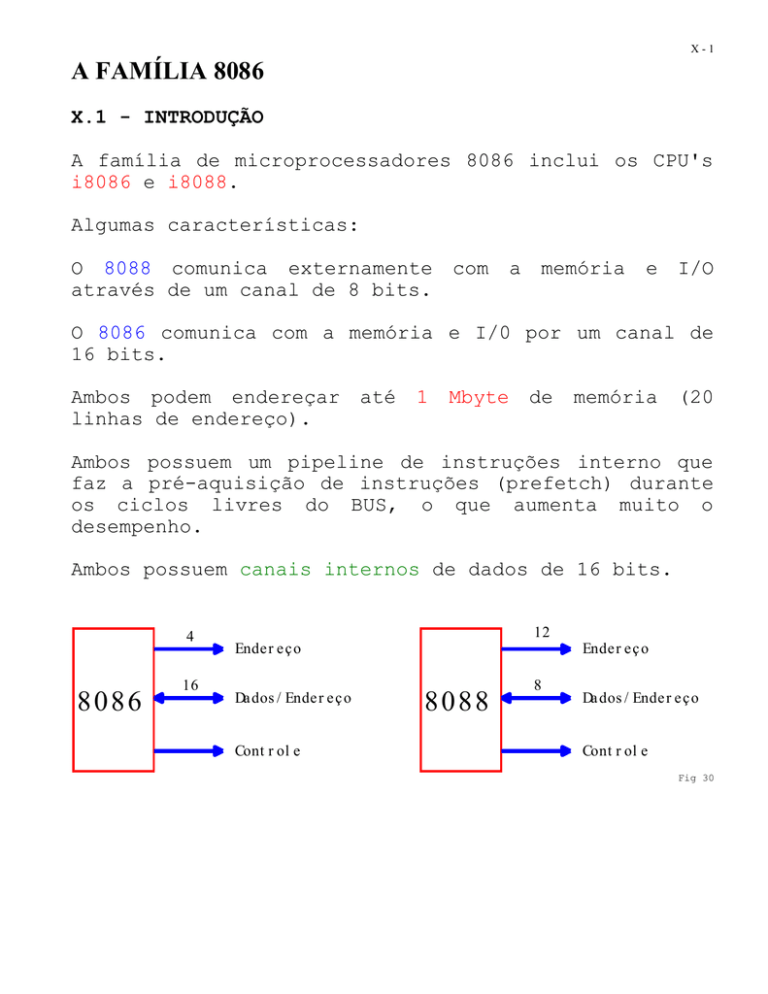

A família de microprocessadores 8086 inclui os CPU's

i8086 e i8088.

Algumas características:

O 8088 comunica externamente

através de um canal de 8 bits.

com

a

memória

e

I/O

O 8086 comunica com a memória e I/0 por um canal de

16 bits.

Ambos podem endereçar

linhas de endereço).

até

1

Mbyte

de

memória

(20

Ambos possuem um pipeline de instruções interno que

faz a pré-aquisição de instruções (prefetch) durante

os ciclos livres do BUS, o que aumenta muito o

desempenho.

Ambos possuem canais internos de dados de 16 bits.

4

8086

16

12

Ende r e ç o

Da dos / Ende r e ç o

Cont r ol e

Ende r e ç o

8088

8

Da dos / Ende r e ç o

Cont r ol e

Fig 30

X-2

X.2 - A ARQUITECTURA DOS PROCESSADORES

Uni da de de i nt e r f a c e

c om o BUS ( BI U)

Uni da de de e xe c uç ã o ( EU)

Re gi s t os

Ge r a i s

Re gi s t os de

s e gme nt o

Ap I ns t r ( I P)

Ge r a ç ã o de

e nde r e ç os e

c ont r ol e do

BUS

BUS

Mul t i pl e xa do

Ope r a ndos

Fi l a de

i ns t r uç õe s

ALU

Fl a gs

Fig 31

Os endereços manipulados pela EU são de 16 bits.

A BIU realiza uma relocação de endereços que permite

o acesso a um espaço de memória de 1 Mbyte.

A BIU executa

sistema:

todas

as

operações

com

o

BUS

do

Troca de dados entre a EU e a memória do sistema e

dispositivos de I/O.

Enquanto a EU está ocupada a executar instruções, a

BIU lê na memória central as próximas instruções a

realizar (prefetch).

X-3

X.2.1 - Registos gerais

O 8086 tem um conjunto de 8 registos gerais de 16

bits organizados da seguinte forma:

15

8 7

AX

AH

0

AL

Ac u mu l a d o r

BL

Ba s e

CL

Co n t a d o r

BX

Gr u p o

de

da dos

BH

CX

CH

DX

DH

15

Gr u p o d e

a pont a dor e s

e í ndi c e s

Da d o s

DL

0

SP

Ap o n t a d o r

d e St a c k

BP

Ap o n t a d o r

de ba s e

SI

Í ndi c e

de or i ge m

DI

Í ndi c e

de de s t i no

Fig 32

Algumas

instruções

implícita.

Registo

AX

AL

AH

BX

CX

CL

DX

SP

SI

DI

usam

os

registos

de

X-4

forma

Operações

Multiplicação, divisão, I/O (Word)

Multiplicação, divisão, I/O (Byte)

Multiplicação, divisão (Byte)

Tradução

Loops, operações com strings

Rotação e deslocamento de variáveis

Multiplicação, divisão, (Word);

I/O indirecto

Operações de stack

Operações com strings

Operações com strings

X-5

X.2.2 - Registos de segmento e apontador de instrução

O espaço de memória do 8086 está dividido

segmentos lógicos de até 64 kbyte cada um.

em

O CPU tem acesso a 4 segmentos em simultâneo. Os seus

endereços de base estão contidos nos registos de

segmento.

15

0

CS

Se g me n t o

de c ódi go

DS

Se g me n t o

de da dos

SS

Se g me n t o

d e St a c k

ES

Se g me n t o

e xt r a

Fig 33

O apontador de instrução (IP) é um registo de 16 bits

que

em execução normal tem o offset relativo a CS da

próxima instrução a ser fetched pela BIU;

quando é guardado na stack tem o valor da próxima

instrução a ser executada.

X-6

X.2.3 - Flags

O 8086 tem 3 flags de controle que podem ser

alteradas pelos programas para alterar as operações

do processador, e 6 flags de estado que reflectem

certas propriedades do resultados das operações

aritméticas ou lógicas.

Fl a gs de c ont r ol e

TF

DF

IF

Fl a gs de e s t a do

OF

SF

ZF

AF

PF

CF

Ca r r y

Pa r i da de

Auxi l i a r

Ze r o

Si na l

Ove r f l ow

I nt e r r upt

Ena bl e

Di r e c ç ã o

Tr a p

Fig 34

carry - carry ou borrow no bit mais significativo

(MSB) de um resultado (8 ou 16 bits)

paridade - paridade par quando activa

auxiliar - carry ou borrow entre nibbles (usada por

aritmética decimal)

zero - o resultado da operação é 0

sinal - o MSB é 1 (número negativo)

overflow - perda de um bit significativo

X-7

interrupt enable - permite que o CPU reconheça

interrupções externas (mascaráveis)

direcção - quando activa provoca o auto-decremento

nas intruções sobre strings, de contrário

provoca o auto-incremento

trap - põe o processador no modo single-step para

debugging

X-8

X.3 - MEMÓRIA

X.3.1 - Organização

O espaço de memória do 8086

conjuntos de bytes (8 bits).

está

organizado

em

Instruções e dados podem ser guardados em quaisquer

endereços sem ter em atenção alinhamento algum. O

código fica densamente arrumado, poupando memória.

No entanto, variáveis de 16 bits com endereços

ímpares (não alinhadas) não aproveitam a capacidade

de transferência de 16 bits em simultâneo do 8086.

As instruções não precisam de estar alinhadas.

Variáveis de 16 bits (word) são guardadas em

memória com o byte menos significativo na posição de

memória mais baixa.

Apontadores (doubleword) são compostos por 2 words. A

word de endereço mais baixo contém um offset. A word

de endereço mais elevado contém o endereço base do

segmento.

X-9

X.3.2 - Segmentação

O espaço de memória de 1 Mbyte do 8086 é visto pelos

programas como um grupo de segmentos de até 64 kbytes

definidos por cada aplicação.

Os segmentos

bytes.

têm

endereços

base

múltiplos

de

16

Os

segmentos

podem

ser

adjacentes,

disjuntos,

parcialmente ou totalmente sobrepostos. Um endereço

físico pode estar contido num ou mais segmentos.

FFFFFH

A

B

Da dos :

DS:

B

Códi go: CS:

E

St a c k:

SS:

H

Ext r a :

ES:

J

C

D

E

F

G

J

0H

H

I

K

Fig 35

X - 10

X.3.3 - Geração de endereços físicos

Cada posição de memória tem apenas um endereço

físico, mas pode ter vários endereços lógicos.

Um endereço físico pode variar entre 0H e FFFFFH.

Um endereço lógico é dado por 2 valores: base do

segmento e offset.

De s l oc a r 4 bi t s

à e s que r da

1

2

3

4

15

1

2

3

4

0

0

19

0

0

0

2

15

0

0

2

2

2

Ende r e ç o

l ógi c o

Of f s e t

0

2

15

1

Ba s e do

s e gme nt o

0

3

6

2

19

Ende r e ç o f í s i c o

0

Pa r a a me mór i a

Fig 36

Origens dos endereços lógicos

Tipo de referência a memória

Aquisição de instrução (fetch)

Operação em stack

Variável (excepto seguintes)

String de origem

String de destino

BP como registo de base

Base de

segmento por

omissão

CS

SS

DS

DS

ES

SS

Base de

segmento

alternativo

Nenhum

Nenhum

CS,ES,SS

CS,ES,SS

Nenhum

CS,DS,ES

Offset

IP

SP

Endereço efectivo

SI

DI

Endereço efectivo

X - 11

X.3.4 - Implementação da Stack (pilha)

A stack no 8086 encontra-se em memória e é

referenciada pelos registos SS (stack segment) e SP

(stack pointer).

Um sistema pode ter um número ilimitado de stacks, e

uma stack pode ter até 64 kbytes de capacidade.

Apenas se pode endereçar uma stack de cada vez.

As operações na stack são sempre sobre 16 bits.

Um valor é carregado (PUSHed) em stack decrementando

o SP 2 unidades e escrevendo o valor na stack.

Um valor é retirado (POPed) da stack lendo-o do topo

da stack e incrementando o SP 2 unidades.

Fi m da s t ack

TOS

1062

1060

105E

105C

105A

1058

1056

1054

1052

1050

0 0

2 2

4 4

6 6

8 8

AA

0 1

4 5

8 9

CD

1 1

3 3

5 5

7 7

9 9

BB

2 3

6 7

AB

EF

1 0

5 0

0 0

0 8

POP AX

POP BX

PUSH AX

AX 1 2 3 4

0 0

2 2

4 4

6 6

8 8

AA

1 2

4 5

8 9

CD

1 1

3 3

5 5

7 7

9 9

BB

3 4

6 7

AB

EF

SS

1 0

5 0

SP

0 0

0 6

TOS

For a

da

s t ack

1062

1060

105E

105C

105A

1058

1056

1054

1052

1050

AX 1 2

3 4

BX 1 2

3 4

0 0

2 2

4 4

6 6

8 8

AA

1 2

4 5

8 9

CD

1 1

3 3

5 5

7 7

9 9

BB

3 4

6 7

AB

EF

SS

1 0

5 0

SP

0 0

0 A SP

TOS

1062

1060

105E

105C

105A

1058

1056

1054

1052

1050

SS

Fig 37

Operação em stack para a sequência de código

PUSH AX

POP AX

POP BX

X - 12

X.4 - INSTRUÇÕES

X.4.1 - Instruções de transferência de dados

MOV destino, origem

PUSH origem

POP destino

XCHG destino, origem

XLAT tabela

IN acc, porto

OUT porto, acc

LEA destino, origem

LDS destino, origem

LES destino, origem

LAHF

SAHF

PUSHF

POPF

Âmbito Geral

Move byte ou word

Carrega word na stack

Retira word da stack

Troca byte ou word

Traduz byte

Entrada / Saída

Lê byte ou word

Escreve byte ou word

Endereço

Carrega endereço efectivo

Carrega apontador usando DS

Carrega apontador usando ES

Transferência de flags

Coloca as flags em AH

Coloca AH nas flags

Carrega as flags na stack

Retira flags da stack

X - 13

X.4.2 - Instruções aritméticas

ADD destino, origem

ADC destino, origem

INC destino

AAA

DAA

SUB destino, origem

SBB destino, origem

DEC destino

NEG destino

CMP destino, origem

AAS

DAS

MUL origem

IMUL origem

AAM

DIV origem

IDIV origem

AAD

CBW

CWD

Adição

Adiciona byte ou word

Adiciona byte ou word com carry

Incrementa byte ou word 1 unidade

Ajusta ASCII para adição

Ajusta decimal para adição

Subtracção

Subtrai byte ou word

Subtrai byte ou word com borrow

Decrementa byte ou word 1 unidade

Nega byte ou word

Compara byte ou word

Ajusta ASCII para subtração

Ajusta decimal para subtacção

Multiplicação

Multiplica byte ou word sem sinal

Multiplicação inteira de byte ou word

Ajuste ASCII para multiplicação

Divisão

Divide byte ou word sem sinal

Divisão inteira de byte ou word

Ajuste ASCII para divisão

Converte byte em word

Converte word em doubleword

X - 14

X.4.3 - Instruções de manipulação de bits

NOT destino

AND destino, origem

OR destino, origem

XOR destino, origem

TEST destino, origem

SHL / SAL destino, count

SHR destino, count

SAR destino, count

ROL destino, count

ROR destino, count

RCL destino, count

RCR destino, count

Lógicas

Complementa byte ou word

Produto lógico de byte ou word

Soma lógica de byte ou word

Ou exclusivo de byte ou word

Teste (AND) de byte ou word

Deslocamentos

Deslocamento lógico / aritmético de byte

ou word à esquerda

Deslocamento lógico de byte ou word à

direita

Deslocamento aritmético de byte ou word

à direita

Rotações

Roda byte ou word à esquerda

Roda byte ou word à direita

Roda byte ou word com carry à esquerda

Roda byte ou word com carry à direita

X - 15

X.4.4 - Instruções sobre strings

REP

REPE / REPZ

REPNE / REPNZ

MOVS destino, origem

MOVSB / MOVSW

CMPS destino, origem

SCAS destino

LODS origem

STOS destino

Repete

Repete enquanto for igual / zero

Repete enquanto não for igual / não zero

Move string de bytes ou words

Move string de bytes ou words

Compara string de bytes ou words

Pesquisa string de bytes ou words

Lê string de bytes ou words

Escreve string de bytes ou words

Registos e flags utilizados

SI

DI

CX

AL / AX

DF

ZF

Índice (offset) da string origem

Índice (offset) da string destino

Contador de repetições

Valor para pesquisa

Destino para LODS

Origem para STOS

0 = auto-incrementa SI, DI

1 = auto-decrementa SI, DI

Termina pesquisa ou comparação

X - 16

Fluxo das operações com strings

Inicializa

SI, DI,

CX e DF

Prefixo

REPEAT

P

r

e

s

e

n

t

A

u

s

e

n

t

e

e

CX = 0

S

N

Decrementa

CX 1 unidade

Opera

string

usando

SI / DI

Ajusta

SI / DI

de delta

CMPS

ou

SCAS

N

P

r

e

s

e

n

t

S

S tr i n g

DF

d e l ta

B y te

B y te

W o rd

W o rd

0

1

0

1

1

-1

2

-2

P r e fi x o

z

REPE

REPZ

REPNE

REPNZ

1

1

0

0

ZF = z

S

N

Prefixo

REPEAT

e

A

u

s

e

n

t

e

Próxima

instrução

Diag 5

X - 17

X.4.5 - Instruções de transferência de controle

Transferências incondicionais

CALL nome-de-rotina

Chama procedimento

RET valor-a-retirar (op)

Volta de um procedimento

JMP endereço

Salta

Transferências condicionais

JA / JNBE rótulo

Salta se superior / não inferior nem igual

JAE / JNB rótulo

Salta se superior ou igual / não inferior

JB / JNAE rótulo

Salta se inferior / não superior nem igual

JBE / JNA rótulo

Salta se inferior ou igual / não superior

JC rótulo

Salta se carry

JE / JZ rótulo

Salta se igual / zero

JG / JNLE rótulo

Salta se superior / não inferior nem igual

JGE / JNL rótulo

Salta se superior ou igual / não inferior

JL / JNGE rótulo

Salta se inferior / não superior nem igual

JLE / JNG rótulo

Salta se inferior ou igual / não superior

JNC rótulo

Salta se não carry

JNE / JNZ rótulo

Salta se não for igual / não zero

JNO rótulo

Salta se não overflow

JNP / JPO rótulo

Salta se não paridade / paridade ímpar

JNS rótulo

Salta se não tiver sinal

JO rótulo

Salta se overflow

JP / JPE rótulo

Salta se paridade / paridade par

JS rótulo

Salta se tiver sinal

Controle de iteração

LOOP rótulo

Ciclo

LOOPE / LOOPZ rótulo

Ciclo se igual / zero

LOOPNE / LOOPNZ rótulo Ciclo se não igual / não zero

JCXZ rótulo

Salta se CX = 0

Interrupções

INT tipo

Interrupção

INTO

Interrupção se overflow

IRET

Volta de interrupção

X - 18

Mnemónica

JA / JNBE

JAE / JNB

JB / JNAE

JBE / JNA

JC

JE / JZ

JG / JNLE

JGE / JNL

JL / JNGE

JLE / JNG

JNC

JNE / JNZ

JNO

JNP / JPO

JNS

JO

JP / JPE

JS

Condições testadas

(CF ou ZF) = 0

CF = 0

CF = 1

(CF ou ZF) = 1

CF = 1

ZF = 1

((SF xor OF) ou ZF) = 0

(SF xor OF) = 0

(SF xor OF) = 1

((SF xor OF) ou ZF) = 1

CF = 0

ZF = 0

OF = 0

PF = 0

SF = 0

OF = 1

PF = 1

SF = 1

X - 19

X.4.6 - Instruções de controle do processador

STC

CLC

CMC

STD

CLD

STI

CLI

HLT

WAIT

ESC

LOCK

NOP

Operações com flags

Activa flag de carry

Desactiva flag de carry

Complementa flag de carry

Activa flag de direcção

Desactiva flag de direcção

Activa flag de interrupt enable

Desctiva flag de interrupt enable

Sincronização externa

Pára até interrupção ou reset

Espera até pino TEST/ estar activo

Escape para processador externo

Prende o bus para a próxima instrução

Sem efeito

Não efectua nenhuma operação

X - 20

X.5 - MODOS DE ENDEREÇAMENTO

Cálculo dos endereços de memória

Í ndi c e dupl o

Í n d i c e s i mp l e s

Co d i f i c a d o

na

i ns t r uç ã o

Ex p l í c i t o

na

i ns t r uç ã o

BX

ou

BP

BX

ou

BP

ou

SI

ou

DI

SI

ou

DI

EU

d e s l o c a me n t o

En d e r e ç o

e f e c t i vo

0

CS

ou

As s u mi d o

por

o mi s s ã o

0

SS

ou

0

DS

BI U

ou

ES

En d e r .

0

f í s i co

Fig 38

O endereço efectivo é calculado pela EU. É um número

de 16 bits que representa a distância do operando ao

início do segmento onde reside.

X - 21

X.5.1 - Operandos em registo e imediato

As instruções com operandos apenas em registo são as

mais compactas e rápidas. São executadas inteiramente

na CPU.

Exemplo:

ADD AX, BX

Os operandos imediatos são constantes contidas na

instrução, sendo por isso de acesso rápido. Servem

apenas como origem, nunca como destino.

Exemplo:

ADD AL, 5

X.5.2 - Endereçamento directo

É o modo de endereçamento mais simples. É usado para

endereçar variáveis simples (escalares).

OP CODE

R/ M MOD

de s l oc a me nt o

End. e f e c t i vo

Fig 39

Exemplo:

ADD CX, alfa

ADD alfa, 6

X - 22

X.5.3 - Endereçamento indirecto

Uma instrução pode operar em diferentes posições de

memória se o registo de base ou índice for

actualizado. Instruções aritméticas e LEA podem ser

usadas para o efeito.

OP CODE

R/ M MOD

BX

BP

SI

ou

ou

End. e f e c t i vo

ou

DI

Fig 40

Exemplo:

ADD BL, [BX]

ADD [SI], 12

X - 23

X.5.4 - Endereçamento com registo de base

O endereço efectivo é a soma do deslocamento com o

conteúdo do registo BX ou BP. É usado para endereçar

estruturas.

OP CODE

R/ M MOD

d e s l o c a me n t o

BX

BP

ou

En d . e f e c t i v o

Fig 41

Acesso a uma estrutura usando endereçamento com base

En d e r e ç o s a l t o s

d e s l o c a me n t o

d e s l o c a me n t o

( Da t a _ d e _ i n s c r i ç ã o )

( Da t a _ d e _ i n s c r i ç ã o )

Pr o p i n a

At r a s o

Da t a _ d e _ i n s c r i ç ã o

Re g i s t o b a s e

Cu r s o

Tu r ma

I da de

Es t a d o

Re g i s t o b a s e

Nú me r o _ d e _ a l u n o

En d .

e f e c t i vo

En d .

Pr o p i n a

e f e c t i vo

At r a s o

Da t a _ d e _ i n s c r i ç ã o

Cu r s o

Tu r ma

I da de

Es t a d o

Nú me r o _ d e _ a l u n o

En d e r e ç o s b a i x o s

Fig 41a

Exemplo:

ADD [vector].alfa, AH

X - 24

X.5.5 - Endereçamento indexado

O endereço efectivo é a soma do deslocamento com o

conteúdo de SI ou DI. É usado para o endereçamento de

vectores.

OP CODE

R/ M MOD

d e s l o c a me n t o

SI

DI

ou

En d . e f e c t i v o

Fig 42

Acesso a um vector usando endereçamento indexado

En d e r e ç o s a l t o s

d e s l o c a me n t o

Ar r a y ( 1 1 )

d e s l o c a me n t o

Ar r a y ( 1 0 )

Re g i s t o d e í n d i c e

Ar r a y ( 9 )

Re g i s t o d e í n d i c e

Ar r a y ( 8 )

20

6

Ar r a y ( 7 )

En d .

e f e c t i vo

Ar r a y ( 6 )

En d .

e f e c t i vo

Ar r a y ( 5 )

Ar r a y ( 4 )

Ar r a y ( 3 )

Ar r a y ( 2 )

Ar r a y ( 1 )

Ar r a y ( 0 )

1 wo r d

En d e r e ç o s b a i x o s

Exemplo:

ADD CX, alfa[SI]

ADD alfa[DI+2], 10

Fig 42a

X - 25

X.5.6 - Endereçamento indexado e com registo de base

O endereço efectivo é a soma do registo de base com

um registo de índice e um deslocamento.

OP CODE

R/ M MOD

d e s l o c a me n t o

BX

BP

ou

SI

DI

ou

En d . e f e c t i v o

Fig 43

Exemplo:

ADD [BX].alfa[SI], AL

ADD SI, [BP+4][DI]

X.5.7 - Endereçamento de strings

Os registos de índice são usados implicitamente.

Em operações repetidas a CPU ajusta SI e

automaticamente de modo a obter bytes ou words.

DI

OP CODE

SI

End. e f e c t i vo

( or i ge m)

DI

End. e f e c t i vo

( de s t i no)

Fig 44

X - 26

X.5.8 - Endereçamento de portos de I/O

No endereçamento directo o

operando de 8 bits imediato.

OP CODE

número

do

porto

é

um

Da do

End. do por t o

Fig 45

Exemplo:

IN AL, 30

No endereçamento indirecto o número do porto é lido

de DX e utiliza 16 bits.

OP CODE

DX

End. do por t o

Fig 46

Exemplo: OUT DX, AX

X - 27

X.6 - PROGRAMAÇÃO EM ASSEMBLY 86

X.6.1 - Definição de dados

Constantes

Podem ser números

hexadecimais.

binários,

decimais,

octais

ou

Todos os números devem ser representados em 16 bits

incluindo um bit de sinal.

Os números negativos são representados em complemento

para 2.

Exemplos:

letra_A

EQU

'A'

;caracter

hexa_A

EQU

41H

;equivalente em hex.

hexa_196

EQU

0C4H

;hexadecimal

octal_8

EQU

10O

;octal

tudo_uns

EQU

11111111B

;binário

menos_5

EQU

-5

;decimal

X - 28

Variáveis

Podem ser do tipo byte , word ou doubleword. As

directivas DB, DW e DD servem para reservar o

respectivo espaço em memória.

Exemplos:

dados_1

SEGMENT

alfa

beta

gama

delta

epsilon

DB

DW

DD

DB

DW

dados_1

ENDS

dados_2

SEGMENT AT 55H

;especifica endereço de base

iota

kapa

lambda

mu

DB

DW

DD

DB

;contém 48 45 4C 4C 4F H

;contém 42 41 H

;contém 0000 5500 H

;contém (100 x) 00H

dados_2

ENDS

?

?

?

?

5

'HELLO'

'AB'

dados_1

100 DUP (0)

;não inicializada

;não inicializada

;não inicializada

;não inicializada

;contém 05H

X - 29

O assembly 86 guarda três atributos de cada variável

e fornece dois operadores que podem ser usados em

programação.

Variável

alfa

beta

gama

delta

epsilon

iota

kapa

lambda

mu

Segmento

dados_1

dados_1

dados_1

dados_1

dados_1

dados_2

dados_2

dados_2

dados_2

Atributos

Offset

0

1

3

7

8

0

5

7

11

Tipo

1

2

4

1

2

1

2

4

1

Operadores

LENGTH

1

1

1

1

1

5

1

1

100

SIZE

1

2

4

1

2

5

2

4

100

Estruturas

Uma estrutura é uma entidade que

atributos a um conjunto de campos.

Exemplo:

empregado

STRUC

num_cont

dept

ano_contr

DB

DB

DW

empregado

ENDS

9

1

1

DUP(?)

DUP(?)

DUP(?)

dá

um

nome

e

X - 30

X.6.2 - Directivas

Um programa em assembly 86 compreende uma série de

segmentos: segmento de código, segmento de dados,

segmento de stack.

As directivas SEGMENT e ENDS iniciam e terminam o

segmento.

A directiva ASSUME diz ao assemblador quais os

endereços que serão colocados nos registos de

segmento durante a execução do programa.

Exemplo:

dados

dados

pilha

SEGMENT

;definição dos dados

ENDS

pilha

SEGMENT

DW 100 DUP(?)

topo_da_pilha

LABEL

ENDS

codigo

SEGMENT

ASSUME

CS: codigo

DS: dados

ES: dados

SS: pilha

inicio:

MOV

MOV

MOV

MOV

MOV

MOV

AX, dados

DS, AX

ES, AX

AX, pilha

SS, AX

SP, OFFSET topo_da_pilha

; programa principal

codigo

ENDS

END

WORD

inicio

X - 31

X.6.3 - Procedimentos

Um procedimento em assembly 86 é invocado com

instrução

CALL.

O

procedimento

termina

com

instrução RET que transfere o controle para

instrução seguinte ao CALL.

a

a

a

Os parâmetros para o procedimento podem ser passados

por registo ou por stack.

Exemplo:

savebp

MACRO

PUSH

MOV

BP

BP, SP

ENDM

deccount

num

deccount

; definição de uma macro

; guarda o valor de bp

; fim da definição de macro

PROC

NEAR

EQU WORD PTR [BP+4]

savebp

PUSH

num

CALL

_lercount

ADD

SP, 2

DEC

AX

PUSH

AX

PUSH

num

CALL

_esccount

ADD

SP,4

POP

BP

RET

ENDP

; Programa principal

...

PUSH

CALL

ADD

...

indice

deccount

SP,2

; definição de um procedimento

; repõe o valor de bp

; fim da definição de

; procedimento

X - 32

X.6.4 - Strings

Exemplo de cópia (deslocada de 10 bytes) de 20 bytes

da string linha_1 para a string linha_2.

REP

LEA SI, linha_1

LEA DI, linha_2 + 10

MOV CX, 20

CLD

MOVS linha_2, linha_1

;inicializa

;registos de índice

;contador de repetições

;auto-incrementa

Exemplo de comparação alfabética de 2 nomes.

MOV

MOV

MOV

CLD

REPE

CMPS

JB

nome_1_menor:

nome_2_menor:

SI, OFFSET nome_1

DI, OFFSET nome_2

CX, SIZE nome_2

;alternativo ao LEA

;contador

;auto-incrementa

;enquanto for igual

nome_2, nome_1

nome_2_menor

;não é relevante para

;o exemplo

Exemplo de procura do último ponto ('.') numa string.

MOV DI, OFFSET frase +

LENGTH frase

;começa pelo fim

MOV CX, SIZE frase

;contador

STD

;auto-decrementa

MOV AL, '.'

;argumento de procura

REPNE

SCAS

frase

JCXZ

nao_ha_ponto

ha_ponto:

;não é relevante para

nao_ha_ponto:

;o exemplo

&