1180

IEEE LATIN AMERICA TRANSACTIONS, VOL. 10, NO. 1, JAN. 2012

VHDL Implementation of a Flexible and

Synthesizable FFT Processor

I. S. Correa, L. C. Freitas, A. Klautau and J. C. W. A. Costa

Abstract— This paper presents the current stage of development

of a fast Fourier transform (FFT) processor in VHDL. This

processor uses fixed-point as numeric representation, taking

advantage of the facilities provided by the IEEE fixed point

package. Its main advantages is that it is being developed as fully

parameterizable processor, in a way that the number of bits, fixed

point position and number of points computed in the FFT can be

easily changed. It is also able to be used in several applications such

as classification algorithms and communications systems. An open

source prototype core has been developed and it can perform a

complete FFT transform using radix-2 with decimation in time.

Results and details of this implementation are presented.

Keywords— VHDL language, digital hardware design, FFT.

T

I. INTRODUÇÃO

RANSFORMADA de Fourier é uma operação matemática

envolvendo exponenciais complexas que pode representar

um sinal através de suas componentes de frequência,

permitindo a análise de um sinal do domínio do tempo no

domínio da frequência [1]. A transformada de Fourier é base

de muitos estudos científicos, como em Física no estudo do

movimento de ondas eletromagnéticas, com aplicações em

telecomunicações, reconhecimento de voz e outros.

Quando a análise de um sinal no domínio da frequência é

realizada utilizando um computador, a ferramenta para análise

de Fourier mais popular é a chamada Discrete Fourier

Transform (DFT) [1], que basicamente corresponde a

multiplicar o sinal a ser analisado por uma matriz cujos

elementos são números complexos. Devido à complexidade

computacional encontrada nessas multiplicações, em [3] foi

proposto um algoritmo eficiente para o cálculo da DFT. A

partir desse algoritmo, vários outros foram propostos e

atualmente eles compõem uma família de algoritmos chamada

Fast Fourier Transform (FFT), a qual permite a execução

rápida e eficiente da DFT em computador.

Para aplicações que usam FFT e requerem resposta em

tempo real a melhor alternativa é a implementação de

algoritmos de FFT em hardware dedicado (e não em um

computador), por exemplo utilizando dispositivos lógicos

programáveis e linguagens de descrição de hardware. Esse

I. S. Correa, Federal University of Pará (UFPA), Belém, Pará, Brazil,

[email protected]

L. C. Freitas, Federal University of Pará (UFPA), Belém, Pará, Brazil,

[email protected]

A. Klautau, Federal University of Pará (UFPA), Belém, Pará, Brazil,

[email protected]

J. C. W. A. Costa, Federal University of Pará (UFPA), Belém, Pará,

Brazil , [email protected]

tipo de implementação apresenta menor tempo de execução

quando comparado com as implementações utilizando

linguagens de programação tradicionais, pois são projetadas

focando a execução em hardware dedicado, se beneficiando

do potencial de paralelização do projeto de hardware.

Dessa forma, este artigo apresenta o projeto de um

processador de FFT utilizando a linguagem de descrição de

hardware chamada VHSIC Hardware Description Language

(VHDL) [4]. Tal linguagem é projetada para tratar

nativamente características inerentes dos circuitos lógicos que

compõem o hardware. O processador de FFT desenvolvido

neste artigo utiliza ponto fixo como representação numérica

dos dados, e foi projetado para ser flexível o suficiente para

permitir que parâmetros como número de bits e número de

pontos da FFT possam ser facilmente alterados, possibilitando

que o mesmo processador de FFT possa ser utilizado em uma

variedade de aplicações.

A FFT é composta por várias operações elementares

realizadas com todas as amostras de um sinal. Essa operação é

chamada butterfly e é composta por multiplicações e somas. A

butterfly normalmente é realizada com 2 ou 4 amostras de um

sinal por vez, e são chamadas radix-2 [6] ou radix-4 [7],

respectivamente. Nesse artigo foi implementado o algoritmo

FFT com radix-2, devido sua simplicidade e seu baixo uso de

recursos.

Na literatura há muitos artigos descrevendo implementações

de FFT como em [2], [6] e [7], porém não é disponibilizado o

código fonte dessas implementações. Portanto uma das

contribuições deste artigo é disponibilizar uma implementação

flexível de FFT, que possa ser usada em grande variedade de

aplicações, bem como para fins de ensino.

Este artigo está organizado da seguinte forma: a Seção II

explica detalhes de como os dados são tratados e seu fluxo

dentro do processador de FFT, a organização de seus blocos

internos e seus pinos de entrada e saída. A Seção III explica

algumas questões de projeto relacionadas ao bloco principal

do projeto. A Seção IV mostra alguns resultados obtidos a

partir da implementação. A Seção V mostra resultados de

desempenho. A Seção VI apresenta algumas conclusões e

trabalhos futuros.

II. IMPLEMENTAÇÃO DO PROCESSADOR DE FFT

O algoritmo usado na implementação em VHDL é o chamado

FFT com radix-2 e decimação no tempo [1]. O termo

decimação no tempo indica que as amostras são ordenadas

antes do cálculo da FFT (ou seja, quando as amostras ainda

estão no domínio do tempo). O algoritmo de ordenação, neste

SOUSA CORREA et al.: VHDL IMPLEMENTATION OF

caso, segue a ordem reversa dos bits da posição de memória

das amostras de entrada. Por exemplo, os bits da posição de

memória “001”, são invertidos, dessa forma será lida a amostra

da posição de memória “100”. Já o termo radix-2 indica que a

DFT foi decomposta em duas operações que são realizadas

paralelamente, as butterflies da FFT serão realizadas usando

duas amostras de cada vez. Decimação no tempo e radix-2 são

termos resultantes das manipulações matemáticas que

transformam a DFT em FFT, primeiramente proposto em [3].

O processador de FFT utiliza ponto fixo como

representação numérica [8]. O número de bits reservado para a

parte inteira e para a parte decimal são parâmetros passados

antes da compilação. Para usar esse tipo de representação

numérica a implementação do processador de FFT usa o

pacote VHDL de ponto fixo chamado IEEE fixed point [9],

que disponibiliza ferramentas para trabalhar com ponto fixo,

bem como operações matemáticas e rotinas de conversão para

outras representações numéricas.

O número de pontos de FFT que o processador

desenvolvido utiliza pode ser especificado antes da

compilação. No atual estágio de desenvolvimento desta

implementação este número deve ser uma potência de 2 e

menor que 512. Essa limitação existe porque é necessário ter

previamente armazenado o conjunto de exponenciais

complexas no código da FFT. Atualmente estão armazenadas

exponenciais complexas para até 512 pontos. Vale destacar

que essa limitação pode ser facilmente resolvida,

desenvolvendo um programa que automaticamente gere um

conjunto de exponenciais para um número maior de pontos.

A descrição do processador de FFT em VHDL adotou a

organização dos componentes internos, mostrado na Fig. 1. As

próximas subseções descrevem as funções de cada um desses

componentes.

Figura 1. Organização interna do processador de FFT.

A. Sinais de entrada e saída

x CLK: é o pino de entrada que serve como sincronizador,

ou base de tempo para o processador.

x RST: é um pino de entrada que reinicia a operação a

qualquer momento. Quando este pino está em nível alto

(nível lógico 1) os registradores são assumem seus

valores iniciais e as máquinas de estados que compõem

os componentes vão para seus estados iniciais.

x START: é um pino de entrada usado para sinalizar ao

1181

processador quando iniciar sua operação.

x RE_DATA e IM_DATA: é um conjunto de pinos de

entrada que representam a parte real e imaginária dos

dados de entrada. O número de pinos é correspondente

ao número de bits dos dados e pode ser alterado antes

da compilação.

Antes de iniciar a transferência dos dados há um

período de inicialização dos componentes internos.

Após esse período, uma amostra é lida e armazenada na

memória interna do processador a cada ciclo de clock.

x RE_OUT e IM_OUT: é um conjunto de pinos de

saída por onde a parte real e imaginária dos dados

resultantes são transferidos. Os dados da memória

interna do processador são transferidos a cada ciclo de

clock.

B. Blocos internos

Esses blocos foram projetados como máquinas de

estados, pois essa técnica permite boa previsibilidade das

questões encontradas no projeto hardware [10].

x INPUT: é o bloco responsável por armazenar os

dados de entrada na memória interna. Ao início da

operação o bloco ARBITER sinaliza para esse bloco

iniciar sua operação. Ele recebe os dados e gera o

endereço correto para armazenar na memória, ou seja,

esse bloco realiza a decimação no tempo. Futuramente

esse bloco será implementado com um protocolo, para

melhorar a portabilidade do projeto.

x BUTTERFLY: esse bloco é o núcleo do processador, ele

é capaz de fazer transformadas de qualquer tamanho.

Mais detalhes sobre este bloco são dados na Seção III.

x OUTPUT: após a execução do algoritmo de FFT esse

bloco inicia o processo de transferência dos dados

resultantes, transferindo um dado por ciclo de clock.

x MEMORY: é composto por dois blocos de

armazenamento, um para a parte real e outro para a

parte imaginária dos dados. Ele foi implementado de

forma que a ferramenta de síntese mapeie o código

automaticamente para a memória interna do FPGA.

Para isso, utilizou-se a ferramenta de síntese chamada

Altera Quartus II [11].

x ARBITER: somente um bloco deve estar em

operação de cada vez. Dessa forma, esse bloco é

responsável por gerenciar os outros blocos com sinais

de início, recebendo seus sinais de término e fazendo o

interfaceamento com a memória. Por exemplo, quando

o pino START está em nível lógico alto o ARBITER

sinaliza para o INPUT iniciar sua operação, e o

ARBITER espera o fim da operação do INPUT. O

mesmo é feito para o bloco BUTTERFLY e OUTPUT.

Durante o tempo que o ARBITER está esperando o

término da operação de um determinado bloco, somente

os sinais de controle daquele bloco serão repassados

para a memória, desse modo somente um bloco está em

operação e somente ele pode acessar a memória.

1182

IEEE LATIN AMERICA TRANSACTIONS, VOL. 10, NO. 1, JAN. 2012

III. MAIS SOBRE AS OPERAÇÕES INTERNAS NO BLOCO

BUTTERFLY

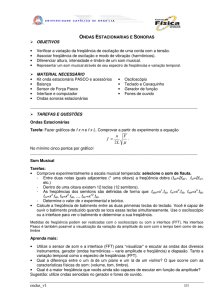

A implementação usando FFT com radix-2 e decimação no

tempo proposta neste artigo resulta no fluxo de dados

mostrado na Fig. 2, na qual é possível observar uma FFT de

oito pontos, sendo que as setas indicam somas e os termos ao

longo das setas são multiplicações. Wxy são exponenciais

complexas na forma e-j2ʌy/x, chamadas de twiddle factor. A

decimação no tempo é também mostrada através da realização

das operações nos dados de entrada seguindo a ordem reversa

dos bits.

256 e 512 pontos, com tamanho de dados de 16 bits, sendo 8

bits para a parte inteira e 8 bits para a parte decimal. Em

ambos os casos utilizou-se o conjunto de twiddle factors,

específico para 512 pontos.

Observou-se que o uso de recursos permanece quase o

mesmo para ambos. Isso acontece porque o bloco

BUTTERFLY continua o mesmo (executa o mesmo

algoritmo), a diferença é que utiliza mais bits para controlar as

operações, pois haverá mais estágios e mais iterações na

execução. O único bloco que significativamente é alterado é o

MEMORY que é dimensionado para armazenar 256 e 512

dados de 16 bits.

A Tabela 1 mostra a porcentagem do uso de recursos das

versões para 256 e 512 pontos, usando o mesmo conjunto de

twiddle factor para ambos.

TABELA 1

RESULTADOS DE SÍNTESE USANDO O FPGA CYCLONE II

EP2C70F896I8 PARA 256 E 512 PONTOS.

V. DESEMPENHO

Figura 2. Uma FFT de 8 pontos usando radix-2 e decimação no tempo.

O algoritmo foi descrito em VHDL como uma máquina de

estados. Dessa forma é possível ter o algoritmo funcional com

as particularidades dos projetos de hardware. Por exemplo, ao

fim de uma operação o resultado é armazenado em um

registrador. Esse resultado estará disponível depois da próxima

subida (ou descida) do clock. Esse comportamento pode ser

modelado como estados de uma máquina de estados, onde em

um estado uma operação é feita e o resultado é preparado para

ser armazenado. Na subida do clock o valor é efetivamente

armazenado e o estado alterado, então no próximo estado o

valor pode ser usado.

O algoritmo FFT é composto por vários estágios e em cada

um desses estágios as operações de butterflies são realizadas.

O número de estágio é o logaritmo base 2 do número de

pontos da FFT.

O bloco BUTTERFLY é independente dos outros e pode

ser adicionado em outro sistema e trabalhar como bloco

interno. Por exemplo, em um sistema onde há um elemento

que armazena dados na memória, o endereço desses dados é

passado para o bloco BUTTERLFY que realiza sua operação e

sinaliza ao término de sua operação, assim os dados resultantes

ficam disponíveis na memória.

IV. RESULTADOS DE SÍNTESE

O processador de FFT foi sintetizado para o FPGA Cyclone

II EP2C70F896I8, usando o software Altera Quartus II. Nesta

Seção os resultados são mostrados para o cálculo de FFT de

Através da ferramenta de síntese Altera Quartus II foi

possível obter informações para calcular a frequência máxima

de clock que o processador de FFT pode operar. A partir da

síntese para o FPGA Cyclone II EP2C70F986I8 foi calculada

a frequência máxima de operação de 43.072 MHz.

A partir dessa máxima frequência de clock, simulações

foram realizadas para verificar o tempo necessário para o

cálculo de uma FFT.

Ao fim da simulação foi obtido o tempo total, para o

processador de FFT completo e somente para o bloco

BUTTERFLY, que foram de 0.7 ms e 0.6 ms,

respectivamente. A Tabela 2 apresenta um resumo dos dados

mostrados nesta Seção.

TABELA 2

ANÁLISE DE DESEMPENHO

VI. CONCLUSÕES

Este artigo apresentou a implementação, os resultados de

síntese e detalhes a respeito das operações internas de um

processador de FFT de propósito geral.

Esse processador de FFT foi desenvolvido para compor um

algoritmo de classificação. Porém devido a sua vasta

SOUSA CORREA et al.: VHDL IMPLEMENTATION OF

aplicabilidade, o mesmo foi desenvolvido para ser genérico e

altamente parametrizável. Trata-se de um código open source

que pode ser utilizado em muitas aplicações além de

classificação, por exemplo, o mesmo código tem sido usado,

pelos autores, em um protótipo de um modem DSL gigabit.

Melhorias nesta implementação já estão sendo realizadas,

objetivando diminuir o tempo de execução. Dentre estas,

destaca-se o uso de outras arquiteturas de butterfly mais

eficientes, como a radix-4. Além disso, o nível de

paralelização pode ser aumentado, através do uso de um

número maior de butterflies (a atual arquitetura utiliza apenas

uma butterfly). Dessa forma, uma futura implementação

poderia ter como parâmetro de configuração o nível de

paralelização, o que afetaria diretamente o uso de recursos e

tempo de cálculo da FFT.

AGRADECIMENTOS

Este trabalho contou com o apoio financeiro do Conselho

Nacional de Desenvolvimento Científico e Tecnológico

(CNPq), Brasil.

REFERÊNCIAS

[1]

Alan V. Oppenheim, Ronald W. Schafer and John R. Buck, DiscreteTime Signal Processing, Prentice Hal, second edition, 1999.

[2] Mandeep Singh Balwinder Singh Pawan Verma, Harpreet Kaur,

“VHDL implementation of FFT/IFFT blocks for OFDM”, International

Conference on Advances in Recent Technologies in Communication

and Computing, 2009.

[3] James W. Cooley and John W. Tukey, “An algorithm for the machine

calculation of complex fourier series”, Math Comput., pp. 297 – 301,

1965.

[4] Volnei A. Pedroni, Circuit Design with VDHL, MIT Press, ISBN 0262-16224-5, 2004.

[5] T. Starr, M. Sorbara, J. M. Cioffi and P. J. Silveramn, DSL Advances,

Prentice Hall, 2003.

[6] Rd. J.; Ordaz-Moreno A.; Vite-Frias, J. A.; Romero-Troncoso, “VHDL

core for 1024-point radix-4 fft computation”, International Conference

on Reconfigurable Computing and FPGAs 2005, ReConFig 2005, pp.

4 – 24, 9 2005.

[7] A. Álvarez-Marquina E. Martinez de Icaya C. Gonzaléz- Consejero, V.

Rodellar and P. Gonzalez-Vilda, “A portable hardware design of a FFT

algorithm”, Latin American Applied Research, 2007.

[8] Randy Yates, “Fixed-point arithmetic: An introduction”, 2009,

http://www.digitalsignallabs.com.

[9] David Bishop, “Fixed point package user’s guide”.

[10] Frank Vahid, Digital Design with RTL Design, VDHL and Verilog,

John Wiley and Sons, second edition, 2011.

[11] Altera, “Altera Corporation”, 2011, http://www.altera.com.

Ilan Sousa Correa was born in Pará, Brazil, on July 25,

1990. He is a student of Computer Engineering at Federal

University of Pará (UFPA). He works at the Laboratory of

Applied Electromagnetism (LEA) and Laboratory of Sensors

and Embedded Systems (LASSE) since 2009, where he has

been developing projects in wireless sensors networks and

digital systems design with emphasis on FPGA.

Lilian Coelho de Freitas received the BSc degree in

Computer Engineering from UFPA (Federal University of

Pará) - Brazil in March 2007. She received the MSc. degree

in Electrical Engineering from UFPA. Nowadays she is doing

a doctorate in UFPA. Since 2003, she has been developing

research in the wireless sensor network area for

environmental and industrial monitoring application. Her research interests

include wireless sensor networks and cognitive radio.

1183

Aldebaro Barreto da Rocha Klautau Júnior received the

Ph.D. degree from the University of California, San Diego, in

2003. In 1995, he was a Faculty Member with the Federal

University of Santa Catarina, Florianópolis, Brazil. Since

1996, he has been with the Federal University of Pará, Belém,

Brazil, where he is affiliated with the Computer Science. He

also directs the Signal Processing Laboratory and the Embedded Systems

Laboratory. His research interests include machine learning for signal

processing, with applications including speech recognition, DSL, power

systems and software/cognitive radio, and the algorithm to its implementation

on ¿eld-programmable gate array or application-speci¿c integrated circuits.

João Crisóstomo Weyl Albuquerque Costa. He received the

title Engenheiro Eletricista - Eletrônico, from the Federal

University of Pará (UFPA), Brazil, in 1981, the Geophysics Pos

Graduated, from the UFPA, Brazil, in 1983, the M. Sc. Degree

(with thesis) in Electrical Engineering (telecommunication) in

1989 from PUC-RJ, Brazil, and received the Doctor in Electric

Engineering degree in Electric Engineering in 1994, from the State University

of Campinas, São Paulo, Brazil. Since 1994 he is with the Federal University

of Pará (UFPA), Brazil, Department of Electrical and Computer Engineering.

Presently, his research areas are the modeling of devices and systems for

optical and mobile communications, including access networks. He is

aresearcher of the Brazilian Research Funding Agency (CNPq) since 1994.