UNIVERSIDADE FEDERAL FLUMINENSE

ANTONIO ADÍLSON FERREIRA e EDUARDO ASSIS SILVEIRA

UM ESTUDO SOBRE PROCESSADORES CELL E GPU:

A ANUCIAÇÃO DA NOVA ERA DA

COMPUTAÇÃO PARALELA

HETEROGÊNEA

Niterói

2007

ANTONIO ADÍLSON FERREIRA e EDUARDO ASSIS SILVEIRA

UM ESTUDO SOBRE PROCESSADORES CELL E GPU:

A ANUCIAÇÃO DA NOVA ERA DA

COMPUTAÇÃO PARALELA

HETEROGÊNEA

Trabalho de Conclusão de Curso submetido ao Curso de Tecnologia em Sistemas de Computação da Universidade

Federal Fluminense como requisito parcial para obtenção do Tecnólogo em Sistemas de Computação.

Orientador:

Leandro Soares de Sousa

NITERÓI

2007

ANTONIO ADÍLSON FERREIRA e EDUARDO ASSIS SILVEIRA

UM ESTUDO SOBRE PROCESSADORES CELL E GPU:

A ANUCIAÇÃO DA NOVA ERA DA

COMPUTAÇÃO PARALELA

HETEROGÊNEA

Trabalho de Conclusão de Curso submetido ao Curso de Tecnologia em Sistemas de Computação da Universidade

Federal Fluminense como requisito parcial para obtenção do Tecnólogo em Sistemas de Computação.

Niterói,18 de Dezembro de 2007.

Banca Examinadora:

•

Prof . Anna Dolejsi Santos, Dr.Sc. - Universidade Federal Fluminense

•

Prof. Leandro Soares de Sousa, Msc. - Universidade Federal Fluminense

•

Prof . Talita de Oliveira Ferreira, Msc. – Universidade Federal do Rio de Janei-

ro

a

a

Dedicamos aos nossos pais, responsáveis primeiros pelas dádivas das concepções de nossas vidas.

Às empresas AMD, IBM, INTEL e

NVIDIA assim como o LANL Los Alamos Lab pela generosidade em

tornar público, em seus sítios na Internet,

informações vitais para todos sobre o assunto em questão.

Aos institutos MIT, GeogeTech e à universidade de Stanford pelos materiais de

cursos online.

AGRADECIMENTOS

A Deus, que ilumina todos os caminhos.

A nosso Orientador Leandro Soares de Sousa

pelo estímulo e atenção que nos concedeu

durante o curso.

Às coordenadoras Marta e Rosana do Pólo

de Angra dos Reis do CEDERJ

por seus

enormes e solidários préstimos.

Aos colegas de trabalho pelo apoio e suporte:

Anis, Jorge e Waldirio (Windows); Leandro

(Linux); e Paulo (CELL e GPU).

Ao Paulo Fernando pelo enorme espírito democrático,

liderança

nata

e

profissional,

incentivador da educação e cultura.

Às nossas esposas e aos nossos filhos.

“Quem não soube a sombra, não sabe a luz.”

Taiguara Chalar da Silva

“O estilo é uma dificuldade de expressão.”

Mário Quintana

“Agente vai contra a corrente, até não poder resistir.

Na volta do barco é que sente, o quanto deixou de

cumprir”.

Chico Buarque de Holanda, em Roda Viva, 1967.

“Muitos escritores novos dizem que seu maior problema é saber por onde começar. Não é. O maior

problema de quem escreve (ou compõe, ou interpreta, ou, principalmente, discursa) é saber onde parar.”

Luis F.Veríssimo em “Robinho e o Paradoxo”, O Globo, 1/7/7

“To put it quite bluntly: as long as there were no machines, programming was no problem at all; when

we had a few weak computers, programming became a mild problem, and now we have gigantic

computers, programming has became an equally gigantic problem.”

E. Dijkstra.

Turing Award, 1972.

RESUMO

Este trabalho descreve a origem do multicore e as tendências em computação paralela heterogênea de alto desempenho. Especialmente arquiteturas como

GPUs e o processador CELL da IBM, que são o nosso principal alvo de estudo.

Fornecemos alguns detalhes de especificações e implementações do

hardware e software para estas arquiteturas bem como suas aplicações em diversas

áreas de atuação. Nos aprofundamos principalmente na computação de alto desempenho, no processamento gráfico e de multimídia.

Detalhamos muitas características, tecnologias envolvidas, programação,

mercados de atuação e propostas para novos processadores gráficos, GPUs, e uma

nova abordagem para processadores com múltiplos núcleos, heterogêneos, com

rede interna e arquitetura SMP, com modelo de programação paralela heterogênea,

como tendência tecnológica a ser consolidada.

Descrevemos e detalhamos o porquê da tecnologia multicore, e os fundamentos teóricos motivados inicialmente pela Lei de Moore, que ainda vigora mas talvez não vigorará devido aos limites impostos pela Física e estabelecidos pela Mecânica Quântica, que inviabilizam os processos de fabricação atual da eletrônica digital

baseado na tecnologia CMOS para processadores de computador e que, possivelmente, serão repensados e redirecionados para uma nova tecnologia.

Comentamos sobre os paradigmas da computação atual tanto nos processos de fabricação tecnológicos, com tecnologia CMOS, quanto o de programação seqüencial com a programação serializada e algumas das novas tendências tecnológicas de hardware e software.

Mostramos as tendências atuais de fabricação de processadores com

múltiplos núcleos, homogêneos e heterogêneos, associados à computação paralela

heterogênea de alto desempenho e as novas tecnologias candidatas à substituição

da tecnologia CMOS, em especial a Spintrônica como sendo a melhor posicionada.

Palavras-chaves: CELL, COMPUTAÇÃO HETEROGÊNEA, GPU, GPGPU, HPC,

MULTICORE, PROCESSADOR, PROGRAÇÃO PARALELA, SPINTRÔNICA.

LISTA DE ILUSTRAÇÕES

Figura 1: Evolução do processos de fabricação de processadores até 2.012...........29

Figura 2: Evolução da potência consumida das CPUs x performance escalar..........30

Figura 3: Limitações físicas inviabilizam o aumento das freqüências........................31

Figura 4: O multicore como solução para as limitações impostas pela Física...........32

Figura 5: Consumo crescente de potência nos últimos 20 anos................................33

Figura 6: A inexorável jornada para o multicore.........................................................34

Figura 7: Evolução da bitola equivalente do fio em ciclos de máquina......................35

Figura 8: Processador single core: em extinção.........................................................36

Figura 9: O singlecore tende a extinção. O multicore floresce...................................37

Figura 10: Problema fundamental: alta dissipação térmica........................................38

Figura 11: Aquecimento das CPUs.............................................................................38

Figura 12: A gênesis do problema está na Física.......................................................39

Figura 13: A inviabilidade de se aumentar a freqüência indefinidamente..................40

Figura 14: A história se repete ou nós já vimos isto ocorrer anteriormente...............41

Figura 15: As diminutas dimensões do processador CELL........................................42

Figura 16: GPUs de mercado: Nvidia Quadro FX 5600 e ATI (AMD) R600.........44

Figura 17: Acelerada evolução do poder computacional das GPUs..........................49

Figura 18 Diagrama de blocos das unidades de processamento das GPUs............56

Figura 19: Características gerais de um CELL...........................................................59

Figura 20: Fotografia da pastilha de um processador CELL.....................................63

Figura 21 Jogos de mercado: Sony PS3, Microsoft Xbox 360 e Nintendo Wii..........70

Figura 22: Cluster Linux de IBM CELL com Sony PS3...............................................88

Figura 23: Lâminas de CELL e IBM CELL Blade Center QS20 ................................89

Figura 24: Instalações típicas de clusteres Linux Beowolf.........................................89

Figura 25: Ambiente Teste: Sun + NV FX 5600 + cluster PS3 + switch Gig E........91

Figura 26: IBM BlueGene/P........................................................................................94

Figura 27: Logo do projeto RoadRunner.....................................................................96

Figura 28: Distintas abordagens e direções na busca do PetaFLOPS......................97

Figura 29 O processador CELL, peça fundamental do projeto RoadRunner............98

Figura 30 Em apenas 18 racks , 7.000 CPUs e 13.000 CELLs : 1 PetaFLOPS......99

Figura 31 Arquiteturas distintas com duas CPUs físicas distintas...........................100

Figura 32 Um exemplo marcante de heterogeneidade............................................103

Figura 33 O futuro imita o passado..........................................................................105

Figura 34

Tributo a Gordon Moore...........................................................124

LISTA DE TABELAS

Tabela 1 Exemplos de processadores multicore....................................................... 43

Tabela 2 Características gerais de alguns processadores multicore ......................... 43

Tabela 3 Algumas aplicações para GPGPUs............................................................. 54

Tabela 4 Tipos de operações em GPU e localização de ocorrência ......................75

Tabela 5 Exemplo de limites superiores para GPU..................................................75

Tabela 6 Acesso á memória pelo tipo específico de memória .................................. 78

Tabela 7 Característica de cada memória de uma moderna GPU ............................80

LISTA DE GRÁFICOS

Gráfico 1 Evolução do número de transistores nos microchips Intel no tempo.......124

LISTA DE ABREVIATURAS E SIGLAS

AMD

-

Advanced Micro Devices

ANSI

-

America National Standard Interchange

API

-

Application Program Interface

ATI

-

ATI Fabricante de GPUs e Placas de Vídeo (AMD)

BW

-

Broadband With

CDC

-

Control Data Corporation

CEDERJ

-

Centro de Educação Superior à Distância do RJ

CELL BE

-

CELL Broadband Engine

CMOS

-

Complementary Metal-Oxide-Semiconductor

CPU

-

Central Processor Unit

CTM

-

Close to The Metal

CUDA

-

Computer Unified Development Architecture

DD

-

Data Definition

DDR2

-

Double Data Rate 2

DMA

-

Direct Memory Access

DP

-

Double Precision

DRAM

-

Dynamic Read Access Memory

EIB

-

Element Interconnected Bus

FFT3D

-

Fast Fourier Transform 3D

FLEXIO

-

Flexible Input Output

FORTRAN

-

Formula Translator

FPAP

-

Floating Point Array Processor

FPGA

-

Field-Programmable Gate Array

FPS

-

Floating Point System

GDB

-

GNU Debugger

GEOGIATECH

-

Georgia Technology Institute

GF

-

Giga Flops

GFLOPS

-

Giga Floating Point Operations Per Second

GNU

-

Gnu is Not Unix

GTS

-

Modelo de GPU da Nvidia

GTX

-

Modelo de GPU da Nvidia

HPC

-

High Performance Computing

HT

-

Hyper Transport

HTX

-

Hyper Transport Extended

I/O

-

Input-Output

I486

-

Intel Architecture 80486

IBM

-

International Business Machine

IBM BLUE GENE

-

A PetaFLOPS supercomputer of IBM

IBM ES9000

-

A mainframe Enterprise System of IBM

IBM POWER

-

Workstation Technology from IBM

INTEL

-

Intel Corporation

JCL

-

Job Control Language

LANL

-

Los Alamos National Laboratory

LCM/SCM

-

Small Fast Core Memory / Large Core Memory

LLNL

-

Lawrence Livermore National Laboratory

MASS

-

Mathematical Application Statistical Subroutines

MIPS

-

Old Manufacturer of Processors

MIT

-

Massachussetts Institute of Technology

MPI

-

Message Passing Interchange

NVCC

-

Nvidia C Compiler

NVIDIA

-

Manufacturer of GPUs

OPENMP

-

Free Library of Message Passing Open

PC

-

Personal Computer

PCI EXPRESS

-

Peripheral Card Interface model Express 16x

PDA

-

Personal Digital Assistants

PPE

-

Power Processor Element

PPU

-

Power Processor Unit

PS3

-

Sony Game Play Station 3

RAM

-

Read Access Memory

RED HAT WS

-

Linux Operating System for Workstation

ROAD RUNNER

-

HPC Project of Los Alamos National Lab

RPC

-

Request Procedure for Comments

SCEI

-

Sony Computer Entertainment Inc.

SDK

-

Software Development Kit

SGI

-

Silicon Graphics Inc.

SIMD

-

Single Instruction Multiple Data

SM

-

Single Multiprocessor

SMP

-

Symmetric Multi Processor

SOI

-

Silicon Over Insulator

SP

-

Single Precision

SPE

-

Synergetic Processor Element

SSE

-

Internet Streaming SIMD Extensions

STANFORD

-

Stanford University

STI

-

Joint Venture Sony-Toshiba-IBM

TFLOPS

-

Tera Floating Point Operations Per Second

TSUBAME

-

A supercomputer of Japan

WII

-

A Game of Nintendo Manufacturer

X86_64

-

Architecture based in Intel 80486 processor

XBOX360

-

A Game of Microsoft Corporation

XDR

-

Memória Rambus

XEON

-

Processador Intel x86_32, x86_64 bits

SUMÁRIO

RESUMO......................................................................................................................7

LISTA DE ILUSTRAÇÕES...........................................................................................8

LISTA DE TABELAS.................................................................................................. 10

LISTA DE GRÁFICOS................................................................................................11

LISTA DE ABREVIATURAS E SIGLAS..................................................................... 12

SUMÁRIO...................................................................................................................15

1 INTRODUÇÃO........................................................................................................ 16

2 HISTÓRICO..............................................................................................................18

3 OS PROCESSADORES MULTICORE.................................................................... 20

3.1 CONCEITOS PRELIMINARES......................................................................... 20

3.2 A EVOLUÇÃO DO SINGLECORE................................................................... 22

3.2.1 Os limites da tecnologia singlecore........................................................... 23

3.3 A TECNOLOGIA MULTICORE........................................................................ 24

3.3.1 Arquiteturas Multicore............................................................................... 26

4 O PORQUÊ DA TRANSIÇÃO PARA O MULTICORE.............................................27

4.1 TAXONOMIA DOS MULTICORES...................................................................42

5 GPU..........................................................................................................................44

5.1 FUNÇÕES COMPUTACIONAIS...................................................................... 45

5.2 GPGPU............................................................................................................. 46

5.2.1 Conceitos de Programação em GPGPU.................................................... 47

5.3 PORQUE USAR GPGPU?............................................................................... 48

5.4 TÉCNICAS GPGPU..........................................................................................50

5.4.1 Classificação das operações das GPUs....................................................50

5.5 ESTRUTURA DE DADOS................................................................................53

5.6 APLICAÇÕES EM GPGPU.............................................................................. 53

5.7 DIAGRAMA DE BLOCOS DA GPU..................................................................54

5.8 PRINCIPAIS LINGUAGENS PARA USO EM GPUs........................................56

6 CELL.........................................................................................................................57

6.1 UMA HISTÓRIA ROMÂNTICA ......................................................................... 57

6.2 DA IMAGINAÇÃO À REALIDADE....................................................................57

6.3 DISPOSITIVOS DE VETORIZAÇÃO DO CELL................................................64

6.4 DESENVOLVIMENTO PARA O CELL.............................................................66

6.5 É O PROCESSADOR CELL DE FIM GERAL?................................................67

6.6 A ARQUITETURA RISC ATACA NOVAMENTE..............................................68

7 DIFERENÇAS ENTRE O PROCESSADOR CELL E GPUs....................................69

8 RUDIMENTOS DE SOFTWARE PARA GPUs........................................................ 72

8.1 A ARQUITETURA CUDA COMO PADRÃO PARA GPU..................................73

8.2 CONCLUSÃO SOBRE A ARQUITETURA CUDA EM GPU............................. 76

8.3 UMA IMPLEMENTAÇÃO CUDA NO HARDWARE G80...................................78

8.4 IMPLEMENTAÇÃO DA ARQUITETURA DE MEMÓRIA - G80........................78

8.5 SÍNTESE DO MODELO DE HARDWARE dA G80..........................................79

8.6 APIs PARA GPUs..............................................................................................80

8.7 COMPILAÇÃO EM CUDA................................................................................. 82

8.8 LINK-EDIÇÂO EM CUDA.................................................................................. 82

8.9 DEPURAÇAO EM CUDA.................................................................................. 83

8.10 A NOVA ARQUITETURA DE DESENVOLVIMENTO EM GPUS...................84

9 RUDIMENTOS DE SOFTWARE PARA CELL........................................................85

10 USO DE GPUs E DE CELL NO AMBIENTE HPC................................................86

11 UMA EXPERIÊNCIA PRÁTICA COM GPUS E CELL........................................... 90

12

A COMPUTAÇÃO DE PETAFLOPS...................................................................93

12.1 SISTEMAS DE COMPUTAÇÃO HÍBRIDA ESTÃO CHEGANDO.................101

12.2 “DEJA VU” (PARECE QUE A HISTÓRIA SE REPETE).............................. 104

13 TECNOLOGIAS ALTERNATIVAS A SUBSTITUIÇÃO DO CMOS.....................106

13.1 A EVOLUÇÃO DAS TECNOLOGIAS DOS TRANSISTORES.....................106

13.2 LIMITES de TRANSISTORES na TECNOLOGIA MOSFET........................108

13.3 AS FUTURAS TECNOLOGIAS QUE SE APRESENTAM...........................109

1.1.1Tecnologia de Diodos Ressonantes de Tunelamento ...............................109

1.1.2AUTÔMATOS CELULARES QUÂNTICOS (QCA)....................................110

1.1.3Nanoeletrônica Molecular.......................................................................... 110

1.1.4SPINTRÔNICA...........................................................................................111

14 CONCLUSÕES................................................................................................... 113

REFERÊNCIAS BIBLIOGRÁFICAS........................................................................118

ANEXOS...................................................................................................................122

ANEXO A - LEI DE MOORE.................................................................................... 123

ANEXO B - PRINCÍPIO DA INCERTEZA DE HEISENBERG................................. 128

1

INTRODUÇÃO

O objetivo fundamental deste trabalho é de apresentar duas mais importantes tecnologias de processadores da atualidade, CELL e GPU, que despontam e

disputam as preferências técnico-científica, comercial e de público para uma enorme

gama de aplicações tais como: jogos, computação gráfica e computação de alto desempenho. Ele foi elaborado fundamentalmente através de vários cursos

on-line

disponibilizados pelos fabricantes IBM, Nvidia, Intel e instituições científicas como

MIT, Los Alamos Lab, Geogia Tech, Stanford University, dentre outras, aliado a muitos trabalhos publicados e informações também disponibilizadas na Internet. A motivação básica reside na necessidade de se ter acesso e disponibilidade de computa ção de altíssimo desempenho e a um baixo custo, ou seja, TeraFLOPS por centenas

de dólares. Este trabalho não é original nem tem a pretensão de sê-lo, pois procurou

extrair aquilo que considerarmos ser de melhor na bibliografia e em todas as referên cias encontradas. A maior dificuldade foi exatamente a escolha e ordenação do conteúdo, imagens, gráficos e figuras, bem como o texto e a ordenação do mesmo

numa modesta tentativa de conduzir o leitor de tal forma que este possa ter uma re ferência e um roteiro significativos na língua nacional sobre o tema e, de posse destes, possa guiar-se e enveredar pelo conhecimento nesta área.

O despertar do século XXI traz boas novas em termos tecnológicos e, em

particular, novíssimas arquiteturas de processadores para enfrentar o desafio imposto pelas necessidades econômicas de baixos custos e ambientais, de melhor e mais

racional uso dos recursos energéticos aliados à requisição de processadores muito

mais velozes. Em especial, no que tange a computação de alto desempenho, objeti vando apresentar e resolver várias aplicações como processamento de imagens, si mulações, cálculos científicos, pesquisas em biologia, química, física e medicina,

processamento sísmico e pesquisas espaciais entre tantas outras. A restrição tecno-

17

lógica fundamental reside nas limitações impostas para consumo de energia e necessidades de refrigeração dos processadores devidos ao enorme consumo e desperdício, provenientes da dissipação de calor, além do grande espaço físico para

acomodar os equipamentos e os altíssimos custos de aquisição, manutenção e garantia dos mesmos.

Estamos vivendo num momento nitidamente propício para a ruptura do

paradigma vigente de computação e programação numa busca de um novo paradigma. No paradigma atual, a computação homogênea, isto é, aquela baseada em processadores com um ou mais núcleos homogêneos idênticos e de mesma natureza

como, por exemplo os dos fabricantes Intel ou AMD de um único núcleo (singlecore),

dois núcleos (dualcore), quatro núcleos (quadcore), oito núcleos (octocore) [10], etc; e,

a programação seqüencial (baseadas em programas compostos por instruções que

são executadas passo a passo, seqüencialmente) é seu carro-chefe. Nesta nova

era que se vislumbra e que se estabelecerá definitivamente nos próximos dez ou

vinte anos, os computadores heterogêneos multicore (baseado em múltiplos núcleos

distintos) e a programação paralela (“de pedaços das linhas de códigos a serem

executados sequencialmente” ou “um fluxo de controle sequencial isolado dentro de

um programa” – threads – sendo executados em paralelo pelos distintos núcleos do

processador)

[17]

reinarão hegemônicos e, motivados pelas

de necessidades de

computação de alto desempenho e baixos custos, estarão disponíveis para a grande

maioria dos usuários em seus próprios desktops, notebooks, laptops, e nos novos

dispositivos de tecnologia convergente que se apresentarão, permitindo que a computação de teraflops (trilhões de operações de ponto flutuante por segundo) fique à

disposição de todos por custos muito baixos.

Duas das tecnologias representantes desta verdadeira revolução, que se

configura, podem ser identificadas nos processadores gráficos (GPUs) e nos processadores heterogêneos multicore (IBM CELL, por exemplo), ou, também, nos multicore homogêneos (com microarquitetura x86_64 dual, quad, octocore da Intel ou AMD)

[7,10]. Por considerar este tema apaixonante e excitante, modestamente discorreremos em particular sobre estas duas tecnologias e alguns tópicos relacionados ao

tema da computação de alto desempenho, computação paralela e os novos desafios

delas decorrentes.

18

2 HISTÓRICO

No último quarto do século XX, observou-se uma desenfreada e frenética

competição na corrida pelo aumento da freqüência do clock, ou seja, da velocidade

de operação, dos processadores como o modo mais simples de se obter o aumento

de desempenho dos computadores. Desde os 4.77 MHz do IBM PC original lançado

em agosto de 1981

[1,2]

Xeon ou AMD Opteron

até os 3.4 GHz dos monoprocessados e singlecore Intel

[7,10]

ou, a impressionante freqüência de 4.7 GHz do IBM

Power 6 dualcore [3], a corrida parece ter chegado ao seu limiar. Limiar este que esbarrou nos limites decorrentes das propriedades físicas dos materiais envolvidos e

de suas dimensões físicas, que definiram uma barreira intransponível para os fabricantes de processadores. Dos fabricantes de processadores apenas a IBM segue

em frente, imediatamente, com freqüências de clocks além de 4 GHz

[5]

como, por

exemplo, o seu já citado IBM Power6 que, em sua versão comercial de 2007, pode

operar em até 4.7 GHz ou 4.2 GHz ou 3.7 Ghz [3], como possibilidades de atingir algo

próximo a 6 Ghz

[4]

em versões futuras, segundo o próprio fabricante, mas por um

custo altamente proibitivo para a maioria dos usuários. Do ponto de vista tecnológico, o custo não é relevante, o que importa é possibilidade de ultrapassar os limites

anteriores com inovação tecnológica e pesquisa de novos materiais e propriedades

destes para obtenção das metas, mas do ponto de vista econômico-financeiro, é importantíssimo o baixo custo, para uma possível produção em massa e a disseminação dos benefícios da tecnologia para um maior número possível de pessoas e sistemas.

As atuais e futuras necessidades computacionais passam diretamente

pela obrigatória ruptura com o estabelecido, isto é, dadas as barreiras e restrições

de energia finita, espaço exíguo e refrigeração também finita, não se pode ou poderá

conceber arquiteturas computacionais gulosas e ineficientes nestes pontos de vista.

A mitigação dos recursos energéticos, principalmente, aliada a impossibilidade de se

elevar o clock dos processadores a níveis além dos atualmente alcançados (que já

atingiu um ponto de temperatura equivalente ou próximo do ponto das reações nucleares e que, se levado avante, alcançaria a temperatura da superfície solar –

19

10.000 graus centígrados), conforme mostram, respectivamente, as Figuras 10 e 11,

induzindo obrigatoriamente a uma mudança tecnológica. Esta mudança, pelas razões anteriores e por outras que detalharemos mais à frente, implicou na tecnologia

multicore

[18]

por um lado e por outro, como fruto da natural evolução tecnológica dos

conceitos de co-processador matemático dedicado, de uma outra tecnologia: processadores gráficos (GPU)

, aplicados inicialmente à computação gráfica e atualmen-

[11]

te com incursões na área da computação de alto desempenho.

As GPUs encontraram um rico e profícuo ambiente de altos e relevantes

investimentos no mercado de jogos eletrônicos e na indústria do entretenimento formada pelos desenhos em 3D, sofisticadas texturas, computação física, etc. O mercado de jogos eletrônicos primordialmente é o principal mote da evolução tecnológica das GPUs, representando bilhões de dólares de faturamento, o que permitiu maiores investimentos nesta tecnologia e um alto nível de capitalização dos fabricantes

de GPUs, tendo o fabricante Nvidia [9] como o maior e melhor representante como

poder comprovado por seus balanços financeiros e valorização de suas ações no

mercado de capitais.

Por outro lado, grandes fabricantes de computadores e produtos de consumo do mercado de eletro-eletrônico, em defesa de seus interesses, uniram-se

numa parceria batizada como IBM STI (Sony, Toshiba e IBM) no despertar deste,

que será um luminoso século, para definir aquilo que se espera que não seja apenas

uma evolução da tecnologia existente aplicada a um nicho de mercado, como o da

computação gráfica ou jogos eletrônicos, mas para a computação de fim geral e

também aplicável em problemas mais específicos. Especialistas da IBM denominam

esta evolução de “A vingança da arquitetura RISC” [21]. Esta parceria gerou como

fruto o IBM CELL Broadband Engine, o CELL BE, a qual detalharemos nos capítulos

seguintes bem como a também o faremos com relação a GPU (Graphical Processor

Unit).

20

3 OS PROCESSADORES MULTICORE

3.1

CONCEITOS PRELIMINARES

As principais partes dos processadores convencionais são

1 – Núcleo

(em inglês, Core):

[22]

:

local onde as instru-

ções são executadas. Ou seja, é aqui que as coisas realmente acontecem. Que tipo

de coisas?

Execução de instruções, cálculos, etc.

2 – Cache:

é uma memória que se encontra dentro

do processador. Ao invés de termos o processador indo buscar dados na memória

principal o tempo todo, aplicando-se o Princípio da Localidade

[23]

, ele possui uma

memória interna onde os dados são armazenados temporariamente. O processador

procura por um dado primeiramente dentro de sua memória cache antes de ir buscar

o dado na memória principal. Por este motivo, o cache também influencia no desempenho do processador. Resumindo, cache é uma pequena quantidade de memória

estática de alto desempenho, tendo por finalidade aumentar o desempenho realizando uma busca antecipada na memória RAM. A taxa de acerto típica é de 80% a 90%

[11]

.

Note-se que a palavra Núcleo em inglês é Core. Quando colocamos dentro de um processador mais do que um núcleo, ele se torna um processador Multi-N úcleos ou MultiCore.

No caso dos processadores que possuem dois núcleos, eles são chamados de DualCore. Qualquer que seja o processador, quando ele for identificado

21

como sendo Dual Core, terá dois núcleos de execução. Quando os processadores

DualCore começaram a aparecer no mercado

, dizia-se que tínhamos colocado

[24]

dois processadores em um. Isso não é verdade mas serve muito bem como analogia. Há também, os processadores que possuem 4 (quatro) núcleos. Esses processadores são chamados de QuadCore e estão presentes hoje em desktops e servidores. Tanto a empresa Intel como a sua concorrente em arquiteturas x86, fabricam

processadores dualcore e quadcore disponíveis no mercado como, por exemplo,

Intel Xeon Core Duo (para laptops e desktops), Intel Xeon Quad Core (para servidores), AMD Opteron Dual Core, AMD Opteron Quad Core. Os processadores IBM

Power5+ e IBM Power 6 são dualcore [8]. Existem também, no mercado, processadores com 8 núcleos como o Sun T1

[25]

ou de 9 (nove) núcleos como o IBM CELL

[26]

,

que está incorporado nas consoles de jogos Sony PS3 e outros com muitos núcleos, ditos manycores ainda não comercializáveis ou em testes nos laboratórios dos

fabricantes como o Octocore da Intel, o Octocore da AMD, o MIT Raw (16 núcleos),

etc.

Existem processadores ainda não comerciais como o Intel Larrabee de 80

(oitenta) núcleos ou outros em desenvolvimento, como na universidade de Tókio

com 512 núcleos denominado Grape DR e destinado à computação de alto desempenho (HPC) [30].

A existência de vários núcleos dentro dos processadores é uma tendência

e deve-se esperar que a quantidade de núcleos cresça para além dos quatro existentes hoje como os vistos no parágrafo anterior. Colocar vários núcleos dentro de

um processador foi uma das formas encontradas para se aumentar ainda mais o seu

desempenho. Isto gerou uma quebra de paradigma (tabú). O desempenho dos processadores sempre foi definido simplificadamente pelo clock (freqüência de operação do processador), ou o popular GHz (gigahertz, ou seja, tendo hertz como unidade de medida de freqüência). Esta foi uma boa medida durante muito tempo. Quando vamos para processadores com múltiplos núcleos, a coisa muda de figura. Processadores com dois núcleos e com freqüência de clock menor possuem desempenho superior a processadores com um único núcleo trabalhando a uma freqüência

22

maior. Ou seja, ao analisarmos o desempenho de processadores não devemos considerar a freqüência do clock como o único e exclusivo indicador de desempenho.

Os processadores têm um ou mais núcleos e uma ou mais memórias cache. Internamente, o núcleo ainda é subdividido em vários componentes. A forma

como os elementos internos do núcleo estão dispostos, como eles irão se comunicar, a maneira como o cache será acessado, como as instruções serão executadas

– serializadas ou em paralelo - etc, tudo isso define o que chamamos de Microarqui tetura. É a partir de uma concepção de Microarquitetura que os processadores são

criados. Os processadores criados a partir de uma mesma Microarquitetura terão as

mesmas características básicas, apesar de poderem ter pequenas alterações para

funcionamento em desktops, notebooks ou servidores devido às particularidades distintas de cada um destes como dimensão física, alimentação, autonomia, robustez,

etc. Porque uma Microarquitetura é importante? A mudança de uma Microarquitetura

pode fazer com que uma nova geração de processadores atinja um desempenho

(performance) muito melhor e consiga, por exemplo, ter um consumo muito menor

de energia, como é a proposta dos multcores: IBM CELL (9 cores e heterogêneo: 1

PPE e 8 SPEs)

[28]

; e os homogêneos Intel Larrabee (80 cores), Sun T1

(octocore) [27], AMD Barcelona (quadcore), Intel Xeon (quadcore) [10], etc.

3.2

A EVOLUÇÃO DO SINGLECORE

Os processadores multicore representam uma grande revolução da tecnologia computacional. São capazes de prover maior capacidade de processamento

com uma relação entre custo e benefício melhor do que os processadores singlecore. São uma resposta científica às crescentes demandas por desempenho e uma

forma de contornar as limitações impostas pela Física para os processadores singlecore, preservando o paradigma vigente da tecnologia CMOS.

23

3.2.1

OS LIMITES DA TECNOLOGIA SINGLECORE

As demandas de complexas simulações 3D, arquivos de streaming media, níveis adicionais de segurança, interfaces do usuário mais sofisticadas, bancos

de dados mais robustos e cada vez mais e mais usuários conectados on-line estão

sempre requisitando por maior poder de processamento. A solução aplicada até

agora, de maneira simplificada, foi aumentar a freqüência de operação dos processadores, aumentando-se assim a sua capacidade de processamento. Isto exige que

o processo de fabricação de transistores seja feito em camadas de silício cada vez

menos espessas. Entretanto, este método de fabricação tem seus dias contados

[28]

o que obriga a busca de uma tecnologia alternativa para a fabricação de circuitos integrados e, com eles, microprocessadores.

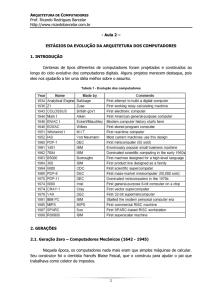

Conforme Figura 1, podemos verificar que as tecnologias de fabricação

de 90 nm com espessura de porta de 50 nm, e as seguintes deverão ter sua exaus tão lá pelos idos de 2012, conforme previsões dos cientistas das empresas fabricantes de processadores. Isto porque, quanto menor for à largura da porta mais próxima

as regiões da fonte e do dreno do transistor ficarão. Pelas leis da Física Quântica,

quando a largura da porta atingir a 5 nm, a fonte e o dreno ficarão separados por um

trecho de silício tão pequeno que não se conseguirá isolá-los completamente, gerando uma probabilidade de 50% de que a corrente flua mesmo quando não houver ten são aplicada à porta (este fenômeno denomina-se na Física Quântica de tunelamento do elétron). Quando isto ocorre, o transistor deixa de ser confiável como dispositivo de processamento de dados pois passamos a não ter mais controle sobre seu

comportamento ou propriedades

[28,29]

. Além disso, temos outro problema ainda mais

grave: a dissipação de energia em forma de calor. Devido à miniaturização dos novos processos de fabricação de circuitos integrados, cada vez mais se fabricam processadores com mais e mais transistores equivalentes em menores áreas do chip.

Quanto menores são os transistores do circuito integrado, maior sua “densidade superficial” , ou seja, o número de transistores por unidade de área. O acúmulo de um

número muito grande de transistores numa área tão pequena concentra tremenda-

24

mente a produção de calor devido à dissipação de energia pela corrente elétrica

que circula nos transistores (dada pela Lei de Joule:P = i2 R)

[31]

. Se essa energia

não for rapidamente removida do circuito e transferida para o ambiente, o chip atingirá temperaturas tão elevadas que, literalmente, derreterá

[32]

. As Figuras 10 e 11,

respectivamente, mostram a evolução da energia dissipada por processador.

Afirmam os cientistas que, mesmo que se conseguisse contornar o limite

da largura de porta, não haveria como remover o calor do processador com a mesma velocidade com que ele seria produzido. O chip se autodestruiria [22].

Além dessas, há diversas outras limitações impostas pela arquitetura de

núcleo único. Entre elas, temos que a estreita banda de dados, aliada a grande diferença entre a velocidade do processador e a da memória, faz com que 75% do tem po da CPU, em média, seja gasto esperando por resultados dos acessos à

memória [33].

3.3

A TECNOLOGIA MULTICORE

A tecnologia multicore (múltiplos núcleos) consiste em colocar duas ou

mais unidades de execução (cores) no interior de um único “pacote de processador”

(um único chip). O sistema operacional trata esses núcleos como se cada um fosse

um processador diferente, com seus próprios recursos de execução. Na maioria dos

casos, cada unidade possui seu próprio cache e pode processar várias instruções simultaneamente.

Adicionar novos núcleos de processamento a um processador possibilita

que as instruções, das aplicações, sejam executadas em paralelo em vez de serialmente, como ocorre em um único núcleo (considerando um único pipeline de execução - pipeline é uma técnica de hardware que permite que a CPU realize a busca de

uma ou mais instruções além da próxima a ser executada

[11]

).

25

Os processadores de múltiplos núcleos permitem trabalhar em um ambiente multitarefa. Em ambientes de um só núcleo, as funções de multitarefa podem

ultrapassar a capacidade da CPU, o que resulta em queda de desempenho enquanto as operações aguardam serem executadas. Em sistemas de múltiplos núcleos,

como cada núcleo tem seu próprio cache, o sistema operacional dispõe de recursos

suficientes para lidar com o processamento intensivo de tarefas executadas em pa ralelo. Portanto, melhora-se a eficiência do sistema como um todo e o desempenho

dos aplicativos, em computadores que executam vários aplicativos simultaneamente. A presença de vários núcleos é particularmente eficaz quando uma das aplica ções deve ficar sendo executada continuamente (ou quase), como no caso dos dispositivos das consoles gráficas de jogos, nos dispositivos de convergência digital

(som, vídeo, etc), entre outros.

As principais vantagens da arquitetura multicore são:

1. Maior eficácia (throughput) do sistema e desempenho aprimorado

de aplicativos em computadores que executam vários aplicativos

simultaneamente.

2. Desempenho aprimorado para aplicativos multi-threaded.

3. Maior capacidade para mais usuários ou tarefas em aplicativos

com muitas transações.

4. Desempenho superior em aplicativos que utilizem processamento

de forma intensiva.

5. Economia no preço do licenciamento de software proprietário, passando a ter um maior poder de processamento sem necessitar de

uma nova máquina (os fabricantes de software podem rever suas

políticas de comercialização de licenças de software por processador para core, minimizando esta vantagem).

6. Redução da dissipação térmica quando comparado ao singlecore.

26

3.3.1

ARQUITETURAS MULTICORE

Uma arquitetura multicore é, geralmente, um multiprocessamento simétrico (SMP) implementado em um único circuito VLSI (Very Large Scale Integrated). O

objetivo é melhorar o paralelismo no nível das threads, ajudando especialmente as

aplicações que não conseguem se beneficiar dos processadores superescalares

atuais, por não possuírem um bom paralelismo ao nível de instruções. Essa arquite tura propicia o chamado paralelismo em nível de chip. Algumas de suas vantagens

são: melhor localidade de dados se comparado com outras arquiteturas de multi-processamento; melhor comunicação entre as unidades; economia de espaço e ener gia. É importante observar que o aumento de throughput não ocorre ao acaso da

execução de uma única aplicação que não possa ser paralelizada, mas, nos outros

casos, e sempre que se considera o sistema como um todo (rodando várias aplicações simultaneamente), tal aumento é bastante notável. Com todas essas vantagens, os multicores apresentam uma melhor relação custo / benefício do que os singlecore.

Uma alternativa ao multiprocessamento simétrico, ou SMP (Symmetric

Multi Processing), é uma arquitetura de multiprocessadores na qual dois ou mais

processadores idênticos são conectados a uma única memória principal. Isso permi te que qualquer processador trabalhe em qualquer tarefa, não importando onde ela

esteja localizada. Assim, é possível ficar movendo as tarefas entre processadores de

modo a tornar a carga de trabalho o mais eficiente possível. Porém, há um custo a

se pagar: como a memória é muito mais lenta que o processador, se em arquiteturas

singlecore é gasta uma grande parcela de tempo esperando pelos dados da memória, na SMP fica pior ainda, pois vários processadores podem ficar esperando por

uma mesma memória [22].

27

Uma alternativa ao SMP é a NUMA (Non-Uniform Memory Access), na

qual cada processador tem a sua própria parte de memória. Essa arquitetura permite

acessos paralelos à memória, melhorando em muito o throughput, se os dados de

um processo forem bem localizados. Por outro lado, o custo de se mover os dados

de um processador para o outro fica bem mais caro, ou seja, balancear a carga de

trabalho é bem mais custoso do ponto de vista computacional, ou seja, exige mais

recursos de processador, rede, ocupação de banda, comunicação e tempo

.

[11]

Há ainda alternativas não tão utilizadas como as acima: o Multiprocessamento Assimétrico (ASMP) designa diferentes processadores especializados para

tarefas específicas, enquanto que, no multiprocessamento com clusters de computadores, nem toda a memória está disponível para todos os

processa -

dores [22].

Como exemplo de implementação multicore podemos citar: Intel Xeon

Core Duo, Intel Xeon Quad Core, Intel Larrabee (80 cores), AMD Opteron Dual Core,

AMD Barcelona Quad Core, SUN T1 (octocore), IBM Power 6, IBM CELL (ninecore),

etc.

4 O PORQUÊ DA TRANSIÇÃO PARA O MULTICORE

Como visto anteriormente, a corrida pelo aumento de desempenho dos

processadores com o mais conveniente e fácil procedimento, que é o da elevação

do clock do processador, atingiu o seu ápice ao esbarrar no superaquecimento e na

baixa relação entre o desempenho e o consumo de energia, medido agora não em

milhões de instrução de ponto flutuante por segundo apenas, mas também dividido

pelo consumo energético em watts (GFLOP/Watt). Além do aumento do clock, a tecnologia de múltiplos processadores numa mesma placa mãe (sistemas multiprocessados – ditos MP) não era, por si só, suficiente devido a vários problemas de gerenciamento do sistema operacional e, mais especificamente, o da memória ou do ca-

28

che ou cachês associados a um ou vários dos processadores. O resultado não era

suficiente e deparava-se com a Lei de Amdahl [35] para sistemas multiprocessados,

ou seja, tudo indicava não adiantar juntar muitos processadores numa mesma placamãe devido ao custo-benefício e as dificuldades de gerenciamento acrescido do problema das aplicações não aproveitarem esta arquitetura do tipo SMP (Symmetric

Multi Processing).

O problema crucial é o do consumo energético. Como resolver ou contornar? Não foi e não é simples. Uma idéia, que foi implementada com distintas arquite turas, foi a de aumentar o número de cores ou núcleos numa mesma pastilha ou

chip. Assim, para um pequeno aumento no consumo energético poderíamos aumentar, em tese, significativamente o desempenho. A tecnologia de 90 nm dos chips assim o permitia e os primeiros, em verdade, eram como ainda muitos o são, apenas

dois cores acoplados numa mesma pastilha, isto é, praticamente se estendeu à tecnologia SMP a um único processador, por analogia, com o diferencial de ser controlado por um único sistema operacional. Outra abordagem é a de uma arquitetura

multicore, mas com um barramento interno de comunicação de alta velocidade entre

esses núcleos ou cores, ou seja, em rede.

Neste ponto, devemos frisar bem que, enquanto a GPU é uma sofisticada

evolução de um co-processador, o IBM CELL, um processador heterogêneo formado

por vários e distintos processadores em uma mesma pastilha e estes interconectados entre si através de uma rede compartilhada de alta velocidade, é uma revolucionária proposta de uma nova arquitetura de um processador nativamente paralelo e

internamente em rede. De fato, não é uma proposta, é uma realidade e o futuro pró ximo irá julgar a ousadia de seus criadores (STI)

.

[36]

Para nosso discurso inicial, acrescentarmos convenientemente alguns

gráficos e diagramas, que enriqueçam ou comprovem nossos argumentos. A transição obrigatória para o multicore está na Física. São as propriedades e leis físicas

que implicam diretamente no multicore [34].

29

Figura 1:

Evolução do processos de fabricação de processadores até 2.012.

Fonte:

Webinar da Intel, www.intel.com em 20 de março de 2007 [34].

Como podemos observar na Figura 1, os processos de fabricação de

chips estão cada vez mais provocando um adensamento de transistores numa menor área. É esperado que se atinjam processos de fabricação que possibilitem até

22 nm no ano de 2012. Atualmente são comercializados chips com tecnologia de

65nm e os de 45 nm deverão se tornar comercializáveis até 2009.

Historicamente, a análise de processadores monoprocessados revela que

enquanto o desempenho cresce linearmente, a potência necessária para operação

deste cresce exponencialmente como pode ser exemplificado com os processadores

da Intel do i486 ao Pentium(Prs) na curva normalizada ao consumo de energia do

i486 da Figura 2, demonstrando assim a insustentabilidade de se tentar aumentar o

desempenho de processadores apenas com o aumento da freqüência pois, do ponto

de vista energético, o consumo é excessivamente ineficiente e implica numa enorme

necessidade de refrigeração, o que inviabiliza soluções tecnológicas nesta direção.

30

Figura 2:

Evolução da potência consumida das CPUs x performance escalar

Fonte:

Webinar da Intel, www.intel.com em 20 de março de 2007 [34].

Como conseqüência da Lei de Moore

[anexo A]

, a quantidade de transistores

dobra a cada dezoito meses, o que adensa mais ainda o número de transistores

numa menor área do chip, enquanto a espessura do óxido também se encurta, aumentando as freqüências e reduzindo o limiar das voltagens envolvidas. Mas a espessura já atingiu as dimensões atômicas e não pode mais ser encurtada tão rapida mente. Logo, só podemos obter pequenos aumentos de freqüências com menores

reduções na voltagem, o que implica num maior consumo energético e maior dissi pação térmica como esboçado na Figura 3.

31

Figura 3:

Limitações físicas inviabilizam o aumento das freqüências

Fonte:

Webinar da Intel, www.intel.com em 20 de março de 2007 [34].

Em longo prazo, a única solução a ser considerada, sem levar em conta

novas descobertas na ciência dos materiais e na física, seria a de introduzir vários

núcleos num mesmo chip, ou seja, passar-se a fabricar e produzir processadores

com múltiplos núcleos em uma mesma pastilha, levando-se em conta a viabilidade

de fazê-lo devido ao adensamento de transistores, causado pelas novas tecnologias

de fabricação de chips, como conseqüência da Lei de Moore, contornando os problemas determinados pelas limitações da Física e, principalmente, observando que

com múltiplos núcleos num mesmo chip, podemos assim obter um melhor desempenho do processador com uma maior eficiência energética. Portanto, a tecnologia de

fabricação de processadores com muitos núcleos, dita multicore, vem obrigatoriamente, como uma forma de contornar as limitações impostas leis da Física e assim

obter um maior desempenho, com maior eficiência energética e melhor gerenciabilidade técnica, isto é, menor necessidade de refrigeração do calor gerado pela dissipação térmica do processador.

32

Figura 4:

O multicore como solução para as limitações impostas pela Física

Fonte:

Webinar da Intel, www.intel.com em 20 de março de 2007 [34].

Por exemplo: suponhamos um chip com um dado número de transistores

e a este associado uma potência unitária e um desempenho unitário. Para aumentarmos o desempenho de maneira ingênua e direta, quadruplicamos o número de

transistores num chip maior, significando apenas a duplicação do desempenho a um

custo também quadruplicado da potência consumida. Por outro lado, se formos capazes de colocar quatro pequenos núcleos com o mesmo número de transistores da

hipótese inicial, num mesmo chip poderíamos obter ao invés de um único chip com

um único núcleo, um novo chip com quatro núcleos mais eficiente em performance e

consumo energético, além de menor dissipação térmica (Figura 4).

33

Figura 5:

Consumo crescente de potência nos últimos 20 anos.

Fonte:

MIT Course 6.189 IAP, 2007 [37]

O aumento do número de transistores no chip devido à Lei de Moore e o

associado aumento da potência consumida pelo chip, medida em Watts (Figura 5),

provocaram, quase que obrigatoriamente, a marcha para o multicore, como pode ser

visto na Figura 6.

34

Figura 6:

A inexorável jornada para o multicore

Fonte:

MIT Course 6.189 IAP, 2007 [37]

Estima-se que até o ano de 2012 já se possam construir chips com processo de fabricação de 0,02 microns em pastilhas de 400 mm2 com freqüências de

clock de 13.5 GHz, conforme pode ser visto na Figura 7. Atualmente, o que está disponível no mercado são os chips com tecnologia de fabricação CMOS de 45 nm e

wafer de 300 mm2 com processadores multicore de até oito núcleos de vários fabricantes como Intel, AMD, Sun (com oito núcleos), IBM com dois núcleos para processadores Power5+ e Power6 e nove núcleos com processadores CELL. Cabe lembrar

que, na microeletrônica, um wafer é uma fina fatia de material semicondutor, assim

como o cristal de silício, na qual microcircuitos são construídos pela dopagem (por

exemplo, difusão ou implantação de íons), separação química com ácidos, e deposição de vários materiais. Wafers são importante chave para a construção de dispositivos de semicondutores, assim como circuitos integrados. Eles são feitos de tamanhos variados, de cerca de 1 polegada (25,4 mm) até 11,8 polegadas (300mm) e espessura da ordem de 0,5 mm. Geralmente, eles são provenientes do corte de uma

barra pura de um material cristalizado, usando-se para o corte uma serra de diamante ou um fio desse mesmo material, e então polidos em uma ou nas duas faces. Os

wafers fazem parte do resultado final do processo de fabricação de processadores

35

para computador: hoje em dia, aproximadamente cada wafer gera 400 microprocessadores [61].

Figura 7:

Evolução da bitola equivalente do fio em ciclos de máquina

Fonte:

MIT Course 6.189 IAP, 2007 [37]

Como uma conseqüência imediata da chegada dos processadores multicore no mercado, motivada pelas necessidades de maior desempenho a custos de

consumo e gerenciamento energéticos mais baixos e contornando problemas da Fí sica, parece inexorável a extinção dos processadores com um único núcleo, ou singlecore. Este movimento e tendência podem ser avaliados conforma apresentado na

Figura 8.

36

Figura 8:

Processador single core: em extinção

Fonte:

MIT Course 6.189 IAP, 2007 [37]

Na verdade, já podem ser vistas e comprovadas as movimentações do

mercado nesta direção desde os primeiros anos deste século, com concentrações e

forte tendência após 2004, conforme exposto na Figura 9, com destaque para MIT

Raw (2004) não comercial, o IBM CELL (2005) e o IBM Power 6 (2006) neste perío do.

37

Figura 9:

O singlecore tende a extinção. O multicore floresce.

Fonte:

MIT Course 6.189 IAP, 2007 [37]

O problema fundamental que levou à tecnologia de processadores multicore, como visto anteriormente, foi o da necessidade de se reduzir a potência consumida pelos processadores das gerações anteriores (Figura 10), cujas energias dissi padas já beiravam a temperaturas de reações nucleares e, se levadas avante, temperaturas equivalentes à da superfície solar (Figura 11), que seriam inimagináveis

ou de difícil implementação, inviabilizando novos projetos de fabricação de processadores. O multicore floresce na tentativa de contornar três barreiras intransponíveis

devido às limitações da tecnologia CMOS: a de energia, a de potência e de tamanho

de escala ou dimensões dos transistores na pastilha ou wafer definidas pela Mecânica Quântica [29].

38

Figura 10:

Problema fundamental: alta dissipação térmica

Fonte:

MIT Course 6.189 IAP, 2007 [34]

Figura 11:

Aquecimento das CPUs

Fonte:

MIT Course 6.189 IAP, 2007 [34]

A causa fundamental do problema, apresentado nas figuras 10 e 11, está

na sua natureza física, pois a potência consumida é proporcional ao quadrado da

voltagem e a freqüência de operação. Isto significa que para os processos de fabri-

39

cação de 65 nm os problemas de alimentação do processador e refrigeração seriam

intransponíveis (Figura 12).

Figura 12:

A gênesis do problema está na Física.

Fonte:

MIT Course 6.189 IAP, 2007 [34]

Re-avaliando e analisando historicamente o problema, verificamos que o

mesmo já havia ocorrido desde o instante inicial da produção do primeiro processador nos idos de 1945 até data de 1990, com a inserção do mainframe IBM ES9000

(Figura 13).

40

Figura 13:

A inviabilidade de se aumentar a freqüência indefinidamente

Fonte:

MIT Course 6.189 IAP, 2007 [34]

Naquela oportunidade, ainda foi possível uma quebra de paradigma baseada na introdução de uma nova tecnologia, findando assim a era dos processadores

com tecnologia Bipolar e surgindo uma nova era da tecnologia de processadores

CMOS. Mas, esta nova era com seu novo paradigma tecnológico resistiu uns poucos

quinze anos, até 2005, e já demonstra as suas vulnerabilidades teoricamente previstas, ou seja, necessita de ajustes tecnológicos, como indicado pela Figura 14, que é

chegado o momento. Estes ajustes tecnológicos visam equilibrar melhor o balanço

de energia, permitindo que além de aumentar ligeiramente as freqüências de cada

núcleo, pode-se fazê-lo minimizando o consumo energético do processador como

um todo, assim garantindo um melhor desempenho do mesmo. Portanto, o novo paradigma tecnológico: o de multicore com processamento paralelo heterogêneo se

vislumbra como o florescer desta novíssima era do multicore e da computação paralela heterogênea e de teraflops num desktop.

41

Figura 14:

A história se repete ou nós já vimos isto ocorrer anteriormente.

Fonte:

MIT Course 6.189 IAP, 2007 [34]

Um dos melhores exemplos desta ruptura tecnológica, que podemos exibir, é a do processador IBM CELL, com suas diminutas dimensões, alta densidade

de transistores (cerca de 241 milhões), alta freqüência de operação (3.2 GHz), heterogeneidade de processadores (1 PPE + 8 SPE) e altíssimo desempenho (240

GFLOPS teoricamente). Um novo olhar tecnológico se aproxima para iluminar nossa

visão. O CELL não pode esperar, nem nós podemos esperar o CELL (Figura 15).

42

Figura 15:

As diminutas dimensões do processador CELL

Fonte:

MIT Course 6.189 IAP, 2007 [34]

4.1

TAXONOMIA DOS MULTICORES

Os multicores podem ser divididos em três principais grupos, descritos na

seqüência:

Memória Compartilhada: Neste os processadores comparti-

lham uma única memória comum, acessível por todos os núcleos.

Rede Compartilhada: Os núcleos compartilham internamente

um barramento exclusivo para comunicação entre eles próprios.

Crippled ou Minicores: Os núcleos ou minicores são desabilita-

dos de algumas funções básicas para fins de simplificação e aproveitamento de projetos mais sofisticados em processadores mais

simples e mais baratos – um tipo de desmembramento.

Memória Compartilhada

Rede Compartilhada

Crippled ou Minicores

43

Intel Yonah, AMD Opteron

MIT Raw

Intel Tflops

IBM Power 5 & 6

IBM CELL

PicoChips

Sun Niagara T1, T2

Tabela 1 Exemplos de processadores multicore

Fonte:

MIT Course 6.189 IAP, 2007 [34]

Algumas das significativas características dos computadores listados na

Tabela 1 são detalhadas na Tabela 2, a seguir:

Processador Multicore

Características

Intel Yonah, AMD Opteron

Primeiro dualcore comercial da Intel, lançado em 2005, com 65 nm e

também com versão singlecore

IBM Power 5 & 6

Processadores dualcore IBM, sendo que o Power 6 pode atingir até

4.7 Ghz de clock, lançado em 2007 para servidores high-end

Sun Niagara T1, T2

Denominado T1 pela Sun, possui 8 cores e 32 threads, enquanto o

modelo T2 possui 8 cores e 64 threads simultâneas.

MIT Raw

Multicore experimental do MIT com 16 cores com rede interna de

alta velocidade

IBM CELL

Bastante discutido neste trabalho, 9 cores heterogêneos (1 PPE + 8

SPEs)

Intel Tflops

Nome inicial para projeto Intel do processador com 80 cores

PicoChips

Multicore heterogêneo, constituído de muitos microprocessadores

que podem ser desmembrados e agregados para constituir funções

de processamento específicas

Tabela 2 Características gerais de alguns processadores multicore

Fonte:

Sites dos fabricantes (Intel [7], IBM [8], Sun [25], MIT [14])

44

5 GPU

GPU ou unidade de processamento gráfico (Graphical Processor Unit) é

um dispositivo de renderização gráfica para PC, workstation ou console de jogos eletrônicos. As modernas GPUs são muito eficientes em manipular e exibir gráficos

computadorizados e suas estruturas internas altamente paralelas as tornam mais eficientes que as CPUs típicas e convencionais, para uma faixa de algoritmos que requisitam um intenso e massivo uso de cálculos.

Uma GPU pode alojar-se numa placa de vídeo em separado ou estar integrada na própria placa mãe. Na Figura 16, temos exemplos de GPUs.

Figura 16:

GPUs de mercado: Nvidia Quadro FX 5600 e ATI (AMD) R600

Fonte:

Sites dos fabricantes Nvidia [9] e AMD [10]

As modernas GPUs são descendentes dos chips gráficos monolíticos dos

idos anos de 80 e 90 e possuem hardwares especializados, que são capazes de efetuar a maior parte de operações gráficas 2D e operações para traçar retângulos,

triângulos, círculos e arcos. As mais recentes também já possuem suporte a 3D e tipicamente incluem funções relativas a processamento de vídeo digital.

Algumas GPUs podem fazer uso de DMAs (dispositivos de acesso direto

à memória) para reduzir os tempos de load/restore nos processadores dos hosts associados.

As GPUs surgiram da especialização de funções gráficas e ainda hoje

estão para os processadores como os co-processadores das famílias inicias de x86,

45

ditos x87. Esta analogia será crucial para entendimento das diferenças nos capítulos

seguintes.

Hoje, as GPUs paralelas avançam contra mercados específicos dominados pelas CPUs convencionais, como veremos, devido à alta especialização de suas

funções, num elevado grau de paralelismo e acentuado poder de computação aritmética.

O mercado de entretenimento formado pelos jogos eletrônicos e desenhos animados em 3D foi o grande impulsionador das GPUs e aceleradores gráfi cos, permitindo uma enorme capitalização das duas principais empresas responsáveis pelo desenvolvimento e comercialização de GPUs: Nvídea e ATI (atualmente incorporada como uma divisão pela fabricante de processadores AMD).

5.1

FUNÇÕES COMPUTACIONAIS

As GPUs mais recentes usam a maior parte de seus transistores para efetuar cálculos relativos a gráficos computacionais 3D. Elas foram inicialmente usadas

para acelerar o trabalho de mapeamento de texturas e renderização de polígonos

com uso intensivo de memória, posteriormente foram adicionadas unidades para

aceleração de cálculos geométricos tais como as transformações de vértices entre

diferentes sistemas de coordenadas. Desenvolvimentos recentes, em GPUs, incluem suporte para sombreamentos programáveis, que podem manipular vértices e

texturas com muitas das mesmas operações suportadas pelas CPUs, com técnicas

de extrapolação e interpolação para reduzir as distorções, e com alta precisão no espaço de cores. Devido a maior parte destas computações envolverem matrizes e vetores, engenheiros e cientistas demandaram maiores estudos do uso de GPUs

para cálculos não-gráficos [11].

46

5.2

GPGPU

Um novo apelo comercial com a mudança de nome de GPU para GPGPU, busca efetuar um novo enquadramento das GPUs no mercado diretamente dominado pelas CPUs, pois quando estas são comparadas com os processadores convencionais atuais são de desempenho muito superior para aplicações especializadas

de diversas ordens, como as científicas, que fazem uso intensivo de cálculos aritméticos e uma nítida paralelização muito própria e conveniente às arquiteturas das

GPUs existentes.

A General-Purpose Computing on Graphics Processing Units (GPGPU),

ou GPU de fins gerais, é uma recente tendência que força e incentiva o uso de

GPUs para efetuar computação no lugar de CPUs. A adição de estágios programáveis e precisão aritmética mais alta para pipelines de renderização permitem aos desenvolvedores de software usar as GPUs para aplicações não relacionadas a gráficos apenas. Pela exploração das arquiteturas extremamente paralelas das GPUs,

que usam a abordagem de processamento de stream (um stream é uma seqüência

da dados que podem ser números, cores, vetores RGBA, etc.), muitos problemas de

computação em tempo real podem ser acelerados consideravelmente

[12]

.

Por muitos anos as funcionalidades das GPUs foram limitadas. De fato,

por muitos anos elas foram usadas para acelerar certas partes dos pipelines gráficos. Algumas melhorias eram necessárias antes que a GPGPU se tornasse factível.

A facilidade de programação e os tipos de dados foram as principais melhorias acrescentadas as GPUs, para permitir sua melhor utilização pelos desenvolvedores de jogos para obter efeitos mais realísticos. O desenvolvedor não precisa ficar muito preocupado em portar seu programa para GPUs, pois não é uma tarefa

tão difícil quanto no caso do processador CELL, mas, com relação às estruturas de

dados, estas sim precisam ser mais bem detalhadas e compreendidas.

47

5.2.1 CONCEITOS DE PROGRAMAÇÃO EM GPGPU

As GPUs são projetadas especificamente para gráficos e assim são muito

restritas em termos de operações e programação. Por causa de sua natureza, as

GPUs não são eficientes para lidar com problemas que podem ser resolvidos usando-se processamento de stream e o hardware só pode ser usado em certas

ocasiões [11].

PROCESSAMENTO STREAM

As GPUs só podem processar vértices e fragmentos independentes, mas

podem processar muitos deles em paralelo. Portanto, é especialmente eficiente

quando o programador quer processar muitos vértices da mesma forma. Neste sentido, as GPUs são stream processadas -- os processadores que podem operar em

paralelo pela execução de um único kernel ou muitos registros num mesmo stream

de uma única vez.

Um stream é simplesmente um conjunto de registros de computação similar. Nas GPUs, vértices e fragmentos são elementos no stream e vértices e sombreadores de fragmentos são os kernels a serem executados sobre eles. Logo, as

GPUs processam elementos independentemente, se os dados são compartilhados

ou estáticos. Para cada elemento só podemos lê-lo da entrada, efetuar operações

sobre ele, e gravá-lo na saída. São permitidas múltiplas entradas e múltiplas saídas,

mas nunca um pedaço de memória que é de leitura e gravação simultaneamente.

Aritmética intensiva é definida como a operação executada por palavra de

memória transferida. É importante para aplicações GPGPU que se tenha aritmética

intensiva ou a latência de acesso à memória limitará a velocidade de computação.

48

Aplicações ideais para GPGPU possuem grandes arquivos, alto paralelismo, e mínima dependência entre os elementos de dados.

5.3

PORQUE USAR GPGPU?

As GPUs hoje são bens de consumo praticamente adquiríveis e vendáveis como commodities (produtos de prateleira) e possuem preços relativos muitos

baixos, sendo o melhor e mais poderoso hardware computacional mensurado em

GFLOPS pelo menor custo, ou seja, o melhor valor por dólar empregado. Portanto,

tem sido uma excelente opção de todos que dos seus recursos necessitam para

suas aplicações extensíveis um pouco além de suas características específicas de

processamento gráfico, com várias aplicações de fins gerais sendo portadas para as

GPUs, graças as suas novíssimas características de facilidade de programação, ou

“programabilidade” como denominaremos doravante neste trabalho, e uma enorme

largura de banda de memória. Não somente o hardware é rápido, mas também as

suas atualizações e novas tecnologias estão sendo disponibilizadas mais rapidamente que a tecnologia de seu concorrente, as CPUs, com disponibilização de device drivers (programas acionadores dos dispositivos que permitem a utilização dos

mesmos pelo sistema operacional e aplicações dos usuários) rapidamente para sistemas Linux e Windows [9].

49

Figura 17:

Acelerada evolução do poder computacional das GPUs

Fonte:

Tutorial sobre GPU de Mike Houston na SIGGRAPH 2007

[38]

As GPUs são onipresentes e economicamente menos custosas, ou seja,

estão em todos os dispositivos: placas gráficas, desktops, notebooks, PDAs, celulares, etc. Atualmente já alcançaram um bom nível de maturidade tecnológica e científica.

Na Figura 17, podemos observar que num curto espaço de tempo, de

2001 a 2007, as GPU não apenas aumentaram seu desempenho centenas de vezes

como também o fizeram com uma velocidade muito maior que as CPUs, que além

de crescer muito pouco em termos de desempenho, no mesmo período, também o

fizeram de modo muito lento relativamente as GPUs, isto no que se refere às suas

aplicações gráficas específicas, é claro.

50

5.4

TÉCNICAS GPGPU

As técnicas básicas de operação com GPUs são aplicadas em computação gráfica para renderização de figuras 2D utilizando primitivas gráficas para traçar

retângulos, triângulos, círculos, arcos, preenchendo áreas, processando vértices e

fragmentos, etc. E, também como texturização, iluminação e suavização para figuras

3D nas modernas GPUs, além de incluírem funções relacionadas a processamento

de vídeo digital.

5.4.1

CLASSIFICAÇÃO DAS OPERAÇÕES DAS GPUS

PROCESSAMENTO STREAM

As GPUs [49] podem processar vértices e fragmentos em separado mas

podem fazê-lo em muitos desses e de modo paralelo ao mesmo tempo, ou seja, o

desempenho das GPUs podem ser muito acelerado em comparação as CPUs, pois

as GPUs são processadores de streams, isto é, processadores que podem operar

em paralelo pela execução em um único kernel de muitos registros num mesmo

stream de cada vez.

51

MAPEAMENTO

A operação de mapeamento simplesmente aplica uma dada função (um

kernel) a todo o elemento no stream. Como, por exemplo, o aumento do brilho de

uma imagem com a aplicação de um fator constante a cada valor num stream. A

operação de mapeamento é de simples aplicação na GPU. O programador gera um

fragmento para cada pixel na tela e aplica o programa fragmento a cada um. O stream resultante é do mesmo tamanho do armazenado no buffer de saída.

REDUÇÃO

Algumas computações requerem o cálculo de um stream pequeno (possivelmente um stream de um elemento a partir de um stream muito maior). Esta operação é chamada de redução. Geralmente, uma redução pode ser obtida em múltiplos passos. Os resultados dos passos anteriores são usados como entradas para

os passos seguintes e o resultado final destas operações é reduzido até que se atin ja um elemento restante.

SCATTER

A operação de scatter é mais naturalmente definida sobre um processador de vértices. O processador de vértices é capaz de ajustar as posições dos vértices, o que permite ao programador controlar onde a informação será armazenada

no grid (rede de pontos que formam uma malha bidimensional retangular ou tridimensional cúbica).

52

GATHER

O processador de fragmentos é capaz de ler texturas num modo de acesso aleatório, tal que pode obter informação de qualquer célula do grid, ou múltiplas

células, se assim o desejar.

FILTROS DE STREAM

Um stream filter é essencialmente uma redução não-uniforme. A filtragem

envolve a remoção de itens do stream baseada em algum critério.

SORT

A operação sort (classificar, ordenar) transforma um conjunto desordenado de elementos em um conjunto ordenado de elementos.

SEARCH

A operação search (busca, procura) permite ao programador encontrar

um elemento particular num stream, ou possivelmente encontrar vizinhos de um elemento específico. A GPU não é usada para acelerar a busca de um elemento indivi dual, mas sim executar buscas múltiplas em paralelo.

53

5.5

ESTRUTURA DE DADOS

As estruturas de dados das GPUs são bem conhecidas e descendentes

diretas da representação de dados gráficos para texturização, renderização, buferização, etc. Permitem representar dados estruturados como vetores em uma, duas

ou três dimensões (1D, 2D ou 3D) de forma direta (1D ou 2D) e indireta (3D) mas

com limitações dependentes da memória da GPU.

5.6

APLICAÇÕES EM GPGPU

As aplicações para GPPGUs foram desenvolvidas inicialmente para as

necessidade de computação gráfica. Essencialmente: translações, rotações, texturização, rasterização, iluminação e todos os aplicativos dependentes destes procedimentos como: gráficos 2D e 3D, otimização geométrica, multiplicação matricial, processamento de sinal, etc. Posteriormente, desenvolveram-se, graças a novos algoritmos e novas potencialidades e performance das novas GPGPUs algoritmos para

sistemas de partículas, dinâmica de fluidos, processamento de vídeo, dinâmica molecular, simulação física, Ray-Tracing (traçado de raios), etc. A extensão de aplicações de computação de alto desempenho (HPC) para GPU é muito recente e possui

um amplo espectro à sua frente como, por exemplo, processamento sísmico, FFT

3D, dinâmica das nuvens, imagens médicas, etc. Novas aplicações são esperadas

mas restringe-se ao processamento de ponto fixo ou ponto-flutuante simples, ou

seja, processamento com dados numéricos do tipo inteiro ou que necessitem de baixa precisão de cálculo ou poucas casas decimais de resultados.

Aplicações em GPGPU

54

Análise de Dados

Dinâmica das Nuvens

Otimização Geométrica

Biomédica

Simulação Física

Dinâmica dos Fluídos

Multiplicação Matricial

Reconhecimento de Voz

Sistema de Partículas

Processamento de Vídeo

Simulação do Campo de Forças

FFT 3D

Dinâmica Molecular

Análise Léxica

Desenho de Grafos

Avaliação Polinomial

Processamento de Sinal

Processamento Sísmico

Gráficos

Comparação de Strings

Ray-Tracing (Traçado de Raios)

Imagens Médicas

Tabela 3 Algumas aplicações para GPGPUs

Fonte: http://www.cis.upenn.edu/~suvenkat/700/.

5.7

[39]

DIAGRAMA DE BLOCOS DA GPU

Na Figura 18, podemos verificar os detalhes arquiteturais da GPU da

Nvidia, modelo Nvidiia GeForce 8800. Existem muitos elementos na pastilha da placa gráfica ou GPU. Estes elementos, esquematicamente podem ser visualizados no

diagrama de blocos mostrado na mesma Figura 18. Os blocos verdes marcados

com “SP” e arranjados em grupos de 16 são o que a Nvidia denomina “ stream processors” (processadores de stream). A arquitetura G80 da Nvidiia, da qual faz parte

a GeForce 8800, possui oito grupos de SPs, num total de 128 processadores de

stream. Existem sombreadores de pixels e vértices mas existem processadores, de

ponto flutuante, capazes de operar sobre vértices, pixel ou outros tipos de dados. A

maior parte das GPUs operam sobre dados de pixel na forma de vetor emitindo instruções concorrentes sobre múltiplos componentes de cor de um pixel (tais como

vermelho, verde, azul ou alfa), mas os processadores stream da arquitetura G80 são

55

escalares – cada SP manipula um componente. Os SPs podem ser redirecionados

para manipular dados de vértices (ou outras coisas) dinamicamente, de acordo com

a demanda. Também, diferentemente dos processadores de gráficos tradicionais,

aqueles cujas freqüências devem estar próximas a 600 MHz ou superior, estes

possuem velocidade de clock próximas a freqüências de 1,35 GHz, dando a

GeForce 8800 um tremendo poder de processamento de ponto flutuante. A maior

parte do restante do chip trabalha a uma freqüência independente e mais convencional, da ordem de 575 MHz.

Abaixo dos oito clusters, encontra-se o chaveamento do barramento (os

pedaços com todas as linhas e setas) que conectam os clusters às seis partições

ROP. Cada partição ROP tem sua própria memória cache L2 e uma interface à memória gráfica (ou frame buffer, indicada pelo rótulo “FB”) que tem 64 bits de largura.

No total, isto fornece 384 bits de largura para a memória.

Cada conjunto de 16 SPs é formado por dois grupos de oito SPs. Cada

grupo tem seu próprio endereçamento de textura (TA) e unidades de filtragem (TF,

blocos azuis) e seu próprio pool de cache L1. Além do cache L1, existe uma conexão de barramento que leva às unidades ROP, com seus caches L2 e conexões à

memória principal.

56

Figura 18

Diagrama de blocos das unidades de processamento das GPUs

Fonte:

Course of Stanford University – CS448-07-spring [40]

5.8

PRINCIPAIS LINGUAGENS PARA USO EM GPUS

Historicamente, as principais linguagens para desenvolvimento específico

de programas para GPUs são: Brook, Cg, GLSL, HLSL, Sh

[41]

Existem muitos pacotes de desenvolvimento de software (SDK)

para programadores desenvolverem aplicações para GPUs. O principal deles, atualmente, é o CUDA (Computer Unified Development Architecture), desenvolvido pela

empresa Nvidia e, ao que tudo indica, passará a ser o padrão. Outro pacote de de -

57

senvolvimento para GPU prometido pelo fabricante AMD é o CTM (Close to The Metal) mas, ao que tudo indica, tenderá a aderência ao padrão CUDA da Nvidia por

motivos de racionalidade, evitando competições que enfraqueceriam o mercado neste nicho de mercado com área tão específica [42].

6 CELL

6.1

UMA HISTÓRIA ROMÂNTICA

O conceito de CELL foi criado pela Sony Computer Entertainment Inc., do

Japão, para Sony PlayStation 3. A gênese da idéia foi em 1999 quando o japonês

Ken Kuratagi da Sony [Kuratage], “pai do PlayStation 3”, imaginou um computador