Sistemas Digitais - 2º Exame (Época Especial) 2011/12

{11E2.doc}

1. [11E2.1] Escreva as representações binárias, decimall e hexadecimal de 65(8).

R: 65(8) = 110 101(2) = 11 0101(2) = 35(16) = 3*16+5(10) = 53(10). Confirmação:

53(10).

Confirmação 6*8+5=53

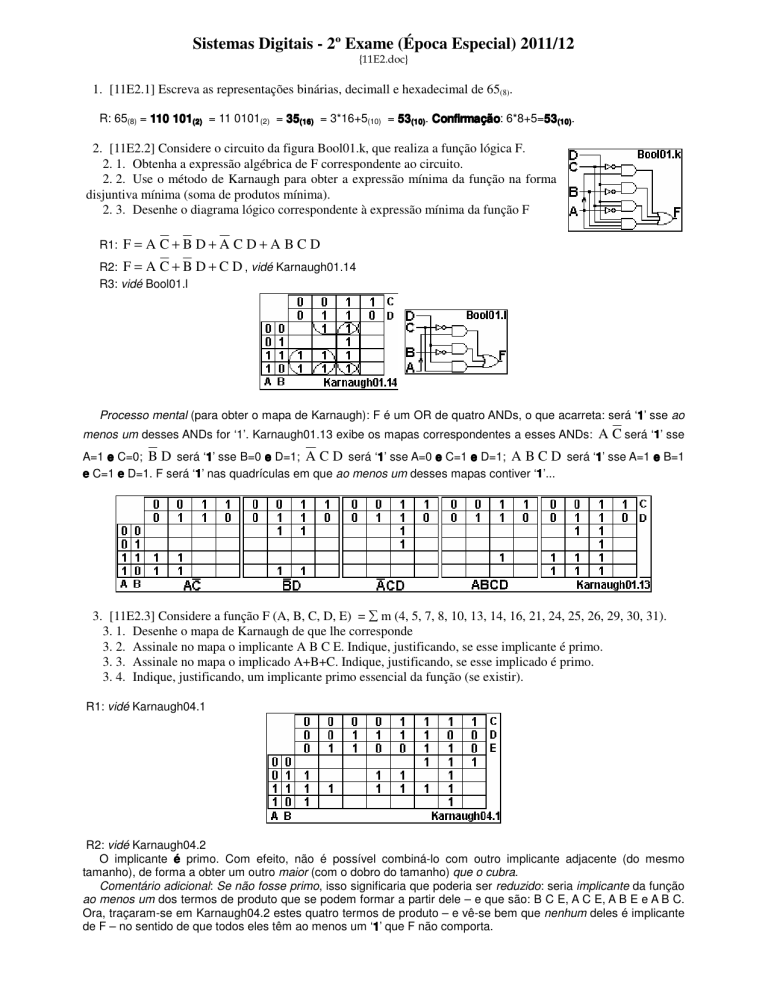

2. [11E2.2] Considere o circuito da figura Bool01.k, que realiza a função lógica F.

2. 1. Obtenha a expressão algébrica de F correspondente ao circuito.

2. 2. Use o método de Karnaugh para obter a expressão mínima da função na forma

disjuntiva mínima (soma de produtos mínima).

2. 3. Desenhe o diagrama lógico correspondente à expressão mínima da função F

R1: F = A C + B D + A C D + A B C D

R2: F = A C + B D + C D , vidé Karnaugh01.14

R3: vidé Bool01.l

Processo mental (para obter o mapa de Karnaugh): F é um OR de quatro ANDs, o que acarreta: será ‘1

1’ sse ao

menos um desses ANDs for ‘1’. Karnaugh01.13 exibe os mapas correspondentes a esses ANDs:

A C será ‘11’ sse

A=1 e C=0; B D será ‘1

1’ sse B=0 e D=1; A C D será ‘1

1’ sse A=0 e C=1 e D=1; A B C D será ‘1

1’ sse A=1 e B=1

e C=1 e D=1. F será ‘1

1’ nas quadrículas em que ao menos um desses mapas contiver ‘1

1’...

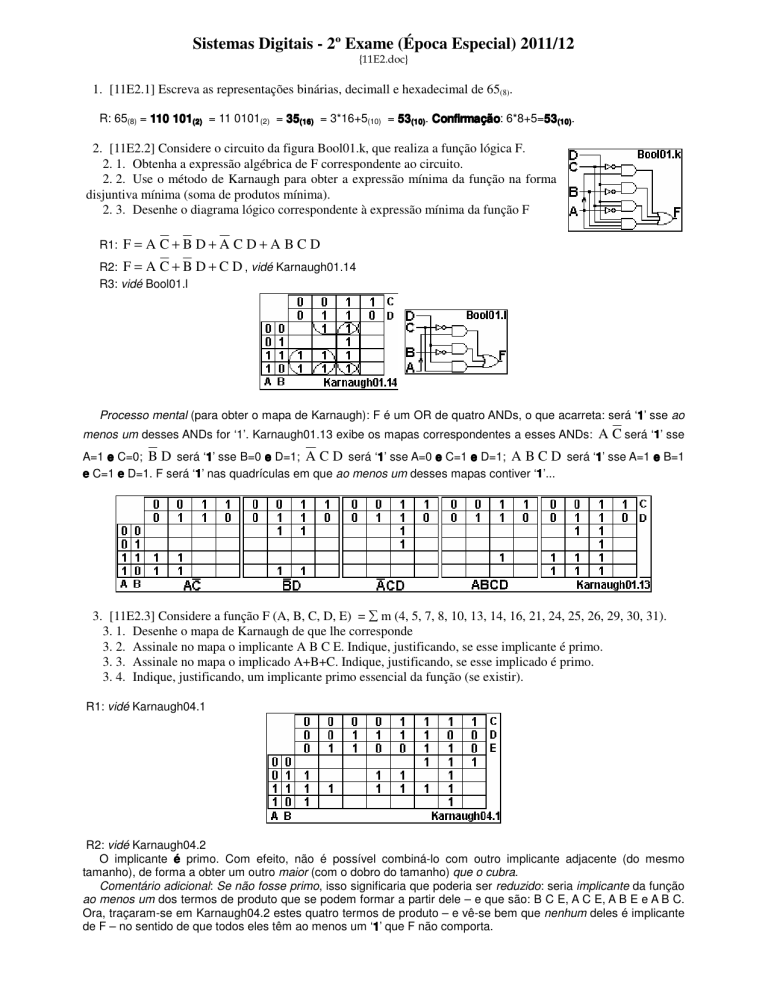

3. [11E2.3] Considere a função F (A, B, C, D, E) = ∑ m (4, 5, 7, 8, 10, 13, 14, 16, 21, 24, 25, 26, 29, 30, 31).

3. 1. Desenhe o mapa de Karnaugh de que lhe corresponde

3. 2. Assinale no mapa o implicante A B C E. Indique, justificando, se esse implicante é primo.

3. 3. Assinale no mapa o implicado A+B+C. Indique, justificando, se esse implicado é primo.

3. 4. Indique, justificando, um implicante primo essencial da função (se existir).

R1: vidé Karnaugh04.1

R2: vidé Karnaugh04.2

O implicante é primo. Com efeito, não é possível combiná-lo com outro implicante adjacente (do mesmo

tamanho), de forma a obter um outro maior (com o dobro do tamanho) que o cubra.

Comentário adicional: Se não fosse primo, isso significaria que poderia ser reduzido: seria implicante da função

ao menos um dos termos de produto que se podem formar a partir dele – e que são: B C E, A C E, A B E e A B C.

Ora, traçaram-se em Karnaugh04.2 estes quatro termos de produto – e vê-se bem que nenhum deles é implicante

de F – no sentido de que todos eles têm ao menos um ‘1

1’ que F não comporta.

R3: vidé Karnaugh04.2

O implicado é primo. Com efeito, não é possível combiná-lo com outro implicado adjacente (do mesmo

tamanho), de forma a obter um outro maior que o cubra.

Comentário adicional: Se não fosse primo, isso significaria que poderia ser reduzido: seria implicado da função

ao menos um dos termos de soma que se podem formar a partir dele – e que são: B+C, A+C e A+B. O leitor é

convidado a traçar em Karnaugh04.2 estes quatro termos – e verificar por si que nenhum deles é implicado de F –

no sentido de que todos eles têm ao menos um ‘0

0’ que F não comporta.

R4:

A B C E , é o único implicante primo que cobre a célula 7. Há outros mais.

4. [11E2.4] Um sistema de ar condicionado dum armazém, S, é controlado por sensores: H, M, P, T.

Ficam activados se e só se:

- H: a Humidade relativa for de pelo menos 60%;

- M: o peso do Material armazenado for igual ou superior a 100 toneladas;

- P: a Pressão atmosférica for igual ou superior a 760 mmHg;

- T: a Temperatura for igual ou superior a 30º.

H, T e S são activos a Low, os restantes sensores são activos a High.

O sistema deve funcionar se ocorrer uma ou mais das seguintes condições:

O peso do material for inferior a 100 t, a humidade for de ao menos 60% e a temperatura não for inferior a 30º;

O peso do material não for inferior a 100 t, a humidade for pelo menos 60% e a temperatura for inferior a 30º;

O peso do material for inferior a 100 t e a pressão atmosférica for igual ou superior a 760 mmHg.

Desenhe o esquema do circuito em lógica mista/de-polaridade.

R: vidé Polarity03.1, que pode ser simplificado, vidé Polarity03.2

5. [11E2.5] Pretende-se concretizar um circuito combinatório, que recebe na entrada um número de 2 bits e gera

um número de 4 bits correspondente ao quadrado do número de entrada. Desenhe o diagrama lógico para o

circuito pretendido. Use um único descodificador (com as dimensões mínimas necessárias) e o número

mínimo de portas lógicas elementares adicionais.

R: Adiante, apresentam-se as tabelas de verdade das saídas do circuito, {Z3,...,Z0}.

Processo mental: listaram-se, nas colunas {X1X0}, todas as combinações das variáveis; após o que se escreveu

à esquerda, em decimal entre parêntesis ‘()’, o valor {N

N} que cada uma representa (em binário); de seguida,

construiu-se a coluna {N

N2}: linha a linha, vem a ser o quadrado do correspondente valor {N

N}. Enfim, pela expansão

2

em binário de cada um desses valores {N

N }, elaboraram-se as colunas {Z3,...,Z0}.

N(10)

(0)

(1)

(2)

(3)

N(2)

0

0

1

1

X1

0

1

0

1

X0

N2(10)

(0)

(1)

(4)

(9)

N2(2)

0

0

0

1

Z3

0

0

1

0

Z2

0

0

0

0

Z1

0

1

0

1

Z0

Da tabela, deduz-se imediato o circuito pretendido, vidé Comb01.10.

Processo mental: analisando a tabela, constata-se o seguinte:

Z3 resume-se a um mintermo das variáveis {X1X0}, mais precisamente: Z3=m3;

Z2 resume-se a um outro mintermo das variáveis {X1X0}, mais precisamente: Z2=m2;

Z1 é sempre 0, ou seja, Z1=0;

Z0 é igual a X0, ou seja, Z0=X0

Para lograr os dois mintermos, m2 e m3, recorre-se a um descodificador, com duas entradas de selecção; a

elas, interligam-se as variáveis {X1X0}, ordenadas: X1, a variável de maior peso, é interligada à variável de selecção

de maior peso... Com isso, as saídas do descodificador vêm a ser todos os mintermos das variáveis {X1X0} –

ordenados de cima para baixo: {m0, m1, m2, m3} - bastando aproveitar aqueles (dois) que são de facto necessários.

6. [11E2.6] Considere o circuito Comb01.25. Qual a expressão algébrica correspondente

à função F (A,B,C)?

R: F = A ⊕ B ⊕ C .

Justificação: Com o Preâmbulo P2 em mente, será útil construir um mapa de Karnaugh

em que as variáveis de selecção do multiplexer são dispostas nas duas linhas de topo:

0

1

(0)

0

0

0

1

A F(0 ) = A

(1)

0

1

1

0

(3)

1

1

0

1

(2)

1

0

1

0

← Entrada de dados seleccionada

B ← Variável de selecção de maior peso

C ← Variável de selecção de menor peso

F(1) = A F(3) = A F( 2 ) = A

A subsequente construção da tabela de verdade de F é pacífica... Seja o caso de as variáveis {B,C} serem, por

ex., {1,0}; isso acarreta que em F irá surgir o que então estiver sendo aplicado na entrada de dados {2} – e que

vem a ser F( 2 ) = A . Ou seja: se em A estiver ‘0

0’, F ficará sendo ‘1

1’, e se em A estiver ‘1

1’, F ficará sendo ‘0

0’ – e é

isso que se inscreve na tabela de verdade. Idem para as restantes combinações de {B,C}. A etapa seguinte é

aplicar o método de Karnaugh, chegando a

F = A B C + A B C + A B C + A B C = A (B ⊕ C ) + A(B ⊕ C ) = ...

7. [11E2.7] Projecte, usando apenas o contador integrado indicado em CTR01.9, um circuito

que concretize a sequência de estados representada nas formas de onda em CTR01.10

R: vidé CTR01.11.

Justificação: convém, antes de mais, entender o ciclo em CTR01.10, e que vem a ser:

S0

S1

S2

S3

0

1

1

0

6 →

1

1

1

0

7 →

0

0

0

1

8 →

1

1

0

0

3 →

0

1

0

0

2 →

1

0

0

0

1 →

0

1

1

0

6

← No estado ‘8’, E0 deve ser ‘1’ (e ‘0’ no estado ‘1’

← Nos estados ‘8’ e ‘1’, E1 deve ser ‘1’

← No estado ‘8’, E2 deve ser ‘0’ (e ‘1’ no estado ‘1’

← Nos estados ‘8’ e ‘1’, E3 deve ser ‘0’

→...

Da análise do ciclo sobressaem três tipos de comportamento:

- há casos {6→7 e 7→8} em que o contador incrementa ‘1’ – e isso logra-se nos modos M2, M3, vidé 2,3,+

- há casos {3→2 e 2→1} em que o contador decrementa ‘1’ – e isso logra-se nos modos M2,M4, vidé 2,4,- nos restantes casos {8→3 e 1→6}: advém um valor não-adjacente – e isso logra-se no modo M1, vidé 1,6D

Convém traduzir estas conclusões em mapas de Karnaugh (de M2 e M3), vidé adiante

- nas células 6 e 7, M2= M3=1

- nas células 3 e 2, M2=1, M3=0

- nas células 8 e 1, M2=0, M3 qualquer – pressupondo respectivamente {0011

0011}

0110}

0011 e {0110

0110 em {E3,...,E0};

- em todas as outras células, M2 e M3 são irrelevantes...

0 0

0 1

1 1

1 0

S3 S2

0

0

0

4

12

8

0

1

1

5

13

9

1

1

3

7

15

11

1

0

2

6

14

10

0

0

X

X

X

0

0 1 1

1 1 0

0 1 1

X 1 1

X X X

X X X

M2

0

0

X

X

X

X

0 1 1 S1

1 1 0 S0

X 0 0

X 1 1

X X X

X X X

M3

A subsequente aplicação do método de Karnaugh conduz a: M2=S1 e M3=S2.

Falta determinar a que ligar {E3,...,E0}, para lograr as transições {8→3

3 e 1→6

6}. É

possível, é claro, proceder como se fez para M2 e M3, a saber: preencher os mapas de

Karnaugh de {E3,...,E0} e deduzir as respectivas expressões algébricas... Mas um olhar

cuidado permitirá deduzi-las, sem tanto esforço...

Em poucas palavras, trata-se de, quando M2=0, produzir 0011 ou 0110.

0110 Um relance

conclui que há neles algo comum, a saber: o primeiro bit à-esquerda é ‘0

0’, e o terceiro bit é

‘1

1’, ou seja: basta impor E3=0 e E1=1...

=1

Quanto ao segundo bit, ele deve volver-se ‘0

0’ no estado ‘8’, e ‘1

1’ no estado ‘1’ - a questão

que então se põe vindo a ser esta: a que ligar E2, de forma que ele se comporte assim?

Olhando para a codificação de ambos os estados, 1000 e 0001,

0001 é pacífica a conclusão:

bastará fazer E2=S0. O raciocínio é análogo para o quarto bit: a que ligar E0, de forma que

ele advenha ‘1

1’ no estado ‘8’, e ‘0

0’ no estado ‘1’? Olhando para a codificação de ambos os

estados, 1000 e 0001,

0001 deverá ser pacífica ao leitor a conclusão: bastará fazer E0=S3.

CTR01.11 reúne as conclusões feitas; ademais, fixa os pertinentes valores nas entradas CT e G5...

8. [11E2.8] Considere o circuito da figura ShiftReg01.9. Indique a sequência de estados, começando no estado 0

e até voltar ao estado 0.

R: A sequência de estados encontra-se na tabela adiante.

Processo mental: As entradas de selecção do modo estão fixas em ‘H

H’; portanto, o

registo está permanentemente no modo M3: deslocamento à esquerda (vidé ‘3←’). Ou

seja: por cada clock, Q2 recebe o valor de Q1, Q1 recebe o valor de Q0 e Q0 recebe o

que se encontrar na entrada 3,4D – e que vem a ser

Q1 ⊕ Q 2

Isso habilita a traçar a seguinte evolução:

Q2 Q1 Q0 Entrada externa à direita:

0 0 0

1

0 0 1

1

0 1 1

0

1 1 0

1

1 0 1

0

0 1 0

0

1 0 0

0

0 0 0 ←voltou ao início

Q1 ⊕ Q 2

Em decimal, a sequência de estados vem então a ser a seguinte: 0 → 1 → 3 → 6 → 5 → 2 → 4 → 0 ...

9. [11E2.9] Um circuito sequencial tem uma entrada X e duas saídas {Z1Z0}, e o

diagrama de estados SeqSynth03.13. Projecte o circuito recorrendo ao menor

número possível de flip-flops do tipo D. Para produzir a saída e excitar as

entradas dos flip-flops, use uma ROM. Indique o conteúdo da tabela da

ROM.

R: O circuito, e tabela da ROM, encontram-se adiante (vidé SeqSynth04.8).

Justificação: a tabela de estados/saídas é a seguinte:

0

0

1

1

Q1

0

1

0

1

Q0

1

0

1

0

1

0

0

0

1

1

Z1

1

0

1

0

1

0

1

1

0

0

Z0

0

0

1

1 X

0

1

1

1

1

1

1

0

0

0

0

1

1

0

0

0

D1=Q1(t+1) D0=Q0(t+1)

Processo mental: repare-se, por ex., na seta etiquetada ‘1

1/1

11’ que se dirige do círculo ’0

01’ para o círculo ‘10

10’...

10

Ela indica que, encontrando-se o circuito no estado ‘Q1=0

0,Q0=1

1’, e se a entrada for X=1

1, ele irá produzir as saídas

Z1=1

1,Z0=1

1, e – no próximo clock - deverá transitar para o estado Q1=1

1,Q0=0

0. Essa informação é inscrita na tabela

da seguinte maneira: na linha ‘0

01’, e nas colunas X=1

1 dos mapas de Z1, Z0, Q1(t+1) e Q0(t+1), inscreve-se 1,1,1,0.

Para as demais quadrículas, o raciocínio é similar.

Repare-se que as variáveis {Q1,Q0} das tabelas não se encontram no código binário reflectido – pela simples

razão de que se vai usar uma ROM: não há lugar à simplificação pelo método de Karnaugh... Isso habilita a

construir de imediato a tabela da ROM.

(0)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

0

1

1

1

0

0

1

0

1

1

1

0

0

1

0

0

0

0

0

1

1

0

1

1

1

0

1

1

0

0

0

1

(address) D1 D0 Z1 Z0

A tabela da ROM deverá conter 4 tabelas de verdade: as das (duas) saídas, {Z1, Z0}, e as de excitação dos

(dois) flip-flops, {D1, D0}. Essas tabelas comportam três variáveis, a saber: {Q1,Q0,X} – o que se volve em 8

combinações distintas, o mesmo é dizer: a ROM deverá ter as dimensões 8x4

8x4.

Regressando ao exemplo acima: à seta etiquetada ‘1

1’ saindo do círculo ’01

01’

01 estão associadas 4 informações: as

saídas {Z1=1

1,Z0=1

1} e os estados seguintes Q1=1

1,Q0=0

0 – o mesmo é dizer, e porquanto se usam flip-flops ‘D’: os

valores, {D1=1

1,D0=0

0}, a aplicar às entradas dos flip-flops, para que eles tenham o comportamento requerido no

diagrama de estados. O que a ROM “faz” é armazenar esses 4 valores, ou seja: na posição de memória

endereçada pela combinação ‘011’ (Estado=01,Entrada=1), inscreve-se 1011

1011.

11 Para as demais posições de

memória, o raciocínio é similar.

Note-se que, no endereço, as variáveis de estado {Q1,Q0} ocupam as posições de maior peso; isso facilitou a

transposição dos mapas para a tabela da ROM: para preencher a coluna D1 da ROM, bastou copiar do mapa de

D1, lendo da esquerda para a direita e de cima para baixo... E as posições de memória de maior peso também

acabaram por ser ocupadas pelas entradas dos flip-flops – conquanto agora por razões de grafismo...