Faculdade de Engenharia da Universidade do Porto

Redução da potência de uma interface de alta

velocidade em tecnologia CMOS através de

“power gating”

Luís Miguel Granja Gomes

VERSÃO FINAL

Relatório final da UC Preparação para a Dissertação realizado no âmbito do

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Major Telecomunicações

Orientador na FEUP: Prof. Dr. João Canas Ferreira

Orientador na Synopsys: Eng.º Hélder Araújo

13 de Fevereiro de 2013

© Luís Miguel Granja Gomes, 2013

ii

Índice

Índice............................................................................................... iii

Lista de figuras ................................................................................... iv

Lista de tabelas ................................................................................... v

Abreviaturas e Símbolos ........................................................................ vi

Capítulo 1 .......................................................................................... 1

Introdução ......................................................................................................... 1

1.1 - Enquadramento ........................................................................................ 1

1.2 - Motivação ............................................................................................... 2

1.3 - Objetivos ................................................................................................ 3

1.4 - Estrutura do documento .............................................................................. 3

Capítulo 2 .......................................................................................... 4

Estado da Arte .................................................................................................... 4

2.1 - Energia e Potência ..................................................................................... 4

2.2 - Potência Dinâmica vs Potência Estática ........................................................... 5

2.3 - Power Gating - Conceito .............................................................................. 6

2.4 - Principais Desafios do Power Gating ............................................................... 9

2.5 - Metodologia para implementação de Power Gating com suporte de ferramentas

Synopsys ............................................................................................... 18

Capítulo 3 .........................................................................................20

Proposta de Trabalho ......................................................................................... 20

3.1 - Metodologia ........................................................................................... 20

3.2 - Ferramentas de trabalho ........................................................................... 21

3.3 - Plano de trabalho .................................................................................... 22

3.4 - Resultados Esperados ............................................................................... 25

Referências .......................................................................................26

iii

Lista de figuras

Figura 2.1- Perfil de um bloco alvo de Power Gating. Fonte: [1] ..................................... 7

Figura 2.2- Utilização de Sleep Transistors. Fonte: [3] ................................................. 7

Figura 2.3 - Diagrama de blocos de um sistema com Power Gating. Fonte: [1] .................... 8

Figura 2.4 - Implentação de Fine Grain numa porta AND. Fonte: [1] .............................. 11

Figura 2.5 - Implementação Coarse Grain. Fonte: [2] ................................................ 12

Figura 2.6 - Header Switch(esquerda) e Footer Switch(direita). Fonte: [1] ...................... 12

Figura 2.7 - Implementação em Anel. Fonte: [1] ...................................................... 13

Figura 2.8 - Implementação em rede. Fonte: [1] ...................................................... 14

Figura 2.9 - Registo de retenção. Fonte: [1]............................................................ 16

Figura 2.10 - Célula de isolamento que fixa a saída em "0". Fonte [1] ............................. 18

Figura 2.11- Metodologia de implementação utilizando ferramentas Synopsys. Fonte: [2] .... 19

Figura 3.1 - Planemanento: Diagrama de Gantt ........................................................ 24

iv

Lista de tabelas

Tabela 1.1 - Técnicas Low Power ...........................................................................2

v

Abreviaturas e Símbolos

Lista de abreviaturas

CAD

Computer Aided Design

CMOS

Complementary metal–oxide–semiconductor

GDSII

Graphic Database System II

HDL

Hardware Description Languages

HDMI

High-Definition Multimedia Interface

IP

Intellectual Property

LVA

Linha Virtual de Alimentação

RTL

Register Transfer Level

SBPF

Synopsys Binary Parasitic Format

SoC

System-On-A-Chip

SPEF

Standard Parasitic Exchange Format

ST

Sleep Transistor

ITRS

INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

VLSI

Very Large Scale Integration

vi

Capítulo 1

Introdução

Esta dissertação foi proposta pela Synopsys Portugal e é realizada no âmbito do Mestrado

Integrado em Engenharia Eletrotécnica e de Computadores da Faculdade de Engenharia da

Universidade do Porto.

O presente capítulo introduz o tema da dissertação e os motivos pelos quais a sua

realização é pertinente. São listados os principais objetivos a alcançar e apresentada a

estrutura do documento.

1.1 - Enquadramento

O tempo dedicado à utilização de dispositivos eletrónicos ocupa uma grande percentagem

da vida quotidiana. Estes dispositivos sofreram uma notável expansão e desenvolvimento nas

últimas décadas. É possível, por exemplo, ler um livro num dispositivo de dimensões mínimas,

cuja autonomia atinge várias horas. É ainda inegável, a dependência que apresentamos em

relação à utilização de muitos equipamentos em áreas tão distintas como a medicina ou o

entretenimento.

A expansão verificada é possível devido à revolução e aos avanços no desenvolvimento de

circuitos VLSI (Very Large Scale Integration) em tecnologia CMOS. A utilização de Linguagens

de Descrição de Hardware (HDL), a reutilização de modelos (IP cores) e a utilização de

ferramentas CAD permitiu que os circuitos aumentassem a sua frequência de funcionamento e

reduzissem o tamanho [1].

À medida que a tecnologia encolhe e aumenta a sua performance, surgem problemas

associados ao consumo de energia. Maiores frequências refletem-se num maior consumo de

energia dinâmica. Por sua vez, menores dimensões refletem-se num aumento do consumo

estático. Este problema levou os projetistas a desenvolverem técnicas para diminuir o

consumo de energia dos circuitos VLSI, em ambas as componentes dinâmica e estática. Entre

estas técnicas, as mais utilizadas estão resumidas na Tabela 1.

Esta dissertação é realizada em conjunto com a Synopsys Portugal e tem como objetivo a

redução da potência de uma das suas interfaces de alta velocidade através da implementação

de Power Gating, atuando ao nível do consumo estático.

2 Introdução

Técnica

Princípio de funcionamento

Objetivo

Clock Gating

Desligar o sinal de relógio

Diminuir potência

dinâmica

Otimização

nível

das

ao

portas

Reordenar portas lógicas e operandos para

Diminuir potência

diminuir atividade de comutação

dinâmica

Utilizar transístores com Vt baixo, apenas

Reduzir fugas

lógicas

Multi-threshold

em caminhos críticos

Power Gating

Utilização

de

células

especiais

para

Reduzir fugas

desligar certos blocos quando estes não

estão em funcionamento.

Multi VDD

Utilizar

tensões

de

alimentação

mais

baixas em blocos que possam funcionar a

Reduzir quadraticamente

a potência dinâmica.

frequências mais baixas

Tabela 1.1 - Técnicas Low Power

1.2 - Motivação

Até aos anos 90, a expansão da tecnologia media-se pelo número de transístores por chip

e pela sua frequência de funcionamento. De acordo com a lei de Moore, assistiu-se a um

grande crescimento na integração de cada vez mais transístores, potenciado pela redução do

seu tamanho. Este fenómeno é denominado de scaling.

O scalling permitiu que os circuitos se tornassem cada vez mais pequenos e mais rápidos.

No entanto a maior densidade de transístores, conduziu a um aumento da densidade de

potência e, consequentemente, da temperatura.

A partir desse ponto, começou-se a dar importância ao consumo de potência devido a

diversos fatores. Aparelhos portáteis são alimentados a baterias, o que torna importante

qualquer redução do consumo energético. Por outro lado a imunidade ao ruido diminuí e os

custos dos sistemas de refrigeração e de packaging aumentam significativamente. Como

exemplo, em 2006 os centros de servidores dos EUA consumiam, cerca de 61 TWh, o que

corresponde a um custo de 4.5 mil milhões de dólares em sistemas de refrigeração [4]. A

INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS (ITRS) afirma que, neste

momento a potência tornou-se o principal fator limitante, em detrimento da velocidade.

Inicialmente, a potência dinâmica dominava as preocupações dos projetistas e ia sendo

combatida com a diminuição da tensão de alimentação. Para manter o aumento de

performance, transístores com tensões de threshold mais baixas começaram a ser utilizados,

o que potenciou um aumento das correntes de fuga. Sendo assim, para tecnologias

avançadas, a partir dos 90nm, a potência estática (conhecida como leakage) começa a

sobrepor-se à potência dinâmica [1].

É neste aspeto que esta dissertação pretende atuar, ao implementar Power Gating, como

uma das técnicas mais eficazes de redução da potência estática. Estudos afirmam que é

Introdução 3

possível reduzir o consumo de potência cerca de 1000x [3]. A justificação é simples: quanto

menos tempo o circuito estiver ligado, menos potência dissipará.

Como já referido na secção anterior, o método Power Gating será implementado numa

interface de alta velocidade. Este tipo de interfaces tem estado cada vez mais em foco no

desenvolvimento de sistemas. Muitos dos dispositivos que utilizamos no dia-a-dia, como

televisores ou dispositivos de armazenamento, utilizam cada vez maiores taxas de

transferências de dados, chegando aos Gbps, quando há alguns anos apenas atingiam taxas na

ordem dos Mbps. Por exemplo, a versão 1.4 do HDMI, atinge 3.4Gbps por canal, esperando-se

que atinga os 6Gbps na verão 2.0 (lançamento programado para o primeiro semestre de 2013)

[5]. Considerando, a crescente taxa de utilização de interfaces deste tipo, e o aumento das

suas taxas de transmissão, torna-se importante atuar no controlo do consumo de energia.

1.3 - Objetivos

Recorrendo à ajuda de ferramentas CAD, como fermentas de síntese lógica, síntese física

e de simulação e análise, esta dissertação tem como objetivos:

1. Reduzir a potência de uma interface de alta velocidade em tecnologia CMOS, através

da implementação de Power Gating;

2. Não prejudicar o desempenho da interface em questão;

3. Não alterar a funcionalidade da interface em questão.

Com o evoluir dos trabalhos, é natural que mais objetivos específicos sejam introduzidos.

1.4 - Estrutura do documento

No segundo capítulo é levantado o estado da arte no que diz respeito à aplicação de

Power Gating.

Finalmente o terceiro capítulo descreve a metodologia a seguir e apresenta o plano de

trabalhos proposto.

Capítulo 2

Estado da Arte

Este capítulo apresenta conceitos associados ao projeto de circuitos de baixa potência,

relevantes para a compreensão do problema. É ainda explicado o conceito que suporta a

metodologia Power Gating bem como os componentes e desafios críticos para uma correta

implementação da mesma.

2.1 - Energia e Potência

Potência e energia são dois conceitos muitas vezes confundidos. Quando nos referimos a

potência, consideramos a potência instantânea presente no circuito ou num elemento do

circuito. É definida como o produto da corrente que o atravessa pela tensão aos seus

terminais, e é expressa em Watts (W):

( )

( )

( )

(2.1)

A energia consumida ( ) pelo circuito durante um intervalo de tempo é o integral da

potência instantânea, ou seja a área delimitada pela curva da potência. A sua unidade SI é o

Joule (J), mas no contexto das baterias é normalmente utilizada a unidade Watt-hora (W-hr)

= 3600J.

(2.2)

Estado da Arte 5

O estado de funcionamento de um dispositivo eletrónico influencia a potência instantânea. Se

considerarmos um aparelho de comunicação móvel, uma chamada ativa implica, certamente,

mais potência que o modo standby. Desta forma, quanto maior a potência instantânea no

dispositivo mais energia será consumida e, consequentemente, o tempo de vida da bateria

decresce.

2.2 - Potência Dinâmica vs Potência Estática

No contexto de aplicação de Power Gating, é a potência estática que merece maior

atenção pois é ela que será maioritariamente afetada. No entanto é interessante perceber de

onde vem o conjunto da potência num circuito CMOS.

A potência total consumida por um circuito CMOS é igual à soma da potência dinâmica e

da potência estática:

(2.3)

Potência dinâmica

A Potência Dinâmica (

) é resultado da carga e descarga de capacidades, resultante da

atividade de comutação dos transístores (

), e da corrente de curto-circuito quando

ambas as redes PMOS e NMOS estão ativas (

).

(2.4)

é função da tensão de alimentação (

frequência de relógio (

), da capacidade de carga (

), da

) e da probabilidade dos sinais transitarem entre 0 e 1( ).

(2.5)

A outra componente de potência dinâmica,

(

), da corrente de curto-circuito (

é função da tensão de alimentação

, muitas vezes chamada crowbar current) e do

intervalo de tempo em que ambas as redes PMOS e NMOS estão a conduzir ( ).

(2.6)

Neste contexto, desde que o tempo de subida do sinal de entrada não seja muito longo,

é negligenciável em relação a

.

Potência estática

Por seu lado,

está presente mesmo quando os transístores não estão a comutar. Este

tipo de potência está associado a correntes de fuga que estão sempre presentes, desde que o

circuito se encontre ligado. Por este motivo é muitas vezes referida como leakage. É o

conjunto de 3 tipos de correntes de fuga:

6 Estado da Arte

Sub-threshold Leakage (

) - É a corrente que flui do dreno para a fonte do

transístor quando este se encontra na região de inversão fraca, ou seja,

quando

. Ou, por outras palavras, é a corrente que atravessa o canal

do transístor quando este era suposto não estar a conduzir.

Gate Leakage (

) – A corrente da porta de um transístor MOS é

idealmente zero, uma vez que esta é isolada por um material dielétrico. No

entanto, existe uma corrente que flui diretamente da gate para o substrato,

através desse material isolador.

Reverse-bias P-N Junction Leakage (

) – Corrente que flui da fonte ou do

dreno para o substrato através dos díodos inversamente polarizados,

presentes nas junções P-N dos transístores.

A corrente de sub-thershold é fortemente dependente de

. Uma diminuição de

,

implica um aumento exponencial da corrente de sub-threshold, como já referido

anteriormente.

dominava a potência estática de um circuito. No entanto, com a

constante redução da espessura do material dielétrico da porta dos transístores,

tem tomado proporções significativas, atingindo 1/3 de

para 90 nm, e

igualando ou ultrapassando Isub, para tecnologias mais avançadas [1].

2.3 - Power Gating - Conceito

Um SoC (system-on-a-chip) é constituído por vários blocos com funcionalidades

diferentes. Cada um desses blocos pode operar num dos seguintes modos:

Modo ativo – Quando executa a sua função e, por isso, as portas lógicas constituintes

estão a comutar.

Modo Standby – Quando o funcionamento do bloco não é necessário, ou seja, os sinais

associados mantêm o seu estado.

No Modo Standby, a potência dinâmica é eliminada, uma vez que não existe atividade de

comutação. No entanto, a potência estática mantém-se uma vez que o bloco continua

alimentado.

Estado da Arte 7

Power Gating consiste em desligar os blocos que não estão em funcionamento, diminuindo

assim as correntes de fuga, e voltar a ligá-los quando o seu funcionamento for novamente

necessário. Deste modo um bloco pode funcionar em dois modos distintos: Active Mode e

Sleep Mode. O perfil de funcionamento de um bloco em que foi aplicado Power Gating está

representado na figura 2.1.

Figura 2.1- Perfil de um bloco alvo de Power Gating. Fonte: [1]

Para desligar um bloco, transístores MOS com

elevado (adiante designados por ST-sleep

transistor) são utilizados como interruptores e posicionados entre o bloco e as linhas de

alimentação:

PMOS, colocado entre VDD e o bloco, e por isso designado Header Switch;

NMOS, colocado entre GND e o bloco, e por isso designado Footer Switch.

Figura 2.2- Utilização de Sleep Transistors. Fonte: [3]

Os blocos do circuito deixam, então, de ser alimentados diretamente pelas linhas de

alimentação, para serem alimentados através dos ST. É legítimo considerar que estamos

perante uma nova linha de alimentação à qual poderemos chamar Linha Virtual de

Alimentação (LVA) (VDD ou GDN).

8 Estado da Arte

Os ST são controlados por um sinal, o qual pode, convenientemente, ser chamado Sleep

Signal e que é gerado por um bloco denominado Controlador de Power Gating.

No caso dos Header Switches, para desligar o bloco, Sleep Signal toma o valor lógico 1, de

forma a colocar o transístor no corte. Caso se trate de um Footer Switch, acontece

precisamente o contrário, ou seja, Sleep Signal toma o valor lógico 0.

Além do controlo do Sleep Signal é necessário garantir, que quando a alimentação de um

bloco é restaurada, este inicie no mesmo estado em que estava aquando a interrupção do seu

funcionamento. Para isso, são utilizados registos que guardam o estado dos blocos. Estes

registos são denominados Registos de Retenção.

Outro aspeto a ter em conta é o fato de as saídas do bloco que sofre Power Gating serem, ao

mesmo tempo, entradas de blocos que estão sempre ligados. Estas saídas podem comutar

muito lentamente e permanecer muito tempo num valor indefinido, o que proporciona o

aumento da já falada corrente de curto-circuito ou crowbar current (

) do bloco que se

encontra sempre ligado. Este problema pode ser atacado recorrendo a células especiais que,

quando necessário, isolam o sinal de saída e previnem a corrente de curto-circuito.

Assim sendo, e de acordo com [1] os elementos fundamentais para a implementação de

power gatins são:

Rede de Sleep Transistors (Power Switching Fabric)

Controlador de Power Gating; (Power Gating Controller)

Mecanismo de retenção de estado;

Células de isolamento (Isol)

Figura 2.3 - Diagrama de blocos de um sistema com Power Gating. Fonte: [1]

Estado da Arte 9

2.4 - Principais Desafios do Power Gating

A projeção destes elementos é a espinha dorsal da implementação de Power Gating. Contudo,

enquanto o projeto é desenvolvido há certos aspetos que devem ser tidos em conta:

Identificação de Power Islands;

O impacto na performance;

O impacto na área;

A queda de tensão imposta pelos Sleep Transistors;

A energia necessária para entrar e sair do Sleep Mode;

O tempo necessário para voltar a alimentar o bloco (Wake-up time);

A corrente que se gera, e consequente energia, durante o tempo em que alimentação

do bloco é reposta (In-Rush Current);

A flutuação gerada nas linhas de alimentação até a alimentação ser reposta

(Power/Ground Bounce), originada pela In-Rush-Current.

2.4.1 Identificação de Power Islands

O conceito de Power Islands é introduzido por [6]. Os autores apresentam uma metodologia

de alto nível em que partes do sistema com características de funcionamento semelhantes

são agregadas e posicionadas numa região que é controlada independentemente. Cada uma

destas regiões é uma Power Island e pode ser individualmente alvo de Power Gating. O

truque é analisar o sistema ao nível RTL e identificar blocos com maior sobreposição do

tempo de funcionamento e criar Power Islands que possam ser desligadas o maior número de

ciclos possíveis. Com esta metodologia ou autores afirmam que atingem poupanças no

consumo de potência entre 5% a 20% com tecnologia de 65nm.

2.4.2 Wake Up Time, In Rush Current e Power/Ground Bounce

Uma característica fulcral de qualquer implementação de Power Gating é o tempo que

decorre desde o fim do Sleep Mode e o início do Active Mode, ou seja, o tempo necessário

para repor a alimentação na LAV (conhecido como Wake-Up Time). É do interesse do

projetista diminuir este tempo, uma vez que, quanto mais rápido a alimentação for reposta,

mais tempo o circuito pode permanecer desligado, poupando mais energia.

No entanto, manter este tempo reduzido, implica uma variação abruta de corrente

instantânea (

) que surge da linha de alimentação e que é necessária para carregar a LVA.

Esta variação abrupta de corrente, além de implicar um aumento de potência, cria flutuações

na linha de alimentação. Ora, em circuitos low power, em que a tensão de alimentação é

10 Estado da Arte

mantida baixa, qualquer variação da mesma pode provocar perturbações na operação de

todos os blocos adjacentes.

Sendo assim, existe um compromisso entre o quão rápido é possível reativar um bolco e a

flutuação da linha de alimentação.

Surge daqui, que é importante desenvolver técnicas que limitem

, de forma a

diminuir as flutuações da linha de alimentação e a manter o tempo de reativação o mais

reduzido possível.

Com este objetivo foram desenvolvidos alguns métodos que estão documentados em

vários artigos. De salientar [7] que, com uma tecnologia de 180nm atingiu uma redução de

10.23% no Wake-Up Time, mantendo a mesma flutuação das linhas de alimentação

experienciada pelo Power Gating tradicional (+-0.083V). Estes resultados resultam da

ativação do circuito por fases, balanceado a variação da corrente, de forma a diminuir o

efeito na flutuação da alimentação. São gerados dois sinais de controlo para dois ST. Um dos

sinais comporta-se da mesma forma que o sinal convencional, enquanto que o outro, aplicado

a um ST mais pequeno, efetua a transição 1->0, em dois degraus, dividindo o período de

ativação em quatro fases. Desta forma, a corrente induzida varia menos, permitindo diminuir

o tempo de ativação, mantendo a mesma característica de flutuação.

Uma solução parecida com a anterior é descrita em [8], no entanto apresenta resultados

mais satisfatórios. O princípio de funcionamento é o mesmo, sendo a ativação executada em

duas fases. A primeira inicia o restabelecimento de energia, limitando a corrente instantânea

gerada. A segunda fase completa a ativação e ativa o bloco. Ao contrário do exemplo

anterior, não são utilizados dois ST. É utilizado apenas um, mas que tem a particularidade de

funcionar como um díodo, bastando para isso introduzir um pequeno transístor de controlo

entre o seu dreno e porta. Na primeira fase, o ST comporta-se como um díodo, reduzindo a

corrente instantânea na linha de alimentação e, na segunda fase, comporta-se como um

transístor normal, restabelecendo energia ao circuito. Esta abordagem, para os mesmos

180nm, permite reduzir o tempo de ativação em 62.3%, ao mesmo tempo que limita a

flutuação da alimentação em 67%.

Outra abordagem é sugerida em [9]. Neste caso é usada uma linha de alimentação auxiliar

que é ligada a cada bloco do sistema através de transístores bypass. Desta forma, apenas o

transístor bypass do bloco que está a ser reativado está ativo, ficando os restantes blocos

ligados apenas à linha principal de alimentação. Assim sendo, a flutuação provocada na linha

auxiliar de alimentação não influencia a operação dos blocos adjacentes. Com este método,

os autores afirmam que, para um processador dual-core fabricado com uma tecnologia de

90nm e para tempos de reativação superiores a 150ns, conseguem diminuir a flutuação de

30mV para 5mV. Para tempos de ativação mais pequenos os resultados mostram que os

ganhos são ainda maiores.

Estado da Arte 11

2.4.3 Projeto da Rede de Sleep Transistors

No que diz respeito ao projeto da rede de interruptores, além dos desafios descritos na

secção anterior, existem várias escolhas a ser feitas.

Fine Grain vs Coarse Grain

Para a implementação dos Sleep Transistors, existem duas alternativas distintas: Fine Grain e

Coarse Grain.

Em Fine Grain os ST encontram-se no interior de cada Standard Cell que constitui o bloco.

Uma vez que que têm que fornecer a corrente necessária para a célula funcionar, têm que

ser relativamente grandes, podendo aumentar a área da célula em 2 a 4 vezes [1]. A grande

vantagem é que é possível seguir o fluxo normal de projeto, uma vez que todas as

características impostas pelo ST já estão devidamente caracterizadas e camufladas.

Figura 2.4 - Implentação de Fine Grain numa porta AND. Fonte: [1]

No caso de Coarse Grain, os blocos recebem a energia através de um conjunto de células

específicas para Power Gating, que têm que constar na biblioteca de células utilizada. Este

método torna o projeto mais complicado, uma vez que as características de funcionamento

não são conhecidas.

12 Estado da Arte

Figura 2.5 - Implementação Coarse Grain. Fonte: [2]

O impacto na área do método Fine Grain faz com que, na maior parte dos casos, não se

justifique a maior facilidade de projeto. Por este motivo Coarse Grain é o método mais

utilizado.

Header vs Footer

Uma outra escolha prende-se com a utilização de Header Switches ou Footer Switches, ou

seja, comutar VDD ou comutar GND.

Figura 2.6 - Header Switch(esquerda) e Footer Switch(direita). Fonte: [1]

Uma hipótese poderia ser utilizar os dois em simultâneo. No entanto a queda de tensão,

potenciada por dois transístores com

alto seria grande, induzindo elevados atrasos nas

portas lógicas.

No que diz respeito à integração num sistema o Header Switch traz vantagens:

Estado da Arte 13

É cada vez mais comum a utilização de vários níveis de tensão num sistema. Para

atingir este fim, é necessária a utilização de Level Shifters. Estes componentes

possuem GND comum e dois níveis diferentes de tensões de alimentação. Neste caso,

não se deve utilizar Footer Swtiches.

É mais comum pensar em “ativo” como o valor lógico “1” e desativo como o valor

lógico “0”. Neste sentido é mais fácil considerar que para desligar um bloco,

colocamos um interruptor entre o mesmo e VDD. Além disso em SoC é mais comum

blocos comunicarem utilizando protocolos “active-high”, em que o valor lógico “0” é

representado por um GND comum.

Header Switches permitem que, quando são utilizadas estratégias de isolamento que

colocam os sinais a ”0”, sejam utilizados simples transístores entre o sinal e GND.

Footer Switches podem ser vantajosos, se a área ocupada for um fator muito importante,

uma vez que transístores nMOS, apresentam maior eficiência de comutação (Ion/Iof),

resultando em menor área total necessária para fornecer a mesma corrente, comparando

com transístores pMOS.

Anel vs Rede

No caso Coarse Grained, os ST podem ser colocados à volta do bloco (Anel) ou no interior do

mesmo (Rede).

Anel

Numa implementação em anel, os ST são colocados à volta do bloco. VDD forma igualmente

um anel, enquanto que várias linhas de alimentação virtual (

bloco.

Figura 2.7 - Implementação em Anel. Fonte: [1]

, na figura 2.7) cobrem o

14 Estado da Arte

As razões que justificam o uso de uma topologia em anel são:

A distribuição da alimentação é mais simples, uma vez que os ST estão confinados a

uma área em específico e não misturados com a lógica do circuito. Existe sempre uma

separação entre VDD e a LVA (VVDD na figura 2.7), o que resulta em apenas uma

região de alimentação no interior do bloco. Isto facilita a fase de place-and-route.

Células

de

isolamento,

que

necessitam

de

alimentação

constante

podem,

simplesmente, ser colocadas no domínio de alimentação constante.

No entanto:

Registos de retenção não podem ser utilizados, uma vez que necessitam, que

no bloco existam duas regiões de alimentação distintas.

Implica um grande aumento da área do bloco.

Implica um maior número de ST para atingir as especificações relativas à

queda de tensão, uma vez que os ST estão afastados da lógica do bloco e, por

isso necessitam de fornecer energia através de interconexões longas.

Rede

Numa topologia em rede, os ST estão colocados entre a lógica do circuito, como representado

na Figura 2.8. As desvantagens da implementação em anel, tornam-se as vantagens da

topologia em rede e vice-versa.

Figura 2.8 - Implementação em rede. Fonte: [1]

Estado da Arte 15

Vantagens:

Proporcionam duas regiões de alimentação, pelo que registos de retenção podem ser

utilizados;

Os ST estão próximos da lógica, não necessitando de fornecer energia através de

interconexões de grande extensão. Deste modo, as linhas de alimentarão virtuais

podem ser implementadas em camadas inferiores de metal;

São necessários menos ST para atingir as especificações de queda de tensão;

Implica menos área, uma vez que espaços não aproveitados da lógica podem ser

utilizados para formar a rede;

Desvantagens:

Complica a implementação física;

Complica a rede de distribuição de energia.

A escolha da topologia a implementar depende de vários fatores e das características da

biblioteca de Standard Cells disponível. A melhor abordagem é experimentar as duas

topologias e analisar os resultados, de forma a escolher qual implementar.

Se considerarmos blocos que não utilizem registos de retenção, pode ser utilizada a topologia

em anel, uma vez que é mais simples. No entanto, se a área for um fator em consideração,

ou se forem necessárias duas regiões de alimentação, a topologia em rede é mais adequada.

No caso de SoC é, também, possível conciliar as duas topologias no mesmo projeto, numa

opção híbrida. Neste caso, a rede seria implementada em alto-nível, ficando o anel reservado

para blocos nos quais não seja possível efetuar modificações físicas ou que apenas necessitem

de uma região de alimentação.

2.4.4 Retenção de estado

Quando um bloco é reativado, é necessário existir um mecanismo que o coloque exatamente

no mesmo estado em que se encontrava antes de ser desligado.

16 Estado da Arte

Pode simplesmente ser induzido um reset que acione mecanismos internos do bloco e que o

faça recuperar o seu estado. Outra opção é guardar o estado numa memória externa.

No entanto quando é necessário uma rápida reativação é importante que mecanismos

internos de retenção de estado estejam implementados, de forma a agilizar o processo.

Registos de retenção

São registos que substituem os registos normais dos blocos e que contém um registo auxiliar

destinado a guardar o estado do registo principal durante a desativação. Posteriormente,

durante a reativação, o registo principal volta a ser carregado a partir do registo auxiliar.

Figura 2.9 - Registo de retenção. Fonte: [1]

Como é possível verificar na Figura 2.9, o registo auxiliar “RET”, é alimentado pela linha

principal de alimentação “VDD”, o que significa que está sempre ativo. Por seu lado o registo

principal “Master/Slave Latches”, que gera a saída “Q”, está ligado à linha de alimentação

virtual (VDD_SW, na imagem).

A grande vantagem da utilização destes registos é que, ao nível de RTL podem ser tratados

como registos normais, o que facilita a integração.

No entanto, requerem um controlo cuidado por parte do Controlador de Power Gating que

necessita de gerar os sinais “SAVE” e “RESTORE”. Além disso, implicam um aumento

significativo da área dos registos.

Scan Chains

É a alternativa à utilização de registos de retenção. Baseia-se na utilização de cadeias de

registos, semelhantes aos utilizados em métodos de teste de hardware como Boundary Scan.

Estado da Arte 17

Tem a vantagem de não implicar aumento de área, uma vez que as cadeias de teste já

implementadas podem ser reutilizadas com o objetivo de retenção de estado.

Durante a desativação do bloco, o conteúdo dos registos da cadeia são deslocados e

guardados numa memória. Durante a reativação, o contudo da memoria é carregado de volta

para os registos da cadeia.

É de salientar o fato de que as operações de deslocação e escrita/leitura na memória gastam

quantidades consideráveis de energia.

As vantagens prendem-se com o fato de não ser necessário manter uma região do circuito

alimentada para fornecer energia aos registos auxiliares usados em registos de retenção. Por

outro lado a energia gasta para guardar o estado é compensada se o bloco ficar desligado por

um tempo considerável.

2.4.5 Células de Isolamento

Como referido anteriormente, na secção 2.3, as saídas de um bloco alvo de Power Gating que

se encontra desativo podem permanecer num estado flutuante e perturbar o funcionamento

dos blocos para os quais representam sinais de entrada. É neste contexto que é necessária a

introdução de células de isolamento.

Estas células são controladas pelo Controlador de Power Gating, e quando ativas fixam os

sinais de saída a “0”, “1” ou ao valor que tinham anteriormente. Para fixar a “0” basta

utilizar um AND, ao passo que, para fixar a “1” utiliza-se um OR.

A decisão de fixar as saídas a “1” ou a “0” depende da natureza dos blocos. A melhor

abordagem é fixar os sinais num valor “neutro”, de forma a não serem interpretados como

comandos pelos blocos dos quais são entradas. Na maior parte dos sistemas, isto significa

fixar a “0”.

Outra justificação que suporta a escolha da fixação a “0” é que, quando existem dois blocos

sujeitos a Power Gating encadeados e desativados, se o bloco de destino utilizar Header

Switches e as saídas (do primeiro bloco) forem fixadas a “1”, é estabelecido um caminho

entre as saídas e GND, causando uma corrente de fuga que aumenta o consumo de energia.

Devido às razões enunciadas acima, [1] recomenda que sejam usados sinais ativos a “1”,

resets ativos “0” e fixar as saídas em “0”.

18 Estado da Arte

Figura 2.10 - Célula de isolamento que fixa a saída em "0". Fonte [1]

As células de isolamento podem desempenhar a sua função em dois sítios diferentes: no bloco

em que o sinal é gerado ou no bloco de destino.

Caso seja escolhida a 2.ª opção, é necessário colocar uma célula de isolamento em cada

bloco de destino e verificar o funcionamento de cada uma. Para casos em que o sinal seja

uma entrada de vários blocos, isto significa um aumento de área e de trabalho de verificação.

Se for escolhida a primeira opção, basta uma célula para cada sinal. No entanto, este caso

traz de volta um problema já discutido na secção anterior. Uma vez que a célula de

isolamento (à semelhança do registo auxiliar de um registo de retenção) necessita de ser

sempre alimentada são necessárias duas zonas de alimentação distintas.

Os autores de [1] recomendam que sejam usadas células de isolamento no interior do bloco

alvo de Power Gating (origem do sinal) de forma a facilitar a reutilização de IP ao nível SoC.

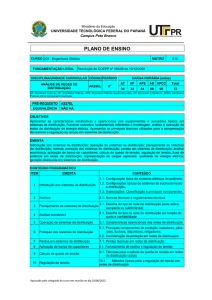

2.5 - Metodologia para implementação de Power Gating com

suporte de ferramentas Synopsys

Em [2] é descrita uma metodologia para implementação de Power Gating utilizando

ferrmentas da Synopsys. Esta metodologia, que vai desde o RTL até GDSII (Graphic Database

System II), é representada na figura 2.11.

Na primeira etapa é utilizada a ferremanta Synopsys VCS, para verificar e validar a

funcionalidade ao nível RTL, verificando os sinais de controlo, os registos de retenção e as

células de isolamento.

Estado da Arte 19

Na segunda etapa é efetuada a síntese da descrição RTL, utilizando o Synopsys Design

Compiler. Nesta fase, são definidos e passados à aplicação os domínios de alimentação do

sistema. Além da síntese lógica normal, elementos como registos de retenção e células de

isolamento são mapeados em células presentas na biblioteca.

Na terceira etapa é efetuada a síntese física, recorrendo ao Synopys IC Compiler.

Inicialmente são criadas as diferentes Power Islands e, de seguida, colocados os Sleep

Transistors. De seguida as redes de alimentação (VDD e GND) são colocadas e analisadas.

A próxima etapa é a otimização física. Nesta etapa, em que é novamente utilizado o IC

Compiler, são conectados os sinais de controlo, sintetizadas as redes que necessitem de estar

sempre alimentadas, sintetizada a clock tree e conectados os pinos secundários das redes que

estão sempre ligadas às respetivas linhas de alimentação.

Na última etapa é analisado o desempenho da implementação de Power Gating, utilizando a

ferramenta Synopsys PrimeTime-PX. É, ainda, analisada a queda de tensão provocada pelos

ST, a corrente instantânea gerada na reativação (In-Rush-Current) e os tempos de reativação

(Wake-Up Time), utilizando o Synopsys PrimeRail. Ao longo desta etapa são, também,

extraídos os elementos parasitas.

Uma metodologia semelhante será utilizada nesta dissertação, bem como a maior parte das

ferramentas.

Figura 2.11- Metodologia de implementação utilizando ferramentas Synopsys. Fonte: [2]

Capítulo 3

Proposta de Trabalho

Neste capítulo é apresentada a metodologia de trabalho que irá ser seguida ao longo do

desenvolvimento desta Dissertação. Com base nessa metodologia é elaborado um plano de

trabalho baseado num mapa de Gantt. Este plano de trabalho irá ser atualizado com o

desenvolver do projeto.

3.1 - Metodologia

Como referido na secção 1.3 o objetivo desta dissertação é reduzir o consumo de

potência numa interface de alta velocidade, sem degradação do seu desempenho. Plataforma

essa, propriedade da Synopsys Portugal.

Neste sentido, o trabalho será desenvolvido no escritório da Synopys Portugal, e iniciarse-á com a familiarização com as ferramentas Synopsys necessárias à execução do projeto.

De seguida, é necessário conhecer a interface em causa, pelo que será feito o estudo da

mesma e levantamento de dados já existentes, no que diz respeito à sua funcionalidade e

consumo de potência.

Finalizada esta fase, irá ser iniciada a implementação do método Power Gating, primeiro

ao nível do RTL e, de seguida, ao nível físico.

Feita a implementação, os resultados obtidos serão comparados com os dados já

existentes de forma a determinar se o objetivo foi cumprido.

A última etapa será documentar o trabalho efetuado e redigir a dissertação.

Proposta de Trabalho 21

3.2 - Ferramentas de trabalho

Está prevista a utilização das seguintes ferramentas da Synopsys:

Desing Compiler

É uma ferramenta de síntese lógica. Síntese lógica é uma tarefa na qual descrições RTL de

alto nível, escritas em HDL (Hardware Description Languages) são convertidas em netlists que

contêm as portas lógicas constituintes do circuito e suas interligações. A síntese é elaborada

a partir da descrição RTL, constraints e portas lógicas da biblioteca respeitante à tecnologia

alvo.

Power Compiler

É uma ferramenta de síntese que permite fazer otimizações do consumo de energia, tanto ao

nível RTL como ao nível das portas lógicas e analisar do consumo de potência apenas ao nível

das portas lógicas.

Com esta ferramenta é possível aplicar várias técnicas de baixo consumo, como é o caso de

Power Gating.

IC Compiler

É uma ferramenta de implementação física. Dispões de capacidades de place-and-route, com

suporte para projetos de baixa potência. Trata-se de, a partir, da netlist gerada na fase de

sitense lógica, gerar uma netlist em que, além das células que constituem o circuito, é

também indicado o seu posicionamento e interligações. A primeira fase (place) envolve

decidir onde colocar as células que constituem o bloco no espaço disponível. A segunda fase

(route) é responsável por estabelecer as ligações entre as células de acordo com as regras e

limitações existentes.

Star- RCXT

Ferramenta para extração de capacidades parasitas. Trata-se de obter um modelo RC do

circuito, para que as simulações representem o funcionamento real de um circuito digital. A

utilização desta ferramenta permite criar ficheiros SPEF (Standard Parasitic Exchange

Format) e SBPF (Synopsys Binary Parasitic Format) que contêm informação relativa aos

elementos parasíticos.

22 Proposta de Trabalho

Prime Time

Ferramenta que permite efetuar análises temporais estáticas ao nível das portas lógicas. O

objetico do metódo STA (Static Timing Analysis) é verificar se os requisitos temporais do

circuito estão a ser cumpridos. É verificado o cumprimento dos tempos de setup e hold, assim

como de fenómenos como clock skew e caminhos lentos que não permitam atingir a

frequência de funcionamento pretendida.

Prime Time PX

É uma extensão do Prime Time que permite analisar o consumo de potência dinâmica e

estática de um circuito. Permite uma análise em alto nível.

Prime Rail

Ferramenta que permite verificar a rede de alimentação, analisando fenómenos de

eletromigração e IR Drop. Em projetos low-power é muito útil pois permite analisar a

corrente instantânea gerada na reativação dos blocos (In-Rush-Current) e os tempos de

reativação (Wake-Up-Time), otimizando a sequência de reativação dos Sleep Transistors.

Incorpora ainda uma funcionalidade “what-if” que permite testar compromissos entre ganhos

no consumo de potência estática e os requisitos relacionados com a queda de tensão nos

Sleep Transistors.

Hercules DRC and LVS

Ferramenta para verificação física. Permite efetuar verificações DRC (Design Rule Check) e

LVS (Layout Versus Schematic). DRC permite verificar que a implementação física do circuito

cumpre certas regras específicas para a tecnologia em uso (design rules) que especificam

restrições geométricas e de conectividade entre elementos, que garantem que o circuito irá

funcionar corretamente. LVS permite verificar se o layout projetado está de acordo com o

esquemático desenhado inicialmente, ou seja, se representa o circuito desejado.

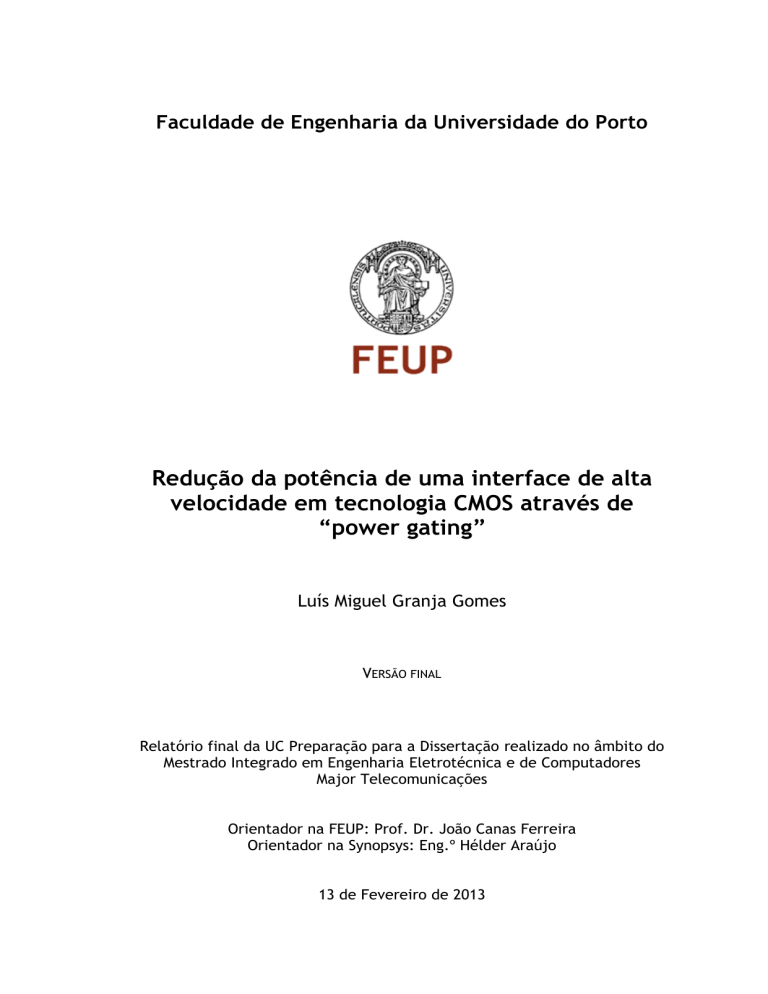

3.3 - Plano de trabalho

As etapas identificadas até ao momento e suas respetivas durações são:

1. Aprendizagem das ferramentas a usar durante a execução do projeto (4 semanas);

2. Levantamento e análise dos dados já existentes para a interface (2 semanas);

3. Análise e implementação do método de Power Gating no RTL do bloco (3 semanas);

Proposta de Trabalho 23

4. Implementação física do bloco (6 semanas);

5. Análise e comparação de resultados (2 semanas);

6. Redação da dissertação (4 semanas).

O Diagrama de Gantt associado ao plano de trabalho pode ser consultado na figura 3.1.

Proposta de Trabalho 24

Figura 3.1 - Planemanento: Diagrama de Gantt

25 Proposta de trabalho

3.4 - Resultados Esperados

No final desta dissertação é esperada a diminuição do consumo de potência da interface em

questão sem a alteração da sua funcionalidade. Será conhecido o impacto que a

implementação de Power Gating terá em aspetos como a área e a performance.

Referências 26

Referências

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

Keating, M.F., David Low Power Methodology Manual - For a System-on-Chip Design.

2007: Springer. 300.

Wang, E. Synopsys Power-gating Design Methodology based on SMIC 90nm Process.

2008.

Ping, H., et al. A Brief Survey on Power Gating Design. in 2010 10th IEEE

International Conference on Solid-State and Integrated Circuit Technology (ICSICT),

1-4 Nov. 2010. 2010. Piscataway, NJ, USA: IEEE.

WESTE, N.H.E.H., DAVID, CMOS VLSI Design - A circuits and Systems Perspective, 4th

edition. 2011: PEARSON.

Wikipedia. HDMI. [cited 2012 8/02]; Available from:

http://en.wikipedia.org/wiki/HDMI.

Dal, D. and N. Mansouri, Power optimization with power islands synthesis. IEEE

Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2009.

28(7): p. 1025-1037.

Chao-Yang, C., et al. A fast wake-up power gating technique with inducing a

balanced rush current. in 2012 IEEE International Symposium on Circuits and Systems

- ISCAS 2012, 20-23 May 2012. 2012. Piscataway, NJ, USA: IEEE.

Ku, H., L. Rong, and W. Yu. A power gating scheme for ground bounce reduction

during mode transition. in 25th International Conference on Computer Design, ICCD

2007, 7-10 Oct. 2007. 2007. Piscataway, NJ, USA: IEEE.

Kawasaki, K.i., et al. A sub-s wake-up time power gating technique with bypass

power line for rush current support. in 2008 IEEE Symposium on VLSI Circuits, 18-20

June 2008. 2008. Piscataway, NJ, USA: IEEE.

Bhatnagar, H., Advanced ASIC Chip Synthesis: Using Synopsys Design Compiler and

PrimeTime. 1999, Dordrecht, Netherlands: Kluwer Academic Publishers.

Brunvand, E., Digital VLSI Chip Design with Cadence and Synopsys CAD Tools. 2010:

Pearson.

Butzen, P.F.R., Renato Perez, Leakage Current in Sub-Micrometer CMOS Gates.

Universidade Federal do Rio Grande do Sul.

Hyung-Ock, K. and S. Youngsoo, Semicustom design methodology of power gated

circuits for low leakage applications. IEEE Transactions on Circuits and Systems--II:

Analog and Digital Signal Processing, 2007. 54(6): p. 512-16.

Jotwani, R., et al., An x86-64 Core in 32 nm SOI CMOS. IEEE Journal of Solid-State

Circuits, 2011. 46(1): p. 162-72.

Kyung Ki, K., N. Haiqing, and C. Ken. Power gating for ultra-low voltage nanometer

ICs. in 2010 IEEE International Symposium on Circuits and Systems. ISCAS 2010, 30

May-2 June 2010. 2010. Piscataway, NJ, USA: IEEE.

Nebel, W.T., Jurgen, RT-Level Power-Gating Models optimizing Dynamic LeakageManagement. 2012.

Rabaey, J.M., Digital Integrated Circuits: A Design Perspective, 1996, Prentice

Hall,Inc: Upper Sadle Rive. p. 700.

Sedra, A.S.S., Kenneth c., Microelectronic Circuits, 5th Edition. 2004, Oxford: Oxford

University Press.

Referências 27

19.

20.

[1-20]

Suji, C.C.G., S. Maragatharaj, and R. Hemima. Performance analysis of power gating

designs in low power VLSI circuits. in 2011 - International Conference on Signal

Processing, Communication, Computing and Networking Technologies, ICSCCN-2011,

July 21, 2011 - July 22, 2011. 2011. Thuckalay, India: IEEE Computer Society.

Zhigang, H., et al. Microarchitectural techniques for power gating of execution

units. in Proceedings of the 2004 International Symposium on Low Power Electronics

and Design, 9-11 Aug. 2004. 2004. New York, NY, USA: ACM.