Universidade do Vale do Paraíba

Faculdade de Engenharias Urbanismo e Arquitetura

Curso de Engenharia Elétrica/Eletrônica

GIGA DE TESTES PARA RIB

Teste dos circuitos DCDC e RS485

FÁBIO UMEHARA

MARCOS PAULO A. VILLAS-BÔAS

Relatório do Trabalho de Conclusão de Curso

apresentado à Banca Avaliadora da Faculdade de

Engenharias Urbanismo e Arquitetura da

Universidade do Vale do Paraíba, como parte dos

requisitos para obtenção do Título de Bacharel em

Engenharia Elétrica/Eletrônica.

São José dos Campos – SP

Novembro 2014

GIGA DE TESTES PARA RIB

FÁBIO UMEHARA

MARCOS PAULO A. VILLAS-BÔAS

Banca Avaliadora

Presidente Alderico Rodrigues de Paula Junior

Orientador Alessandro Corrêa Mendes

Membro A

Membro B

______________________________________

Alessandro Corrêa Mendes

Orientador Acadêmico

______________________________________

José Ricardo Abalde Guedes

Coordenador da Disciplina de TCC

Data:

Agradecimentos

Agradecemos primeiramente

a Deus, Criador de todas as coisas.

Agradecimento especial às nossas

famílias que diretamente contribuíram

para a realização deste trabalho, aos

colegas, aos professores e os

colaboradores que sempre estiveram

prontos a nos ajudar.

A todos, nosso “muito obrigado”.

Resumo

Foi desenvolvido um projeto de uma estação de teste para uma placa específica

da empresa Ericsson Telecomunicações S.A. de São José dos Campos, tendo o nome

técnico RIB (Placa de Interface de Rádio, do inglês “Radio Interface Board”). A RIB é

uma placa interna de uma RRU (Unidade de Rádio Remoto, do inglês “Remote Radio

Unit”) e tem como função realizar a interface de sinais analógicos e digitais entre a RRU

e a BTS (Estação Base de Transmissão, do inglês “Base Transceiver Station”). A placa

possui como principais conexões a Ethernet, transceptores ópticos, sinais de alarmes

externo e conectores usados somente em instalações e manutenções da RRU, assim,

através do microcontrolador da família MSP430 (Texas Instruments) desenvolveu-se uma

estação em que são testados funcionalmente os sinais de comunicações e alarmes

externos, e tendo como principais objetivos, abranger todos os tipos de simulações

possíveis semelhantes ao seu funcionamento em campo e ao mesmo tempo minimizar o

custo do projeto com soluções simples, porém eficaz. Neste projeto serão abordados os

testes nos circuitos DCDC e RS485 da RIB.

Palavras-chave: Microcontrolador; MSP430; Ethernet; RS232; Fibra-óptica.

Abstract

Develops a design of a test station for a specific board of the company Ericsson

Telecommunications SA of São José dos Campos, the technical name is RIB (Radio

Interface Board). The RIB is an internal board of RRU (Remote Radio Unit) and has the

function to interface of analogue and digital signals between the RRU and BTS (Base

Transceiver Station). The board has as main connections to Ethernet, optical transceivers,

external alarm signals and connectors used only in installation and maintenance of RRU,

thus by the MSP430 microcontroller family (Texas Instruments) developed a station

where are functionally tested signals communications and external alarms, and having as

main objectives reach all similar functions like field operation while minimizing possible

simulations project cost with simple but effective solutions. In this project will be covered

the test in the circuits DCDC and RS485 of the RIB.

Keywords: Microcontroller; MSP430; Ethernet; RS232; Fiber-optics.

Sumário

BANCA AVALIADORA ............................................................................................... II

AGRADECIMENTOS ................................................................................................ III

RESUMO ....................................................................................................................... IV

ABSTRACT .................................................................................................................... V

ÍNDICE DE FIGURAS .............................................................................................VIII

ÍNDICE DE TABELAS ................................................................................................. X

LISTA DE ABREVIAÇÕES........................................................................................ XI

INTRODUÇÃO ............................................................................................................. 12

1.1 ANTECEDENTES .................................................................................................. 12

1.2 DESCRIÇÃO DO PROBLEMA ........................................................................... 14

1.3 OBJETIVO .............................................................................................................. 15

1.4 RESTRIÇÕES......................................................................................................... 15

1.5 ORGANIZAÇÃO O TRABALHO........................................................................ 15

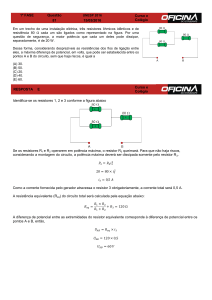

EMBASAMENTO TEÓRICO .................................................................................... 16

2.1 CONHECIMENTOS BÁSICOS SOBRE A RIB ................................................. 16

2.2 CONCEITOS BÁSICOS ........................................................................................ 17

2.2.1 MSP-EXP430F5529LP ...................................................................................... 17

2.2.2 Efeito Hall .......................................................................................................... 19

2.2.3 COMUNICAÇÃO RS232.................................................................................... 20

2.2.4 Conversores de nível TTL / RS232 .................................................................... 25

2.2.5 COMUNICAÇÃO RS485.................................................................................... 26

2.3 METODOLOGIA ................................................................................................... 27

DESENVOLVIMENTO ............................................................................................... 30

3.1 MATERIAIS ........................................................................................................... 30

3.1.1 Circuito Principal ............................................................................................... 30

3.1.2 Circuito DCDC................................................................................................... 33

3.1.3 Circuito RS485 ................................................................................................... 34

3.2 PROJETO DETALHADO ..................................................................................... 35

3.3 PROGRAMAÇÃO.................................................................................................. 40

3.4 FLUXOGRAMA ..................................................................................................... 41

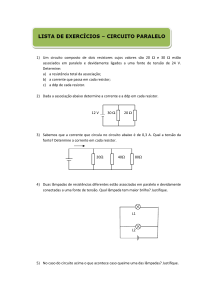

RESULTADOS ............................................................................................................. 43

4.1 CIRCUITO TESTE DCDC.................................................................................... 43

4.1.1 Teste funcional ................................................................................................... 43

4.1.2 Teste de Confiabilidade...................................................................................... 43

4.2 TESTE RS-485 ........................................................................................................ 44

4.2.1 Teste Funcional .................................................................................................. 44

4.2.2 Teste de confiabilidade ...................................................................................... 44

4.3 PLACAS CONFECCIONADAS ........................................................................... 45

CONCLUSÕES ............................................................................................................. 48

REFERÊNCIAS BIBLIOGRÁFICAS ........................................................................ 49

ANEXO 1 – ESQUEMA ELÉTRICO......................................................................... 50

ANEXO 2 – CÓDIGO “MAIN” .................................................................................. 56

Índice de Figuras

Figura 1 – Exemplo de Instalação de RRUS nas configurações estrela e cascata .......... 14

Figura 2 – Desenho simplificado dos conectores da RIB ............................................... 16

Figura 3 - MSP-EXP430F5529LP LaunchPad ............................................................... 18

Figura 4 - diagrama para o estudo do efeito “hall” ......................................................... 19

Figura 5 - EIA232 em sua aplicação mais comum ......................................................... 22

Figura 6 - Pinagem completa do padrão EIA232 para dispositivo DTE (usualmente um

PC) ........................................................................................................................... 23

Figura 7 - Pinagem completa do padrão EIA232 para dispositivo DCE (usualmente um

modem) .................................................................................................................... 24

Figura 8 - Convenção utilizada para os sinais mais comuns. ......................................... 25

Figura 9 - Estados lógicos da linha A e B de acordo com o dado que o transmissor

deseja enviar ............................................................................................................ 27

Figura 10 – Diagrama esquemático da Giga de Teste da placa RIB .............................. 28

Figura 11 – Bloco Principal ............................................................................................ 36

Figura 12 – Bloco DCDC ............................................................................................... 37

Figura 13 – Pinagem do CI Hall ACS 712 ..................................................................... 38

Figura 14 - Bloco RS485 / Ethernet................................................................................ 38

Figura 15 - PCB Circuito DCDC (TOP) ......................................................................... 45

Figura 16 - PCB Circuito DCDC (BOT) ........................................................................ 45

Figura 17 - PCB Circuito RS485/Ethernet (TOP) .......................................................... 46

Figura 18 - PCB Circuito RS485/Ethernet (BOT) .......................................................... 46

Figura 19 – Circuito Estação RIB parcialmente completo utilizado para testes ............ 47

Índice de Tabelas

Tabela 1 Estudo dos principais defeitos possíveis na RIB ............................................. 35

Tabela 2 – Resultados dos testes no circuito DCDC ...................................................... 43

Tabela 3 – Resultados dos testes no circuito RS-485 ..................................................... 44

Lista de Abreviações

RIB

Radio Interface Board

RRUS

Remote Radio Unity

RBS

Radio Base Station

BTS

Base Transmission Station

HW

Hardware

LED

Light Emitting Diode

NC

Not connected

OVP

Over Voltage Protection

PCB

Printed Circuit Board

RET

Remote Electrical Tilt

SFP

Small Form Pluggable transceiver

XALM

External Alarm

CI

Circuito integrado

AC

Corrente Alternada

DC

Corrente Contínua

Capítulo 1

Introdução

1.1 Antecedentes

A RIB (Placa de Interface de Rádio, do inglês “Radio Interface Board”), produzida

atualmente na empresa Ericsson, é uma placa interna essencial das RRUS (Unidades de

Rádio Remoto, do inglês “Remote Radio Unity”) que são capazes de ampliar o alcance

da RBS (Estação Rádio-Base, o inglês “Radio Base Station”) em dezenas de quilômetros

e, devido a isso, é um componente muito importante e faz parte das tecnologias que

possuem o papel de solucionar a problemática do aumento recente de demanda de banda

larga e tráfego de redes móveis.

O tráfego de dados móveis atualmente já ultrapassou o de voz e continua

crescendo segundo as tendências globais . Em regiões como Oriente Médio, África e

América Latina o tráfego de banda larga móvel tem quase que dobrado a cada ano e a

projeção para os próximos anos indica um crescimento exponencial [2]. A Ericsson prevê

um aumento de dez vezes no tráfego de dados até 2019 em relação aos dados de 2013,

resultado de vários fatores, como o crescimento global em dispositivos sem fio em redes,

o aumento no uso de “smartphones”, e a implantação de redes mais rápidas que os

padrões atuais 2G e 3G em todo o mundo [3].

Os serviços de 4G / LTE e 5G prometem a solução para o aumento da demanda

com a ampliação da largura de banda, o que de fato, é muito importante, no entanto cada

vez mais no meio técnico-científico tem crescido também outra escola de pensamento

que sugere como solução uma melhoria na eficiência das redes e defende o uso de um

modelo híbrido (redes heterogêneas ou “Het Nets”), geralmente composto de várias

tecnologias de acesso de rádio, diferentes arquiteturas, soluções de transmissão e estações

rádio-base com vários níveis de potência de transmissão. As redes heterogêneas fazem o

“offload” da rede e favorecem a cobertura “indoor”, pois funcionam com uma cobertura

de pequenas células (“small cells”) subjacente à cobertura de células macro e com a

integração de tecnologia Wi-Fi [4].

Para que se compreenda melhor o problema da ineficiência da rede convém citar

o exemplo recente quando na abertura da Copa do Mundo, na partida entre Brasil e

Croácia, segundo a SindiTelebrasil, a tecnologia 3G teve picos de tráfego e

congestionamentos momentâneos devido a grande concentração de usuários conectados

12

em um mesmo lugar [5]. E vale ressaltar que na arena de São Paulo, a cobertura “indoor”

contava com 337 antenas interligadas por 12 quilômetros de fibras ópticas e a área externa

do estádio ainda foi reforçada com mais 22 antenas móveis.

Para os sistemas públicos, especialmente ao ar livre e se a rede macro existente é

demasiado escassa para atender a demanda de tráfego e a cobertura adequada, a

implantação de nós de baixa potência ao ar livre é o mais adequado, pois podem oferecer

cobertura a uma vasta área com vários edifícios e abranger vários locais fechados

(“indoor”).

Existem vários tipos de nós de baixa potência, cada um com exigências diferentes

do “backhaul” (infraestrutura de conexão dos pontos de concentração da rede de acesso

com o núcleo de alta capacidade de transmissão da rede, também conhecido como

“backbone”) [6]. Para redes onde o “backhaul” tem características de baixa latência e alta

capacidade, a implantação de RRUS é a abordagem mais praticada.

A RRU tem o potencial de melhorar o desempenho geral da rede e é instalada

através de uma configuração estreita entre os nós exemplificada na Figura 1 e que

geralmente compreende antenas para enviar e receber a transmissão de rádio, bem como

uma unidade de processamento de frequência de rádio. Uma unidade central de controle

recebe os sinais de várias RRUS e realiza os processamentos de sinal e de camada

superior. A unidade de controle e as RRUS devem ser conectadas diretamente com uma

baixa latência e interface de alta capacidade, por isso um “backhaul” baseado em fibra

óptica é o mais adequado para a implantação de RRUS.

A RIB tem como principal função realizar a interface de sinais analógicos e

digitais entre a RRU e a BTS (Estação Base de Transmissão, do inglês “Base Transceiver

Station”). A placa possui conectores utilizados na instalação e manutenção da RRU e

trabalha com sinal digital RS485, conexões no padrão Ethernet, transceptores ópticos e

sinal analógico RET VCC.

13

Figura 1 – Exemplo de Instalação de RRUS nas configurações estrela e cascata

1.2 Descrição do problema

Devido à sua complexidade e a importância da RIB na RRU, torna-se

indispensável que haja planos de amostragem e procedimentos para inspeção por

atributos dos lotes de RIBs, ou seja, deve haver um teste simples na linha de produção

segundo o qual a unidade de produto seja classificada como defeituosa ou não em relação

a um dado requisito ou conjunto de requisitos.

Atualmente a inspeção de um lote na linha de produção é feita com a montagem

completa de uma RRU, e em seguida são feitos vários ensaios das principais funções do

equipamento para verificar se a RIB não apresenta defeitos.

Apesar da eficácia deste processo, ele ocasiona minutos de linha parada enquanto

se espera o resultado do teste, e consequentemente, diminui a produtividade na linha.

No mercado não foram encontrados equipamentos específicos que atendessem as

necessidades do teste da RIB. Por se tratar de uma placa muito singular, exige-se um

dispositivo fabricado segundo as necessidades do processo que seja simples, prático e de

baixo custo.

14

1.3 Objetivo

Estudar o funcionamento da RIB para projetar uma estação de teste (Giga de

Teste) de baixo custo que simule e teste as funções dos circuitos DCDC e RS485 da RIB.

Melhorar a metodologia de inspeção no processo de fabricação da RIB,

apresentando ao usuário o resultado do teste ao usuário de maneira mais simples.

Obter resultados mais rápidos no processo de inspeção da RIB para liberar os lotes

em menos tempo, reduzindo o tempo de linha parada e consequentemente o custo da

produção da RIB.

1.4 Restrições

Este trabalho irá se dedicar somente ao estudo dos circuitos DCDC e RS485 da

RIB, não se aprofundando nos testes de outros blocos da RIB tais como o Óptico e o de

padrão Ethernet.

Como já foi esclarecido, este projeto tem como finalidade a redução de custo no

processo de fabricação da RIB, portanto a principal restrição para este trabalho é que o

custo da Giga de Teste não seja demasiado elevado, prejudicando assim sua viabilidade

para a empresa.

A placa RIB, suas especificações (“datasheets”), normas de processo, os

documentos e equipamentos envolvidos em seu processo de fabricação e nem mesmo o

protótipo da Giga de Teste não puderam ser retirados da empresa Ericsson por motivo de

sigilo empresarial. No entanto, com autorização das gerências da empresa, os estudos

puderam ser realizados nas dependências da Ericsson e com isto os autores conseguiram

reunir neste trabalho todo o conhecimento adquirido com esta experiência.

1.5 Organização o Trabalho

O capítulo 2 apresenta o embasamento teórico do funcionamento da RIB e da Giga

de Teste e os principais conceitos utilizados na solução do problema. O capítulo 3

apresenta os materiais e a metodologia utilizada no processo de teste dos circuitos DCDC

e RS485 da RIB no projeto da Giga de Teste. O capítulo 4 apresenta os resultados obtidos

e faz uma discussão usando-se dos conhecimentos adquiridos. O último capítulo traz as

conclusões gerais sobre o projeto e apresenta as proposições para novos estudos e futuros

desafios.

15

Capítulo 2

Embasamento Teórico

2.1 Conhecimentos básicos sobre a RIB

A RIB (Placa de Interface de Rádio) tem como principal função realizar a

interface de sinais analógicos e digitais na instalação e manutenção da RRU, por isso

trabalha com diferentes tipos de sinais e níveis de tensão simultaneamente e possui vários

conectores, que estão listados a seguir e podem ser vista na Figura 2:

RJ-45 (8 pinos)

RET (6 pinos)

XALM (4 pinos)

Conector de teste (24 pinos)

SFP A (20 pinos)

SFP B (20 pinos)

Conector RIB (80 pinos)

Figura 2 – Desenho simplificado dos conectores da RIB

16

Para facilitar o seu estudo podemos dividir a RIB em quatro circuitos, de acordo

com os sinais e conectores envolvidos: circuito de sinal digital RS485, circuito de

comunicação no padrão Ethernet, circuito de comunicação óptica e circuito de sinal

analógico RET VCC.

O procedimento de inspeção da RIB na linha de produção deve testar cada um

destes quatro circuitos e o requisito para que a amostra e, assim também, o lote sejam

classificados como não defeituosos é que todos os quatro circuitos não apresentem falha,

ou seja, se um ou mais destes circuitos apresentar mau funcionamento, o lote deve ser

classificado como defeituoso e não pode ser liberado para a próxima fase.

Como já foi mencionado na introdução, este trabalho irá se dedicar somente ao

estudo de como serão testados na Giga de Teste os circuitos DCDC e RS485 da RIB. Este

processo envolve como componentes principais dois microcontroladores da família

MSP430 (Texas Instruments), um CI que faz a medição indireta da corrente do circuito

mensurando o efeito “hall” e um módulo conversor de sinal digital RS232 / RS485.

2.2 Conceitos Básicos

2.2.1 MSP-EXP430F5529LP

O MSP-EXP430F5529LP LaunchPad conforme a Figura 3, ou simplesmente

“F5529 LaunchPad”, é um kit de desenvolvimento para o microcontrolador USB

MSP430F5529 que oferece emulação “on-board” para programação e “debug” e dispõe

de LEDs para simplificar a interface com o usuário.

O microcontrolador 16-bit MSP430F5529 tem 128KB de memória “flash”, 8KB

RAM e velocidade de processamento de 25MHz, USB integrado e a possibilidade de

trabalhar com diversos periféricos, a critério do usuário. Sua tensão de operação é de 1,8V

a 3,6V.

17

Figura 3 - MSP-EXP430F5529LP LaunchPad

Seus principais recursos são:

cinco “timers”

sistema de “clock” até 25MHz

pode trabalhar com até quatro interfaces de comunicação serial (SPI,

UART, I²C).

conversor analógico-digital (AD) de 12 bits

entradas analógicas e digitais com função de “pull up” e ”pull down”

interno.

A Giga de Teste da RIB utiliza dois kits de microcontroladores

MSP-EXP430F5529LP LaunchPad nos testes dos cicruitos DCDC e RS485, que serão

aqui representados por MSP_A e MSP_B.

18

2.2.2 Efeito Hall

Em 1879, foi publicado um artigo escrito por Hall, que tinha como objetivo

explicar um fenômeno muito interessante que acontecia com circuitos elétricos quando

estes eram submetidos a um campo magnético: a presença de uma diferença de potencial.

Na época, não se conhecia muito sobre a corrente elétrica; sabia-se da existência da

mesma, mas suas características e propriedades, bem como sua constituição, eram apenas

especulações.

O fenômeno descrito, segundo Hall, era mais perceptível se fosse inserido no

circuito elétrico uma chapa metálica, ou um material semicondutor. No experimento

realizado por Hall em 1879, ele utilizou uma placa fina de germânio, ou seja, um material

semicondutor. Conectando-se um voltímetro (instrumento para medir diferença de

potencial) na placa, Hall constatou a existência de uma tensão, denominada tensão “hall”.

Este efeito, a existência de uma tensão no material quando o mesmo é submetido a um

campo magnético, é conhecido como efeito “hall”.

Figura 4 - diagrama para o estudo do efeito “hall”

A Figura 4 representa um diagrama para o estudo do efeito “hall”. O diagrama

ilustra uma bateria (5) que alimenta o elemento ou sensor “hall” (2) com o fluxo de

19

elétrons (1) no sentido real (e não convencional) e dois imãs (3) aplicam um campo

magnético (4) na direção perpendicular ao plano do sensor “hall”. Conforme indicado no

quadro “A” o sensor “hall” recebe uma carga negativa na extremidade superior

(simbolizado pela cor azul) e uma positiva na extremidade inferior (cor vermelha).

Nos quadros “B” e “C”, observa-se que a inversão da corrente elétrica ou do

campo magnético causam a polarização reversa. Invertendo ambas, corrente e campo

magnético no quadro “D”, o elemento “hall” novamente assume a carga negativa na

extremidade superior.

Este efeito foi descoberto em 1879 por Edwin H. Hall durante seu doutorado em

física sob a supervisão de Henry A. Rowland na Universidade Johns Hopkins em

Baltimore, Maryland. Durante seus estudos experimentais sobre a influência do campo

magnético nos portadores de carga da corrente elétrica ele determinou a existência de

portadores de carga negativa muitos anos antes da descoberta dos elétrons por J. J.

Thompson.

O efeito Hall permite a obtenção de dois resultados importantes: o sinal da carga

dos portadores, apartir da medição da diferença de potencial entre as superfícies superior

e inferior, e a densidade de portadores [7].

2.2.3 Comunicação RS232

Quando se trata de transferência de dados, diversas tecnologias ainda utilizam o

sistema de comunicação serial, na qual os bits de dados são enviados sequencialmente

através de um canal de comunicação ou barramento [9]. Existem, no entanto, diversos

parâmetros a se definir, como em qualquer outro tipo de comunicação, tais como níveis

de tensão, codificação do sinal, frequência de transmissão e até mesmo o tipo de conexão

mecânica. Devido a isso normalmente trabalha-se adotando um padrão de interface, que

nada mais é que um grupo de normas para regulamentar um determinado tipo de

comunicação.

No início de 1960, um comitê de padrões, hoje conhecida como a Electronic

Industries Association (EIA), desenvolveu um padrão de interface para transferência

serial de dados entre equipamentos. Naquele tempo, a comunicação de dados

compreendia a troca de dados digitais entre um computador central (mainframe) e

terminais de computador remotos, ou entre dois terminais sem o envolvimento do

computador. Estes dispositivos poderiam ser conectados através de linha telefônica, e

20

consequentemente necessitavam um modem em cada lado para fazer a decodificação dos

sinais [1].

Dessas ideias nasceu o padrão RS232. “RS” é uma abreviação de “Recommended

Standard” (padrão recomendado). As principais normas que o padrão RS232 abrange

envolvem:

Funções de cada circuito no conector da interface

Características elétricas, como taxa de sinalização, níveis de tensão,

comportamento de curto-circuito e carga máxima da capacitância.

Características mecânicas da interface, como tipos de conectores e identificação

dos pinos.

Todavia o padrão RS232 não define elementos como:

Taxas de bit para transmissão, apesar de o padrão ser destinado para taxas de bits

menores que 20.000 bits por segundo.

Codificação de caracteres (por exemplo, ASCII, código Baudot ou EBCDIC)

Enquadramento dos caracteres no fluxo de dados (bits por caractere, bits de início

e parada, paridade)

Protocolos para detecção de erros ou algoritmos para compressão de dados

Fornecimento de energia para dispositivos externos

Ao longo de cinquenta anos desde que este padrão foi desenvolvido, a EIA

publicou três modificações, sendo o mais recente o padrão EIA232F introduzido em 1997.

Apesar dessas revisões, as normas desse padrão sofreram apenas pequenas alterações e a

designação mais utilizada ainda é RS232. Hoje este padrão é muito utilizado pela sua

simplicidade e possibilidade de ser aplicado tanto em equipamentos novos quanto nos

mais antigos.

As maiores dificuldades encontradas pelos usuários na utilização deste padrão de

interface são relativamente pequenas, pois apresentam pequeno risco aos “drivers” e CIs

e incluem pelo menos um dos seguintes fatores:

A ausência ou conexão errada de sinais de controle resultam em estouro do buffer

(“overflow”) ou travamento da comunicação.

21

Função incorreta de comunicação para o cabo em uso resulta em inversão das

linhas de transmissão e recepção, bem como a inversão de uma ou mais linhas de

controle (“handshaking”).

O cabo de comunicação deve limitar-se a aproximadamente dez metros de

comprimento e deve ser isolado de outros cabos de potência, para evitar o

aparecimento de interferências.

Se aplicada em sua totalidade a EIA232 conforme a Figura 5, o equipamento que

faz o processamento dos sinais é chamado DTE (Data Terminal Equipment – usualmente

um computador ou terminal), tem um conector DB25 macho, e utiliza 22 dos 25 pinos

disponíveis para sinais e o terra. O equipamento que faz a conexão (normalmente uma

interface com a linha telefônica) é denominado de DCE (Data Circuit-terminating

Equipment – usualmente um modem), tem um conector DB25 fêmea, e utiliza os mesmos

22 pinos disponíveis para sinais e terra. Um cabo de conexão entre dispositivos DTE e

DCE contém ligações em paralelo, não necessitando mudanças na conexão de pinos.

Figura 5 - EIA232 em sua aplicação mais comum

Se o dispositivo DCE for mesmo um modem diversos sinais são necessários para

a conexão. Normalmente isso não acontece e o DCE não é um modem, ou dois

dispositivos DTE são conectados diretamente e poucos sinais são necessários.

Deve-se notar que nas figuras 6 e 7 existe um segundo canal que inclui um

conjunto de sinais de controle duplicados (“Secundary”). Este canal secundário fornece

sinais de gerenciamento do modem remoto, habilitando a mudança de taxa de transmissão

22

durante a comunicação, efetuando um pedido de retransmissão se erros de paridade forem

detectados, e outras funções de controle.

Figura 6 - Pinagem completa do padrão EIA232 para dispositivo DTE (usualmente um

PC)

Os sinais de temporização de transmissão e recepção são utilizados somente

quando o protocolo de transmissão utilizado for síncrono. Para protocolos assíncronos,

padrão 8 bits, os sinais de temporização externos são desnecessários.

Os nomes dos sinais que implicam em uma direção, como “Transmit Data” e

“Receive Data”, são nomeados do ponto de vista dos dispositivos DTE, conforme a

23

Figura 6. Se a norma EIA232 for seguida a risca, estes sinais terão o mesmo nome e o

mesmo número de pino do lado do DCE, conforme a Figura 7. Entretanto, normalmente

isto não é feito na prática pela maioria dos engenheiros, provavelmente porque em alguns

casos torna-se difícil definir quem é o DTE e quem é o DCE.

Figura 7 - Pinagem completa do padrão EIA232 para dispositivo DCE (usualmente um

modem)

O Pino 7, o pino 1, e a carcaça tem função de “ground” e “shield”. O cabeamento

possui caminhos diferentes para cada um, no entanto internamente muitas vezes conectase o pino 1 e o cabo da carcaça (“shield”) ao sinal de terra no pino 7 [8].

24

Todos os sinais são referenciados a um terra comum que é definido pela tensão no

pino 7 e este pode ou não ser conectado ao terra do dispositivo DCE [8]. Essa é uma das

principais características que fazem o RS232 ser diferente de muitos outros padrões e é

também a razão deste padrão apresentar maior ruído em relação aos outros.

Figura 8 - Convenção utilizada para os sinais mais comuns.

Sinais com tensão entre -3 volts e -25 volts com relação ao terra (pino 7) são

considerados nível lógico “1” , e tensões entre +3 volts e +25 volts são considerados nível

lógico “0”. A faixa de tensões entre -3 volts e +3 volts é considerada uma região de

transição para o qual o estado do sinal é indefinido [8].

Os demais pinos não citados no texto seguem a convenção utilizada conforme a

Figura 8.

2.2.4 Conversores de nível TTL / RS232

A maioria dos equipamentos digitais, inclusive os microcontroladores utilizados

na Giga de Teste, utilizam níveis TTL ou CMOS, portanto, para conectar um equipamento

digital a uma interface RS232 é necessário transformar níveis TTL (0 a 5 volts) em RS232

e vice-versa com o auxílio de conversores de nível.

25

Existe uma variedade grande de equipamentos digitais que utilizam o “driver”

1488 (TTL => RS232) e o “receiver” 1489 (RS232 => TTL). Estes CIs contém quatro

inversores de um mesmo tipo, sejam “drivers” ou “receivers”. O “driver” necessita de

duas fontes de alimentação +7,5 volts a +15 volts e –7,5 volts a –15 volts, o que é um

problema para sistemas que utilizam somente uma fonte de +5 volts.

Em vista disso, outro CI que está sendo amplamente utilizado é o MAX232 (da

Maxim) que inclui um circuito de “charge pump” capaz de gerar tensões de –10 volts e

+10 volts a partir de uma fonte de alimentação simples de +5 volts, bastando para isso

alguns capacitores externos. Este CI também tem 2 “receivers” e 2 “drivers” no mesmo

encapsulamento. Nos casos onde serão implementados somente as linhas de transmissão

e de recepção de dados, não seria necessário 2 chips e fontes de alimentação extras.

2.2.5 Comunicação RS485

A comunicação RS485 surgiu a partir do padrão RS232, mas funciona no que se

pode chamar de “modo diferencial”, ou seja, a diferença entre as tensões na linha resulta

se o mestre está transmitindo “1” ou “0” e não há um sinal terra de referência como em

RS232.

A RS485 suporta a comunicação “half-duplex” e “full-duplex”; para a primeira

há necessidade da utilização de um cabo com um par trançado enquanto no segundo são

necessários dois pares de cabos.

Este tipo de comunicação alcança grandes distâncias de cabo. Podemos chegar

até 1200m de cabo funcionando a 9600 bps. Conforme o “baud-rate” aumenta, o tamanho

do cabo diminui.

Este padrão possibilita o trabalho em rede e utiliza a estrutura mestre-escravo onde

há uma máquina que faz a pergunta e os escravos respondem de acordo com o frame que

chegar se estiver com o mesmo endereço ajustado no escravo.

O cabo de comunicação 485 é composto de dois fios, um destes é chamado de A

e o outro de B. Os estados lógicos da linha A e B variam de acordo com o dado que o

transmissor deseja enviar, conforme a Figura 9.

Quando o transmissor (INPUT D) fica em alto, a linha A fica mais positiva que a

B e o inverso ocorre quando o estado inverte. Note-se também que também há uma linha

de controle chamada DE e quando a mesma fica em nível lógico baixo, o barramento fica

em alta-impedância.

26

Para que o receptor identifique um sinal válido, a diferença entre os terminais A e

B deve ser maior que 200 mV. Entre 200mV e –200mV o sinal é indefinido.

Figura 9 - Estados lógicos da linha A e B de acordo com o dado que o transmissor

deseja enviar

2.3 Metodologia

Antes de iniciar o procedimento de inspeção da RIB com a Giga de Teste, o

operador liga a fonte alimentação (5V) para energizar os microcontroladores da estação

e encaixa a RIB que será testada.

27

Figura 10 – Diagrama esquemático da Giga de Teste da placa RIB

A Figura 10 representa o diagrama de blocos da Giga de Teste. Para dar início ao

teste pressiona-se o botão START. O microcontrolador chaveia o circuito do regulador

de tensão LM317 que energiza a RIB com 5V. Se houver curto-circuito o próprio LM317,

que possui proteção de sobrecorrente, abre o circuito instantaneamente. A corrente que

entra na RIB é medida por efeito hall pelo circuito do ACS7/2T. Se a corrente medida

pelo microcontrolador for nula indica que a RIB é defeituosa, o teste é encerrado e o LED

“FAIL” é aceso; e se a corente estiver dentro dos limites normais de operação, é iniciado

o ciclo de testes nos principais circuitos e conectores da RIB.

Logo em seguida inicia-se o teste do circuito RS485 da RIB. O MSP_A enviará

um dado pra o MSP_B através do circuito RS485 da RIB, se o MSP_B receber o dado

corretamente, ele responderá com outro dado novamente através da RIB e o MSP_A

processará este dado para verificar se chegou corretamente. Caso haja alguma divergência

na comunicação entre os microcontroladores, o teste é encerrado e o LED “FAIL” é aceso.

28

Se os dados forem recebidos corretamente, conclui-se que o circuito RS485 não possui

defeitos e passa-se para a próxima etapa de teste.

Ao final do teste, depois de todas as etapas, se em momento algum a amostra não

apresentar defeito, o LED “PASS” é aceso e o usuário pode remover a RIB da Giga de

Teste.

O botão RESET permite que o usuário reinicie um teste a qualquer instante.

29

Capítulo 3

Desenvolvimento

3.1 Materiais

O custo total desse projeto foi de R$230,00; os principais módulos e os kits dos

microcontroladores foram adquiridos no exterior e a compra foi feita via internet. O

custo do fret foi incluído no custo total.

3.1.1 Circuito Principal

Peça

C2

Valor

100nF

Dispositivo

C-EUC0402K

Ecapsulamento

C0402K

C3

100nF

C-EUC0402K

C0402K

C4

100nF

C-EUC0402K

C0402K

C5

100nF

C-EUC0402K

C0402K

DCDC

10PIN

DRIVE

RS

IC2

10 PIN

4052N

4052N

-2510 PAK100/250010

-2510 PAK100/250010

DIL16

IC3

4052N

4052N

DIL16

JP1

ETH_LOOP_

0

ETH_LOOP_

1

UART_MSP

430

CTRL_LED1

CTRL_LED2

JP1E

JP1

Descrição

CAPACITOR,

European symbol

CAPACITOR,

European symbol

CAPACITOR,

European symbol

CAPACITOR,

European symbol

3M (TM) Pak 100

4-Wall Header

3M (TM) Pak 100

4-Wall Header

Dual 4-channel

ANALOG

MULTIPLEXER

Dual 4-channel

ANALOG

MULTIPLEXER

JUMPER

JP1E

JP1

JUMPER

JP2Q

JP2Q

JUMPER

JP1E

JP1E

SSW-102-02-S-D

JP1

JP1

SSW-102-02-SD

SSW-102-02-S-D

SSW-102-02-SD

LEDCHIPLED_08

05

CHIPLED_0805

JUMPER

JUMPER

THROUGH-HOLE

.025" SQ POST

SOCKET

THROUGH-HOLE

.025" SQ POST

SOCKET

LED

JP2

JP3

JP4

JP5

JP8

JP9

LED1

UART_CTR

L1

30

LED2

OPTCO

_A

OPTCO

_B

PAINE

L

R1

UART_CTR

L2

20 PIN

LEDCHIPLED_08 CHIPLED_0805

05

-2520 PAK100/250020

20 PIN

-2520 PAK100/250020

-2510

-2510 PAK100/250010

33 R-US_R0402

R0402

R4

33 R-US_R0402

R0402

R6

2k2

R-US_R0402

R0402

R7

2k2

R-US_R0402

R0402

33 R-US_R0402

R0402

R-US_R0402

R0402

R12

33 R-US_R0402

R0402

R13

33 R-US_R0402

R0402

R14

33 R-US_R0402

R0402

R15

33 R-US_R0402

R0402

R16

33 R-US_R0402

R0402

R17

33 R-US_R0402

R0402

R18

33 R-US_R0402

R0402

R19

33 R-US_R0402

R0402

R20

33 R-US_R0402

R0402

R21

33 R-US_R0402

R0402

R22

33 R-US_R0402

R0402

R8

R11

1k

R37

1K

R-US_R0402

R0402

R39

2K2

R-US_R0402

R0402

R40

1K

R-US_R0402

R0402

R41

2K2

R-US_R0402

R0402

LED

3M (TM) Pak 100

4-Wall Header

3M (TM) Pak 100

4-Wall Header

3M (TM) Pak 100

4-Wall Header

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

RESISTOR,

American symbol

31

R53

1K

R-US_R0402

R54

2K2

R-US_R0402

R55

1K

R-US_R0402

R56

2K2

R-US_R0402

R57

47K

R-US_R0402

R58

470 R-US_R0402

R59

470 R-US_R0402

R60

470 R-US_R0402

R61

470 R-US_R0402

U2

MSP430

U4

MSP430

X200

QSE-040-02

MSPEXP430F5529LP

MSPEXP430F5529LP

QSE-040-02

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

R0402

RESISTOR,

American symbol

MSP-EXP430F5529LP

MSP-EXP430F5529LP

QSE-040-02

0,80mm HISPEED SOCKET

QSE Serie

32

3.1.2 Circuito DCDC

Peça

Valor

5V_ON

Dispositivo

LEDCHIPLED_08

05

C-USC0603K

Ecapsulame

nto

CHIPLED_0

805

C0603K

C2

100nF

C3

1uF

C-USC0603K

C0603K

C4

100nF

C-USC0603K

C0603K

C5

100nF

C-USC0603K

C0603K

DCDC

10PIN

2510

IC1

317T

317T

PAK100/250

0-10

TO220H

IC2

317T

317T

TO220H

J4

ON/OFF

R1

12V

DCJ0303

CON_P CON_PWR_2P

WR

240

R-US_R0402

DCJ0303

PWR_CON

R0402

R2

360

R-US_R0402

R0402

R3

390

R-US_R0402

R0402

R4

360

R-US_R0402

R0402

R5

2K2

R-US_R0402

R0402

R6

360

R-US_R0402

R0402

R7

1.8k

R-US_R0402

R0402

R8

240

R-US_R0402

R0402

R9

1k

R-US_R0402

R0402

R10

1.8k

R-US_R0402

R0402

LEDCHIPLED_08

05

BC817-16-NPNSOT23-BEC

MODULE_ACS71

2

CHIPLED_0

805

SOT23-BEC

RIB_VC

C_ON

T1

U1

BC817

ACS71

2T

Descrição

LED

CAPACITOR,

American symbol

CAPACITOR,

American symbol

CAPACITOR,

American symbol

CAPACITOR,

American symbol

3M (TM) Pak 100 4Wall Header

Positive VOLTAGE

REGULATOR

Positive VOLTAGE

REGULATOR

DC POWER JACK

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

RESISTOR, American

symbol

LED

NPN Transistror

MODULE_A

CS712

33

3.1.3 Circuito RS485

Peça

C1

Valor

100nF

Dispositivo

CEUC0402K

CEUC0402K

CEUC0603K

CEUC0603K

CEUC0402K

-2510

Ecapsulamento

C0402K

C2

100nF

C3

1uF

C4

1uF

C5

100nF

DRIVERS

10 PIN

IC5

MAX3232C MAX3232CS SO16

SE

E

MODULE

RS485

OPT1

DB9

F09HP

F09HP

FODM121

SFH6186-2

SMD4

OPT2

FODM121

SFH6186-2

SMD4

C0402K

C0603K

C0603K

C0402K

PAK100/250010

R1

220 R-US_R0402

R0402

R2

220 R-US_R0402

R0402

RET_CABLE

RS232

RS232_RX/TX

RS485

UART_RX/TX

XALARM_CAB

LE

DB9

CON1

F15

F09HP

53047-03

JP2Q

JP2Q

JP2Q

F15HDH

F09HP

53047-03

JP2Q

JP2Q

JP2Q

HDF15H

Descrição

CAPACITOR,

European symbol

CAPACITOR,

European symbol

CAPACITOR,

European symbol

CAPACITOR,

European symbol

CAPACITOR,

European symbol

3M (TM) Pak

100 4-Wall

Header

True RS-232

Transceivers

3.0V to 5.5V,

Low-Power

SUB-D

Optocoupler,

Phototransistor

Output, Low

Input Current

Optocoupler,

Phototransistor

Output, Low

Input Current

RESISTOR,

American symbol

RESISTOR,

American symbol

SUB-D

CONNECTOR

JUMPER

JUMPER

JUMPER

SUB-D

34

3.2 Projeto Detalhado

Para que se elabore a metodologia de um processo de inspeção deve-se conhecer

antes de qualquer coisa, os padrões de qualidade do produto a ser testado. Para isso

estudou-se os parâmetros de uma placa não defeituosa – comumente chamada na empresa

de placa “Master” – para que sirvam de referência.

Outro ponto importante quando se projeta uma estação de teste é conhecer os

principais defeitos que podem resultar em um produto não conforme. Isto é importante

principalmente para que se tenham critérios de funcionamento da estação, ou seja, a Giga

de Teste deve ser capaz de “perceber” cada um dos defeitos, ainda que não seja capaz de

isolá-los, mas precisa garantir que a amostra, quando aprovada no teste, de fato não possui

nenhum defeito.

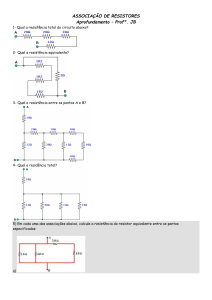

Tabela 1 Estudo dos principais defeitos possíveis na RIB

Causa

Componentes

com orientação /

polaridade

invertida

Efeito

Sintoma

Teste

O componente com orientação / polaridade invertida

irá se danificar e há pequena

possibilidade de danificar

outros componentes ligados

diretamente a ele.

Perda de sinal.

O bloco do circuito

onde o componente

estiver não funcionará corretamente. O

sinal “morre” nele.

Medição dos sinais de

entrada e saída do

componente, em seguida

verificação visual da

serigrafia do componente.

Sinais ligados aos

terminais do componente faltando apresentarão variação nos

níveis de tensão ou

serão nulos.

O bloco do circuito

onde o componente

estiver não funcionará corretamente e

pode haver curtocircuito.

Apenas realizar inspeção

visual.

Aparecimento

de

ruídos no circuito

envolvido.

Identificar a região do

circuito que apresenta

falha através do multímetro e em seguida com

auxilio

de

um

microscópico realizar uma

inspeção

visual

até

identificar o problema na

solda.

Comparar os sinais de

entrada e saída do

componente e comparar os

valores com valores de

uma placa de referência

(placa Master).

Componentes

Faltando

Ponte de Solda

(“Solde bridge”)

Outros

problemas

relacionados à

solda (Solda fria,

insuficiência, etc)

Falha funcional

do componente

Em terminais de sinais

digitais, poderá danificar o

próprio componente com a

ponte de solda e em caso de

ponte de solda entre VCC e

GND a placa entrará em

curto-circuito, danificando

o circuito da fonte.

O circuito pode apresentar

“mau-contato” e intermitência.

O circuito relacionado ao

componente

defeituoso

apresentará mau funcionamento ou não funcionará.

Sinais de entrada no

componente estarão

funcionando perfeitamente, porém não

haverá sinal de saída.

Identificar o circuito com

falha com um ohmímetro e

realizar a inspeção visual

com um microscópio.

35

Nesse sentido, estudaram-se as causas e efeitos dos diversos defeitos em lotes não

liberados na empresa Ericsson pôde-se listar em síntese todos os defeitos possíveis na

RIB. Para que seja possível detectar certo defeito deve-se conhecer não somente as causas

e efeitos, mas também seus sintomas, ou seja, os principais indícios de que este defeito

está presente. Analisando vários casos de lotes defeituosos, pôde-se elencar os principais

sintomas de defeitos e então ficou mais fácil de estabelecer quais os tipos de testes que a

Giga de Teste deveria ser capaz de realizar para garantir a qualidade da RIB. Todas essas

informações foram sintetizadas na Tabela 1.

Excetuando-se a verificação de componentes com o microscópio e a inspeção

visual, os testes que a Giga de Teste deve realizar são simples: medição de corrente, teste

de continuidade e queda de tensão.

Os dois microcontroladores estarão conectados aos quatro circuitos de teste da

Giga, como mostra a Figura 11. O circuito RS 485 é representado junto ao de padrão

Ethernet por utilizar o mesmo multiplexador. No entanto, como já foi mencionado, os

objetos de estudo deste trabalho serão somente os testes do circuitos DCDC e RS485.

MSP430_A

UART

MSP430_B

UART

UART

DCDC

RS 485/Ethernet

Óptico

Painel LEDs

Figura 11 – Bloco Principal

Ao ligar a fonte de alimentação, a tensão é regulada em 5V pelo LM 317 para

energizar a Giga de Teste (seus microcontroladores). E ao ser pressionado o botão

START do microcontrolador, ele envia um sinal para um segundo LM317, que fecha o

circuito e alimenta a RIB que será testada, conforme a Figura 12. Os LM317 possuem

proteção contra sobrecorrente que abrem o circuito se a corrente extrapolar um limite,

assegurando que a RIB conectada à Giga de Teste não receba a corrente de curto.

36

Fontes 12-24V

ON/OFF

LM 317

LM 317

5V

5V

MSP

Medição de

corrente

Estação RIB

CI – Hall

ACS 712 T

RIB

Figura 12 – Bloco DCDC

O MSP realiza uma medição da corrente que sai do LM317 e vai para a RIB a fim

de comparar com o valor da placa Master e detectar já nesse processo inicial se há algum

mau funcionamento na amostra e se esse for o caso, encerra o teste e acende o LED

“FAIL”.

A medição de corrente é feita por um circuito contendo o CI Hall ACS 712

mostrado na Figura 13, que oferece soluções para sensores de corrente AC e DC nas mais

diversas aplicações, como controle de motores, fontes de alimentação e proteção contra

sobrecorrente. O dispositivo consiste de um circuito Hall preciso e linear que possui

internamente uma trilha de cobre (dos pinos 1 e 2, para os pinos 3 e 4) com baixa

resistência interna (1.2 mΩ nominal, para que a haja baixa perda de potência). Quando é

aplicado fluxo de corrente através dessa trilha de cobre cria-se um campo magnético que

o transdutor do CI Hall converte numa tensão de nível proporcional.

Os terminais da trilha condutiva são isolados das outras entradas/saídas de sinal

(pinos 5 a 8), o que permite que o ACS712 seja utilizado em aplicações que requerem

37

isolação elétrica sem elevar muito o custo do projeto. A tensão gerada na saída do CI Hall

(VIOUT) é enviada ao pino de entrada analógica do MSP_A P6.5 para ser processado.

Figura 13 – Pinagem do CI Hall ACS 712

MSP430_A

UART

UART_A

Multiplex

4052

UART_B

Placa RIB

Módulo

Ethernet / RS232

Módulo RS

232/485

Placa RIB

MAX 232

Backloop

MSP430_B

UART

Figura 14 - Bloco RS485 / Ethernet

Na sequência, inicia-se o teste do circuito RS485, que foi esquematizado na Figura

14. Devido a grande quantidade de pinos a serem testados, foi utilizado um componente

multiplexador que comuta a conexão de um pino entre vários caminhos, servindo como

uma extensão do microcontrolador. No processo do teste, o MSP_A enviará um dado para

o MSP_B através do multiplexador que estará conectado à RIB, ou seja, o dado irá passar

38

pelo circuito RS485 da RIB até chegar ao segundo microcontrolador. O MSP_B então

envia uma resposta ao MSP_A pelo mesmo canal RS485.

Para que o código ficasse mais leve e simples, adotou-se um módulo conversor

de forma que a RIB trabalhe com RS485 e os microcontroladores, RS232. Depois de os

receberem, os microcontroladores analisarão os dados e, se verificarem sua integridade,

o teste passa para as próximas etapas.

39

3.3 Programação

O programa inicia em um “loop” de Decisão, no qual aguarda o BOTAO_START

ficar em nível alto, que acontece quando o operador deseja iniciar o teste da RIB e aciona

o BOTAO_START;

Após acionado o BOTAO_START, é feito a leitura da corrente consumida pela

RIB através de uma porta analógica (I_SUPERV) do MSP_A, e se a corrente for menor

que 90d ou maior que 120d o teste é finalizado cortando a alimentação da RIB e

acionando o LED_FAIL(vermelho), e caso a corrente estiver entre 90d a 120d o teste

continua para próxima etapa;

Na etapa seguinte é testada a comunicação serial RS-485, na qual o MSP_A

configura o multiplexador para direcionar a saída serial do MSP_A para o módulo

conversor RS-232/RS485, através do “set” em A e B para zero; em seguida o MSP_A

envia o caracter “a” e aguarda uma resposta de um caracter “b” do MSP_B, nessa etapa

o MSP_B fica aguardando um caracter “a” via serial e em seguida envia um caracter “b”.

Ao receber o caracter “b”, o MSP_A finaliza o teste da RIB cortando a alimentação da

RIB e acionando o LED_PASS (verde), caso não recebe o caracter “b”, o teste é finalizado

indicando falha.

40

3.4 Fluxograma

MSP430_A

INÍCIO

MSP430_B

BOTÃO_START =

1

DELAY_MS = 1000

LER I_SUPERV

90 <

I_SUPERV

< 120

CALL FAIL

A = 0; B = 0

UART_A_TX = “a”

41

C=1; C<500; C++

INTERRUPÇÃO UART_B

CALL FAIL

UART_A_RX

== “b”

UART_B_RX

== “a”

CALL FAIL

RIB_ON/OFF = 0

RIB_ON/OFF = 0

LED_PASS = 1

UART_B_TX = “b”

LED_FAIL = 1

FIM

FIM

FIM

42

Capítulo 4

Resultados

4.1 Circuito Teste DCDC

4.1.1 Teste funcional

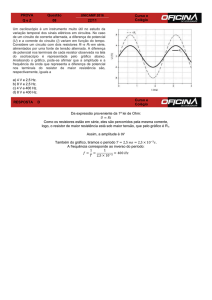

No planejamento das medições, consideramos uma faixa de corrente aceitável

(110 ±10 mA) para o funcionamento de uma RIB e foi implantado juntamente ao circuito

de teste DCDC, um limitador de corrente, para que não ocorresse nenhum dano a placa

ou a estação de testes. Foram disponibilizadas para a realização deste teste 10 RIBs e

apenas duas falharam. Os testes foram realizados em 5 minutos (em média 30 segundos

para cada placa), tempo melhor do que havíamos previsto.

4.1.2 Teste de Confiabilidade

As mesmas 10 RIBs testadas na estação, passaram pelo teste de bancada (teste

realizado por técnicos que a analisam quando realmente é necessário o reparo dessas

placas) e foram confirmados todos os resultados retornados pela estação. As duas placas

que não passaram no teste da estação, realmente estavam com problemas ocorridos no

processo produtivo, como mostra a Tabela 2.

Tabela 2 – Resultados dos testes no circuito DCDC

Após realizados os testes, todas as RIBs com problema na região de DCDC

Valor Medido em

Bancada (mA)

Resultado do teste

(DCDC)

Resultado Teste

(RIB)

110

110

110

200

110

Pass

Pass

Pass

Failed

Pass

Pass

Pass

Pass

Failed

Pass

50

Failed

Failed

110

Pass

Pass

100

Pass

Failed

110

110

Pass

Pass

Pass

Pass

Observação

Técnica

Curto por solda

Faltando

Componente

Falha em outra região,

DCDC ok

foram reparadas para serem utilizadas no próximo teste.

43

4.2 Teste RS-485

4.2.1 Teste Funcional

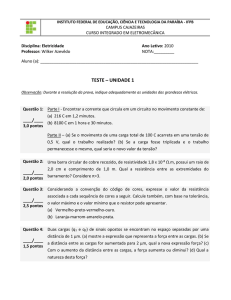

Conforme planejado, o teste RS-485 foi realizado enviando um dado via RS-232

convertido à RS485 e injetado a RIB e lido de forma inversa através de outro conector da

própria RIB. Foram utilizadas as mesmas 10 RIBs disponibilizadas para o teste e

nenhuma falhou.

4.2.2 Teste de confiabilidade

Como não é possível realizar este teste em bancada, fizemos o seguinte teste: Não

conectamos totalmente o cabo na RIB, simulando algum problema de solda fria ou até

mesmo falta de solda ou ainda a falta de um componente causando problema na

comunicação ou no recebimento do dado enviado. Como previsto em todos os casos a

estação as reprovou.

Tabela 3 – Resultados dos testes no circuito RS-485

Resultado Teste

RS-485

Pass

Resultado do

teste (RIB)

Pass

Resultado Teste

(RRU)

Pass

Pass

Pass

Failed

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Pass

Observação Técnica

Componente deslocado na PAU (Power

Amplifier Unit)

Para confirmar o teste, levamos as 10 RIBs para serem testadas no nível de rádio

(RRU) e apenas uma RRU foi reprovada. Os técnicos analisaram e RRU reprovada e

constataram um defeito de processo produtivo em outro componente da RRU que não a

RIB, como demonstra a Tabela 3.

44

4.3 Placas Confeccionadas

As Figuras 15 e 16 mostram a placa de circuito impresso da parte DCDC da Giga

de Teste, onde possui um sistema de proteção de curto circuito, regulador de tensão

configurado para 5V e um módulo medidor de corrente por efeito “hall”.

Figura 15 - PCB Circuito DCDC (TOP)

Figura 16 - PCB Circuito DCDC (BOT)

As Figuras 17 e 18 mostram a placa de circuito impresso responsável pela

comunicação RS485.

45

Figura 17 - PCB Circuito RS485/Ethernet (TOP)

Figura 18 - PCB Circuito RS485/Ethernet (BOT)

Conforme a Figura 19, todas placas de circuito impresso foram conectadas à placa

de controle onde estão localizados os dois kits MSP430F5520LP.

46

Figura 19 – Circuito Estação RIB parcialmente completo utilizado para testes

47

Capítulo 5

Conclusões

Com este projeto os autores puderam estudar o funcionamento da RIB e trabalhar

no projeto da estação de teste (Giga de Teste), que chegou a ser testada na linha de

produção da empresa Ericsson. O dispositivo fabricado mostrou-se como uma inovação

de baixo custo capaz de simular e testar as funções dos circuitos DCDC e RS485 da RIB.

Com a Giga de Teste melhorou-se a metodologia de inspeção no processo de

fabricação da RIB, e possibilitou-se que o usuário obtivesse o resultado do teste de

maneira simples, rápida e de baixo custo.

Este projeto conseguiu também ampliar a visão dos envolvidos sobre o processo

de inspeção da RIB, deixando oportunidades de melhoria para implementação futura das

quais se destacam:

Estudar o circuito Óptico da RIB e criar uma metodologia para testá-lo na

Giga de Teste;

Estudar o circuito com padrão Ethernet e aprimorar este dispositivo para

testá-lo também;

Criar uma interface no computador ou tela de LCD para melhorar a

apresentação dos resultados.

48

Referências Bibliográficas

[1] - C. E. STRANGIO. The RS232 STANDARD, A Tutorial with Signal Names and

Definitions. CAMI Research Inc., Acton, Massachusetts (1993-2012) Disponível em:

http://www.camiresearch.com/Data_Com_Basics/RS232_standard.html Acesso em: 27

jul. 2014.

[2] - CISCO. Cisco Visual Networking Index: Global Mobile Data Traffic Forecast

Update, 2013–2018 Disponível em:

http://www.cisco.com/c/en/us/solutions/collateral/service-provider/visual-networkingindex-vni/white_paper_c11-520862.html Acesso em: 27 set. 2014.

[3] - CNET. Ericsson predicts tenfold increase in mobile data traffic in five years.

Disponível em: http://www.cnet.com/news/ericsson-predicts-tenfold-increase-inmobile-data-traffic-in-five-years/ Acesso em: 28 set. 2014.

[4] - E-THESIS. Small cells: você ainda vai ter a sua... Disponível em:

http://www.e-thesis.inf.br/index.php?option=com_content&task=view&id=7912&Itemi

d=52 Acesso em: 4 out. 2014.

[5] - SINDITELEBRASIL, SINDICATO NACIONAL DAS EMPRESAS DE

TELEFONIA E DE SERVIÇO MÓVEL CELULAR E PESSOAL. Copa 2014: mais de

1 milhão de comunicação de dados no jogo do Brasil x Croácia. Disponível em:

http://www.sinditelebrasil.org.br/sala-de-imprensa/na-midia/2210-copa-2014-mais-de1-milhao-de-comunicacao-de-dados-no-jogo-do-brasil-x-croacia Acesso em: 5 out.

2014.

[6] - TELECO. Redes WiMAX: Regras para o Dimensionamento Disponível em:

http://www.teleco.com.br/tutoriais/tutorialredeswimax/pagina_4.asp Acesso em: 27 set.

2014.

[7] - UFRGS. O Efeito Hall. Disponível em:

www.if.ufrgs.br/tex/fis142/mod08/m_s03.html Acesso em: 26 jul. 2014.

[8] - V. A. SOUZA. Comunicação RS232 e RS485 (2010). Disponível em:

http://www.ebah.com.br/content/ABAAAAMYcAI/protocolos-rs232-rs485 Acesso em:

20 jul. 2014.

[9] - WEG. Manual da Comunicação Serial RS232 / RS485, Série: CFW-11, Número

do Documento: 0899.5740 / 03 (2010). Disponível em:

http://ecatalog.weg.net/files/wegnet/WEG-cfw-11-manual-da-comunicacao-serialrs232-rs485-0899.5740-manual-portugues-br.pdf Acesso em: 19 jul. 2014.

49

Anexo 1 – Esquema Elétrico

50

51

52

53

54

55

Anexo 2 – Código “Main”

MSP_A

#include <msp430f5529.h>

volatile unsigned int results[10];

// Needs to be global in this example

// Otherwise, the compiler removes it

// because it is not used for

anything.

unsigned int c;

int Analog;

int RS485_check = 0;

void Pass(void)

{

unsigned int a;

P2OUT |=

P1OUT |=

P6OUT &=

for(a=0;

BIT7;

BIT6;

~BIT6;

a<10000; a++);

while (!(UCA1IFG&UCTXIFG));

UCA1TXBUF = 'p';

//

//

//

//

DESLIGA VCC_RIB

SET UART MSPA=MSPB

SET UART MSPA=MSPB

delay

// USCI_A0 TX buffer ready?

// TX -> RXed character

}

void Fail(void)

{

unsigned int b;

P2OUT |=

P1OUT |=

P6OUT &=

for(b=0;

BIT7;

BIT6;

~BIT6;

b<10000; b++);

while (!(UCA1IFG&UCTXIFG));

UCA1TXBUF = 'f';

//DESLIGA VCC_RIB

// SET UART MSPA=MSPB

// SET UART MSPA=MSPB

// delay

// USCI_A0 TX buffer ready?

// TX -> RXed character

}

int main(void)

{

WDTCTL = WDTPW+WDTHOLD;

// Stop watchdog timer

//Configuração portas

P2DIR |= BIT7;

P2OUT |= BIT7;

// RIB_ON/OFF

// DESLIGA

P3DIR &= ~BIT1;

P3REN |= BIT1;

P3OUT |= BIT1;

// START_BUTTON

// ATIVA PULL UP/DOWN

// SET PULLUP

P6DIR &= ~BIT5;

// I_SUPERV (ANALOGICO)

P1DIR |= BIT6;

P6DIR |= BIT6;

// UART SELECT = A

// UART SELECT = B

56

//Configuração UART

P3SEL = BIT3+BIT4;

// P3.4,5 = USCI_A0 TXD/RXD

UCA0CTL1 |= UCSWRST;

// **Put state machine in reset**

UCA0CTL1 |= UCSSEL_2;

// SMCLK

UCA0BR0 = 6;

// 1MHz 9600 (see User's Guide)

UCA0BR1 = 0;

// 1MHz 9600

UCA0MCTL = UCBRS_0 + UCBRF_13 + UCOS16;

// Modln UCBRSx=0, UCBRFx=0,

UCA0CTL1 &= ~UCSWRST;

// **Initialize USCI state machine**

UCA0IE |= UCRXIE;

// Enable USCI_A0 RX interrupt

__bis_SR_register(GIE);

// interrupts enabled

//Configuração ADC

P6SEL = 0x0F;

// Enable A/D channel inputs

ADC12CTL0 = ADC12ON+ADC12MSC+ADC12SHT0_2; // Turn on ADC12, set sampling

time

ADC12CTL1 = ADC12SHP+ADC12CONSEQ_1; // Use sampling timer, single sequence

ADC12MCTL0 = ADC12INCH_0;

// ref+=AVcc, channel = A0

ADC12MCTL1 = ADC12INCH_1;

// ref+=AVcc, channel = A1

ADC12MCTL2 = ADC12INCH_2;

// ref+=AVcc, channel = A2

ADC12MCTL3 = ADC12INCH_3+ADC12EOS;

// ref+=AVcc, channel = A3, end seq.

ADC12MCTL5 = ADC12INCH_5;

// ref+=AVcc, channel = A5

ADC12IE = 0x08;

ADC12CTL0 |= ADC12ENC;

// Enable ADC12IFG.3

// Enable conversions

while(1)

{

nok:

while((P3IN & BIT1)==0);// Aguarda o operador acionar o botão START

for(c=0; c<15000; c++);

// Delay

P2OUT &= ~BIT7;

// Acionada a alimentação da RIB

for (c=1; c<4000; c++);

// Delay para a RIB estabilizar

// Leitura da corrente

ADC12CTL0 |= ADC12SC;

// Start convn - software trigger

Analog = ADC12MEM5;

// Leitura analogica do I_Superv

if ((90 < Analog) && (Analog < 150)) // Limites de corrente de uma

placa ok

goto ok;

// se ok continua para proxima etapa

else

{

Fail();

goto nok;

// senão termina o teste

}

ok:

for(c=1; c<10000; c++);

//Inicio do teste RS485

P1OUT &= ~BIT6;

P6OUT &= ~BIT6;

// delay

// SET UART RS485

// MSP_A = UART_A / MSP_B = UART_D

for(c=1; c<10000; c++);

// delay

while (!(UCA1IFG&UCTXIFG));

UCA1TXBUF = 'a';

for(c=1; c<20000; c++)

// USCI_A0 TX buffer ready?

// TX -> RXed character

57

{

if(RS485_check == 1) goto ok1;

}

Fail();

// RS485 ok!

ok1:

Pass();

}

}

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=ADC12_VECTOR

__interrupt void ADC12ISR (void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(ADC12_VECTOR))) ADC12ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(ADC12IV,34))

{

case 0: break;

// Vector 0: No interrupt

case 2: break;

// Vector 2: ADC overflow

case 4: break;

// Vector 4: ADC timing

overflow

case 6: break;

// Vector 6: ADC12IFG0

case 8: break;

// Vector 8: ADC12IFG1

case 10: break;

// Vector 10: ADC12IFG2

case 12:

// Vector 12: ADC12IFG3

results[0] = ADC12MEM0;

// Move results, IFG is cleared

results[1] = ADC12MEM1;

// Move results, IFG is cleared

results[2] = ADC12MEM2;

// Move results, IFG is cleared

results[3] = ADC12MEM3;

// Move results, IFG is cleared

results[5] = ADC12MEM5;

__bic_SR_register_on_exit(LPM4_bits);

// Exit active CPU, SET

BREAKPOINT HERE

case 14: break;

// Vector 14: ADC12IFG4

case 16: break;

// Vector 16: ADC12IFG5

case 18: break;

// Vector 18: ADC12IFG6

case 20: break;

// Vector 20: ADC12IFG7

case 22: break;

// Vector 22: ADC12IFG8

case 24: break;

// Vector 24: ADC12IFG9

case 26: break;

// Vector 26: ADC12IFG10

case 28: break;

// Vector 28: ADC12IFG11

case 30: break;

// Vector 30: ADC12IFG12

case 32: break;

// Vector 32: ADC12IFG13

case 34: break;

// Vector 34: ADC12IFG14

default: break;

}

}

// Echo back RXed character, confirm TX buffer is ready first

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=USCI_A0_VECTOR

__interrupt void USCI_A0_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_A0_VECTOR))) USCI_A0_ISR (void)

#else

#error Compiler not supported!

58

#endif

{

switch(__even_in_range(UCA0IV,4))

{

case 0:break;

case 2:

if(UCA1RXBUF == 'b')

{

RS485_check = 1;

}

break;

case 4:break;

default: break;

}

}

// Vector 0 - no interrupt

// Vector 2 - RXIFG

// Vector 4 - TXIFG

59

MSP_B

#include <msp430f5529.h>

int main(void)

{

WDTCTL = WDTPW+WDTHOLD;

// Stop watchdog timer

//Configuração portas

P1DIR |= BIT4;

P1OUT &= ~BIT4;

// LED_PASS

// APAGA

P1DIR |= BIT5;

P1OUT &= ~BIT5;

// LED_FAIL

// APAGA

//Configuração UART

P3SEL = BIT3+BIT4;

// P3.4,5 = USCI_A0 TXD/RXD

UCA0CTL1 |= UCSWRST;

// **Put state machine in reset**

UCA0CTL1 |= UCSSEL_2;

// SMCLK

UCA0BR0 = 6;

// 1MHz 9600 (see User's Guide)

UCA0BR1 = 0;

// 1MHz 9600

UCA0MCTL = UCBRS_0 + UCBRF_13 + UCOS16;

// Modln UCBRSx=0, UCBRFx=0,

UCA0CTL1 &= ~UCSWRST;

// **Initialize USCI state machine**

UCA0IE |= UCRXIE;

// Enable USCI_A0 RX interrupt

__bis_SR_register(GIE);

// interrupts enabled

while(1);

}

// Echo back RXed character, confirm TX buffer is ready first

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=USCI_A0_VECTOR

__interrupt void USCI_A0_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_A0_VECTOR))) USCI_A0_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(UCA0IV,4))

{

case 0:break;

// Vector 0 - no interrupt

case 2:

// Vector 2 - RXIFG

if(UCA1RXBUF == 'a')

// RS485 TEST

{

while (!(UCA1IFG&UCTXIFG));

// USCI_A0 TX buffer ready?

UCA1TXBUF = 'b';

}

if(UCA1RXBUF == 'p') P1OUT |= BIT4;

// LED_PASS ON

if(UCA1RXBUF == 'f')

P1OUT |= BIT5;

// FAIL_PASS ON

60

break;

case 4:break;

default: break;

}

// Vector 4 - TXIFG

}

61