Ministério da Educação

Universidade Tecnológica Federal do Paraná

Departamento Acadêmico de Eletrônica

Curso Técnico em Eletrônica

Disciplina: Microcontroladores 1

PR

UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ

Microcontrolador Hipotético

Estudo e Simulação

Material de Apoio

Cion Cassiano Basso

Curitiba, 02 de março de 2011

Estudo do Microcontrolador Hipotético

Página 1

Lista de Figuras

Figura 1 – Diagrama em blocos do computador digital. ............................................................................................. 5

Figura 2 – Diagrama em blocos do computador digital com o detalhamento da CPU. ................................... 6

Figura 3 – Microprocessador é uma CPU encapsulada em um CI. .......................................................................... 6

Figura 4 – Diagrama em blocos do microcomputador................................................................................................. 7

Figura 5 – Microcontrolador é um microcomputador encapsulado em um CI. ................................................. 8

Figura 6 – Exemplos de aplicação para o microcontrolador. .................................................................................... 9

Figura 7 – Modelo do programador para o microcontrolador hipotético..........................................................11

Figura 8 – Diagrama funcional do microcontrolador hipotético. ..........................................................................11

Figura 9 – Detalhamento do hardware do microcontrolador hipotético. ..........................................................13

Figura 10 – Componentes necessários para se implementar um bit do Bus de dados. ................................14

Figura 11 – O circuito de Clock sincroniza a transferência de dados entre os componentes da CPU.....15

Figura 12 – (a) Diagrama em blocos do registrador de um bit. (b) Implementação do registrador. ......15

Figura 13 – (a) Circuito do registrador de oito bits. (b) Representação sob a forma de bloco..................16

Figura 14 – Implementação do registrador A, com o flag Zero (ZA)....................................................................17

Figura 15 – Representação e implementação da porta P0.......................................................................................18

Figura 16 – Estrutura da Unidade Lógica e Aritmética (ULA). ...............................................................................20

Figura 17 – Diagrama da memória RAM e componentes associados. .................................................................20

Figura 18 – Estrutura da memória de programa (ROM). .........................................................................................21

Figura 19 – (a) Diagrama dos registradores PC e MROM. (b) Composição do registrador PC. .................22

Figura 20 – Ciclos de busca, decodificação e execução do programa (Firmware). .........................................23

Figura 21 – Estrutura da Unidade de Controle. ............................................................................................................24

Figura 22 – Implementação da Unidade de Controle pela técnica de Lógica de Controle Fixo. ................25

Figura 23 – Formas de ondas geradas pelo Contador em Anel. .............................................................................26

Figura 24 – Diagrama de temporização para o ciclo de busca do opcode. .........................................................27

Figura 25 - Implementação do circuito para o sinal LPC. .........................................................................................30

Figura 26 – Níveis de linguagens de programação. ....................................................................................................43

Figura 27 – Estrutura do programa Simulador. ...........................................................................................................44

Figura 28 – Tela de entrada do programa Simulador. ...............................................................................................45

Figura 29 – Tela de entrada do módulo do Editor do Firmware na ROM...........................................................46

Figura 30 – Apresentação do conteúdo da memória ROM, após a edição. ........................................................47

Figura 31 – Tela de entrada do módulo: Gravador do Firmware em Arquivo..................................................48

Figura 32 – Conteúdo gravado com o módulo Gravador do Firmware no arquivo C:/C1.TXT. .................48

Figura 33 – Tela para a opção de carregamento do Firmware. ..............................................................................49

Figura 34 – Firmware carregado na memória ROM....................................................................................................49

Figura 35 – Mensagem de ERRO apresentada na ocorrência de falha na leitura do arquivo.....................49

Figura 36 – Tela apresentada no módulo Desmontador do Firmware................................................................50

Figura 37 – Mensagem de erro devido a um opcode inválido.................................................................................50

Figura 38 – Tela gerada pelo módulo do Simulador do Firmware após a execução das instruções........51

Figura 39 – Apresentação do conteúdo da RAM após operação com a memória. ..........................................52

Figura 40 – Tela de entrada do Simulador das Microinstruções. ..........................................................................53

Figura 41 – Simulação da instrução MOV 01,A (p/A=22). .......................................................................................53

Figura 42 – Conteúdo da memória RAM após instrução MOV 01,A (p/A=22).................................................54

Estudo do Microcontrolador Hipotético

Página 2

SUMÁRIO

APRESENTAÇÃO...................................................................................................................................................4

I. CONCEITOS BÁSICOS...................................................................................................................................5

I.1. Computador Digital ....................................................................................................................................................... 5

I.2. Microcomputador e Microprocessador ................................................................................................................. 6

I.3. Microcontrolador ........................................................................................................................................................... 8

II. MICROCONTROLADOR HIPOTÉTICO................................................................................................... 10

II.1. Modelo do Programador..........................................................................................................................................10

II.2. Operação do Microcontrolador .............................................................................................................................11

II.3. Hardware do microcontrolador hipotético ......................................................................................................13

II.4. Descrição do Hardware ............................................................................................................................................14

II.5. Conjunto de Instruções.............................................................................................................................................30

II.6. Descrição das Instruções .........................................................................................................................................32

III. PROGRAMAÇÃO EM LINGUAGEM DE MÁQUINA ............................................................................... 42

III.1. Linguagem de Programação .................................................................................................................................42

III.2. Programa Simulador................................................................................................................................................44

III.3. Operação do Simulador ..........................................................................................................................................45

III.3.1. Módulo: Editor do Firmware na ROM .......................................................................................................45

III.3.2. Módulo: Gravador do Firmware em Arquivo .........................................................................................47

III.3.3. Módulo: Carregador do Firmware de Arquivo.......................................................................................48

III.3.4. Módulo: Desmontador do Firmware .........................................................................................................50

III.3.5. Modulo: Simulador do Firmware ................................................................................................................51

III.3.6. Módulo: Simulador das Microinstruções.................................................................................................52

Estudo do Microcontrolador Hipotético

Página 3

APRESENTAÇÃO

O objetivo deste material é iniciar o estudo microcontrolador 8051, conteúdo da disciplina

Microcontroladores 1, desenvolvida no 7º período do Curso Técnico em Eletrônica, ministrado no

Campus Curitiba da Universidade Tecnológica Federal do Paraná (UTFPR). A motivação para a sua

elaboração decorre da percepção de que o domínio do tema microcontrolador é facilitado quando o

estudante tem o conhecimento dos conceitos gerais envolvidos com computadores digitais,

principalmente quanto às terminologias, os blocos funcionais, os componentes de hardware, o

princípio de funcionamento e a noção de programação básica (software).

Os dois conhecimentos necessários que o estudante deve possuir para o melhor aprendizado,

compreendem: (i) programação em linguagem de alto nível, como C, Pascal ou outra; e (ii) Eletrônica

Digital, envolvendo o domínio das funções lógicas, circuitos combinacionais (multiplexadores,

demultiplexadores, codificadores, decodificadores, comparadores etc), circuitos sequenciais (flipflops, contadores e registradores) e memórias semicondutoras.

Assim, este estudo será desenvolvido em quatro etapas, abrangendo:

I.

o desenvolvimento dos conceitos básicos relacionados aos computadores digitais,

microcomputadores, microprocessadores e microcontroladores;

II. o estudo de uma arquitetura simplificada de um microcontrolador hipotético;

III. a elaboração e simulação de programas em linguagem de máquina para a arquitetura

simplificada com o emprego de um programa Simulador; e

IV. a programação em Linguagem de Montagem (Assembly), empregando um programa

Montador (Assembler), em conjunto com o Simulador.

Após concluir o aprendizado destes conteúdos, o estudante estará apto a compreender como

os computadores são estruturados, quais são seus principais componentes de hardware, como eles se

conectam e como são controlados a partir de um programa codificado em linguagem de máquina

armazenado na memória.

Também, o conhecimento básico de programação em linguagem de máquina exercitado

facilitará o aprendizado do microcontrolador 8051, ou outros dispositivos, possibilitando a

compreensão das etapas necessárias ao desenvolvimento de software de controle (Firmware).

Como este material está em contínuo processo de correção e construção, as sugestões, as

dúvidas geradas e as propostas de melhorias são bem vindas e podem ser encaminhadas para e-mail:

[email protected].

Estudo do Microcontrolador Hipotético

Página 4

I. CONCEITOS BÁSICOS

I.1. Computador Digital

Um computador digital, genericamente, é um equipamento eletrônico que aceita, armazena,

modifica e disponibiliza informações representadas no sistema de numeração binário, sendo

comumente estruturado a partir de três unidades denominadas de: (i) Unidade Central de

Processamento (UCP ou CPU - Central Processing Unit); (ii) Unidade de Memória; e (iii) Unidade de

Entrada/Saída.

A troca de informações entre estas três Unidades ocorre por intermédio de um sistema de

comunicação designado de Bus (em português, alguns autores empregam os termos: barramento, via

ou duto).

A interação do computador com o meio externo é realizada por diferentes dispositivos de

comunicação, denominados de Periféricos de Entrada/Saída. Os dispositivos de armazenamento de

dados de alta capacidade, conhecidos como memória secundária, também são conectados ao

computador por meio da Unidade de Entrada/Saída. Esses componentes estão representados sob

forma diagrama em blocos ilustrado na figura 1.

Figura 1 – Diagrama em blocos do computador digital.

Funcionalmente, a CPU é responsável pela execução de programas armazenados na Unidade de

Memória (também designada de memória principal) e que são desenvolvidos para uma determinada

aplicação, chamados de softwares aplicativos, tais como editores, navegadores, planilhas, jogos etc, ou

para controle das suas unidades internas, conhecidos como softwares de suporte, que é o caso, por

exemplo, do Sistema Operacional.

Um programa consiste de um conjunto de instruções organizadas de forma a solucionar um

problema computacional, sendo cada instrução uma ordem para que a CPU produza um determinado

resultado. Os dados temporários manipulados pelo programa são armazenados na memória principal.

A CPU, de maneira conceitual, é implementada a partir de três unidades funcionais

denominadas de: (i) Unidade Lógica e Aritmética (ULA ou ALU - Arithmetic Logic Unit); (ii) Unidade de

Controle (UC); e (iii) Unidade de Registradores (UR). Essas unidades trocam informações por um

sistema de Bus.

O diagrama em blocos da figura 2 apresenta a composição do computador digital, com as três

Unidades que implementam a CPU (ULA + UR + UC).

Estudo do Microcontrolador Hipotético

Página 5

Figura 2 – Diagrama em blocos do computador digital com o detalhamento da CPU.

A ULA é responsável pela realização de operações lógicas (E, OU, NÃO, OU exclusivo, entre

outras) e aritméticas (soma, subtração, entre outras), de acordo com a instrução que a CPU irá

executar.

A UC é responsável pela geração de todos os sinais elétricos de controle que comandam as

demais unidades internas à CPU (ULA e UR) e externas (Memória e Entrada/Saída). Estes sinais são

ativados de acordo com a execução de cada instrução.

A UR é constituída por um conjunto de registradores responsáveis pelo armazenamento de

dados e informações de controle necessárias à execução das instruções.

I.2. Microcomputador e Microprocessador

Um microcomputador é um computador digital no qual a CPU é um Circuito Integrado (CI),

denominado de microprocessador (μP)1, conforme ilustrado na figura 3.

Figura 3 – Microprocessador é uma CPU encapsulada em um CI.

1

O desenvolvimento da microeletrônica tem possibilitado a integração de dois ou mais núcleos de processadores

(arquiteturas multicores) em único CI, como estratégia de melhoria no desempenho dos computadores digitais,

Estudo do Microcontrolador Hipotético

Página 6

Adicionalmente ao μP, um microcomputador necessita de outros componentes, conforme

ilustrado no diagrama em blocos da figura 4.

Figura 4 – Diagrama em blocos do microcomputador.

•

•

•

•

•

•

Os componentes que integram o microcomputador, compreendem:

memórias semicondutoras que podem ser classificadas em dois tipos genéricos: (i) RAM

(Random Access Memory – Memória de Acesso Aleatório), capaz de realizar operações de

escrita e leitura e que são empregadas para o armazenamento temporário de dados (e/ou

programas); e (ii) ROM (Read Only Memory – Memória de Somente Leitura), capaz de efetuar

somente a operação de leitura, sendo empregada para armazenar programas e/ou dados

permanentes;

Interfaces de E/S empregados para compatibilizar os diferentes periféricos de E/S ao sistema

de Buses do μP;

um sistema de comunicação com três Buses, designados de Bus de Dados, Bus de Endereços e

Bus de Controle;

Periféricos de E/S para comunicação com o usuário e/ou armazenamento de dados em grande

quantidade e de forma não volátil2;

circuito de Clock para determinar a velocidade de execução das instruções e,

consequentemente, a velocidade na execução de programas; e

circuito de Reset empregado para inicializar o microcomputador ao ser energizado ou reiniciálo manualmente, no caso de travamento do programa ou reinício de operação.

2

Um sistema de armazenamento não volátil retém informações sem necessitar de fonte de energia como, por exemplo,

HDs, pen drivers, sistemas de back-up, entre outros.

Estudo do Microcontrolador Hipotético

Página 7

I.3. Microcontrolador

Um microcontrolador é um microcomputador encapsulado em um CI que pode conter, além

da CPU, memórias RAM e/ou ROM, Interfaces de E/S, circuitos de Clock e Reset, entre outros,

conforme ilustrado na figura 5.

Figura 5 – Microcontrolador é um microcomputador encapsulado em um CI.

Os fabricantes integram em seus microcontroladores diferentes componentes buscando

minimizar a conexão de circuitos externos e, com isso, facilitar o desenvolvimento de aplicações.

Assim, um microcontrolador pode ser comercializado com diferentes configurações, de acordo com os

componentes incorporados, que podem incluir: conversor A/D (analógico/digital), conversor D/A

(digital/analógico), PWM (Pulse Width Modulation - Modulação por Largura de Pulso), contadores,

temporizadores, interface serial, entre outros, bem como diferentes tipos memória (ROM, EPROM,

EEPROM, FLASH, RAM) e com diferentes capacidades.

Em geral, os microcontroladores são utilizados em aplicações nas quais não há a necessidade

da flexibilidade de interfaceamento dos microprocessadores com memórias e periféricos, bem como o

software que ele executa é único, é armazenado em ROM e é denominado de Firmware.

Dentre inúmeras aplicações, os microcontroladores são encontrados em dispositivos pessoais

móveis (tal como: celular, máquina fotográfica, câmera digital, reprodutores DVD e MP3, GPS, pen

drivers, calculadora etc), eletrodomésticos (televisor, lavadora de roupas e louças, forno de

microondas, videogame, ar condicionado, central de alarme etc), instrumental eletrônico

(osciloscópio, analisador de espectro, analisador lógico, frequencímetro, fontes programáveis etc),

equipamentos médico-hospitalares (medidor de pressão, monitor cardíaco, medidor de glicemia,

tomógrafo etc), equipamentos de automação bancária e comercial (caixa registradora, balança

Estudo do Microcontrolador Hipotético

Página 8

eletrônica, terminal de auto-atendimento, leitor de código de barras, impressora, máquina de café

etc), equipamentos de informática (teclado, monitor LCD, unidade de disco, roteador, modem,

impressora, escâner etc), equipamentos de automação industrial (inversor de frequência, controlador

de temperatura, robô, veículo auto-guiado, esteira, misturador, máquina operatriz etc). A figura 6

ilustra algumas destas aplicações.

Figura 6 – Exemplos de aplicação para o microcontrolador.

Estudo do Microcontrolador Hipotético

Página 9

II. MICROCONTROLADOR HIPOTÉTICO

Nesta seção, será desenvolvido o estudo de uma arquitetura simplificada de um

microcontrolador hipotético, com uma estrutura tenuamente assemelhada ao microcontrolador

8051.

Importante destacar que, por se tratar de um modelo didático, não são detalhados os aspectos

de implementação dos seus componentes, bem como foram adotadas inúmeras simplificações,

objetivando facilitar a sua compreensão.

II.1. Modelo do Programador

Para iniciar o estudo, apresenta-se o modelo do programador que é a representação do

diagrama funcional da arquitetura do microcontrolador, sem a preocupação do detalhamento e da

operação do hardware.

O sistema proposto, ilustrado na figura 7, é constituído pelos seguintes componentes:

a) Unidade Central de Processamento (CPU), com dois registradores de oito bits (um byte)

denominados de A e B; Unidade Lógica e Aritmética (ULA); e Bus de dados de oito bits. A

Unidade de Controle não está representada no modelo;

b) Memória de dados3 - RAM de 128 bytes;

c) Memória de programa (Firmware) – ROM de 1 K (1.024) bytes; e

d) Porta de Entrada/Saída (P0) de oito bits para conexão de periférico de E/S.

3 A separação entre memória de dados e memória de programas é conhecida com arquitetura Harvard (por ter sido

proposta nesta universidade). Caso um único espaço de memória seja compartilhado entre dados e programas, a

arquitetura é conhecida com von Neumann (proposta concebida pelo matemático húngaro John von Neumann – biografia

em http://pt.wikipedia.org/wiki/John_von_Neumann, última consulta em 27 de outubro de 2009).

Estudo do Microcontrolador Hipotético

Página 10

Figura 7 – Modelo do programador para o microcontrolador hipotético.

II.2. Operação do Microcontrolador

Para a compreensão do funcionamento do microcontrolador, quando da execução do

Firmware, será empregado o diagrama funcional apresentado na figura 8.

Figura 8 – Diagrama funcional do microcontrolador hipotético.

O programa que o microcontrolador executa é denominado de Firmware, que deve ser

carregado na memória de programa (ROM). A CPU, ao ser energizada, sofre um Reset fazendo com que

a primeira instrução do programa, localizada no endereço 0000H4 da ROM, seja buscada da memória,

decodificada e executada. Assim, este processo de busca, decodificação e execução é repetido para

cada instrução, até que uma instrução de fim de programa seja encontrada. O sinal de clock determina

a velocidade de realização das operações e, portanto, quanto maior for a frequência do clock, mais

rápida será a execução do programa.

Cada instrução é identifica por uma única codificação binária, denominada de código de

operação (operation code - opcode, em inglês) que a identifica entre as demais. Este opcode é lido da

memória ROM e carregado na Unidade de Controle.

4

O sufixo ″H″ indica um número no sistema de numeração hexadecimal.

Estudo do Microcontrolador Hipotético

Página 11

A Unidade de Controle decodifica o opcode e produz uma sequência de sinais elétricos que

ativam os componentes envolvidos com a execução da instrução. Os sinais de controle definem, assim,

o fluxo de dados entre os componentes que integram o microcontrolador.

O fluxo de dados ocorre com operações envolvendo a porta P0, os registradores A e B, a ULA, a

memória RAM e a memória ROM.

Essas operações são definidas pelas instruções e compreendem, como por exemplo, o seguinte

fluxo de dados:

• carregar o dado armazenado na porta P0, oriundo do periférico de entrada, para o

registrador A (A ← P05);

• carregar o dado armazenado no registrador A para a porta P0 e, consequentemente, ao

periférico de saída (P0 ← A);

• carregar o dado armazenado no registrador A para uma posição da memória RAM

(M[end]6 ← A);

• carregar o dado armazenado na memória RAM para o registrador A (A ← M[end]);

• carregar o dado armazenado no registrador A para o registrador B e vice-versa (B ← A

e A ← B);

• efetuar operações aritméticas (soma e subtração) entre os registradores A e B e salvar o

resultado no registrador A (A ← A + B e A ← A - B);

• efetuar operações lógicas (E, OU e Comparação) entre os registradores A e B (A ← A ∧

B7, A ← A ∨ B8 e A <= B);

• efetuar o complemento do conteúdo do registrador A (A ← ~A9); e

• desviar o fluxo de execução do programa, modificando-se o registrador (não

representado no diagrama da figura 7 por se tratar de registrador de uso especial) que

endereça a próxima instrução a ser executada.

5 Esta

notação é empregada para indicar o fluxo do dado, sendo o componente situado à direita da seta a fonte do dado e o

componente à esquerda o destino dado (destino ← fonte).

6 Utiliza-se a notação M[end] para indicar uma posição de memória, sendo o endereço colocado entre os colchetes.

7 O sinal de “∧” é empregado para representar a operação lógica E (AND).

8 O sinal de “∨” é empregado para representar a operação lógica OU (OR).

9 O sinal de “~” é utilizado para representar a operação lógica de complemento (inversão).

Estudo do Microcontrolador Hipotético

Página 12

II.3. Hardware do microcontrolador hipotético

O diagrama em blocos apresentado na figura 9 detalha o hardware do microcontrolador hipotético.

Figura 9 – Detalhamento do hardware do microcontrolador hipotético.

Estudo do Microcontrolador Hipotético

Página 13

II.4. Descrição do Hardware

O estudo do hardware do microcontrolador hipotético inicia-se pelo Bus de dados que tem por

finalidade possibilitar a transferência de dados entre os componentes que constituem a CPU.

Fisicamente, este Bus é o agrupamento de oito condutores paralelos aos quais são conectados os

registradores, buffers e memórias.

O princípio de operação do Bus, por se tratar de um recurso compartilhado, exige uma

disciplina no seu emprego. Em geral, um determinado componente tanto pode disponibilizar um dado

no Bus, quanto capturá-lo. Alguns componentes realizam ambas as operações, como os registradores

A e B, a memória RAM e a porta P0. Os registradores MRAM, Tmp1, Tmp2, PC e IR somente capturam

o dado do Bus. O buffer da saída da ULA e a memória ROM somente disponibilizam seus dados para o

Bus.

Para se implementar um sistema de Bus, para cada bit do dado, são necessários os

componentes apresentados na figura 10.

Figura 10 – Componentes necessários para se implementar um bit do Bus de dados.

De acordo com a figura 10, cada bit deve possuir dois componentes: (i) um flip-flop tipo D

(latch); e (ii) um buffer tri-state. O flip-flop é responsável pela captura do dado presente no Bus,

enquanto o buffer tri-state é responsável por disponibilizar o bit carregado no latch.

Na operação do latch, o bit do dado presente no Bus é capturado (Q ← D) quando o sinal Clk

(Clock) provocar uma borda de subida. Caso não ocorra esta borda, o latch mantém o bit previamente

armazenado (Q = Qo).

O buffer tri-state opera como uma chave controlada eletricamente pela entrada de controle E’

(Enable - habilitação). Se a entrada de controle E’ for ativada (E’ = 0), a saída Y terá o mesmo valor da

entrada A, ou seja, o buffer comporta-se como uma chave fechada (Y = A). Se a entrada E’ for

desativada (E’ = 1), a saída Y estará em estado de alta impedância, neste caso, o buffer é uma chave

aberta (Y = alta impedância). Importante observar que o buffer tri-state não efetua o armazenamento,

apenas conecta ou desconecta eletricamente o componente ao Bus.

A CPU do microcontrolador hipotético foi concebida como um circuito síncrono, no qual as

transferências de dados entre os diversos componentes ocorrem sob o comando de pulsos de Clock

(Clk), oriundos do circuito de Clock, conforme ilustra a figura 11.

Estudo do Microcontrolador Hipotético

Página 14

Figura 11 – O circuito de Clock sincroniza a transferência de dados entre os componentes da CPU.

Para possibilitar a transferência de dados entre os n componentes (C1, C2, ..., Cn) interligados

ao Bus, dois sinais de controle são necessários: (i) Ei’ – sinal de controle de habilitação do buffer tristate, responsável por disponibilizar dados no Bus; e (ii) Li – sinal de controle de captura ou carga (L

de Load – carga em português) do bit do dado presente no Bus.

A implementação de um registrador de um bit (bloco C da figura 11) é realizada pelo esquema

apresentado na figura 12.

Figura 12 – (a) Diagrama em blocos do registrador de um bit. (b) Implementação do registrador.

De acordo com a figura 12 (a), o registrador de um bit contém o latch, o buffer tri-state e um

multiplexador (Mux) 2:1. O Mux, sob o comando do sinal de controle L, seleciona ou o bit do dado

presente no Bus (entrada A), ou o bit previamente armazenado no latch (entrada B). Caso a entrada A

seja selecionada, na próxima ocorrência de uma borda de subida em Clk, o latch armazenará o bit do

dado presente no Bus. Caso a entrada B seja selecionada, na próxima ocorrência da borda de subida

em Clk, o latch realimentará o bit previamente armazenado, ou seja, mantém inalterado o bit do dado

armazenado no latch.

A figura 12 (b) apresenta o circuito que implementa este registrador de um bit, sendo o

multiplexador formado pelas portas P1, P2, P3, P4 e P5.

Para a implementação de um registrador paralelo de oito bits, como é o caso dos registradores

A e B do microcontrolador hipotético, o circuito deve ser o apresentado na figura 13.

Estudo do Microcontrolador Hipotético

Página 15

Figura 13 – (a) Circuito do registrador de oito bits. (b) Representação sob a forma de bloco.

No circuito da figura 13 (a), observa-se que os terminais Clk devem ser interligados, assim

como os terminais E’ e os terminais L e L’, aos oito conjuntos de flip-flops, buffer

tri-state e portas dos multiplexadores, também, cada bit do conjunto deve ser conectado a uma

linha do Bus de dados.

A figura 13 (b) corresponde à representação do registrador de oito bits sob a forma de blocos.

Observar que é exatamente esta a representação do registrador B, conforme o detalhamento do

hardware apresentado na figura 9.

O registrador A, apresentado na figura 14, é implementado de forma semelhante ao

registrador B, com a adição de um circuito detector de zero, responsável pelo sinal denominado de

Zero A. O circuito que implementa o detector de zero é uma porta NOU, cujas entradas estão ligadas

aos oito bits do registrador A. Assim, a saída Zero A assumirá o valor 1, se, e somente se, o registrador

A contiver o valor 000000002. A saída Zero A, sob o controle de uma porta E, é aplicada, ao flip-flop

que armazena este bit sinalizador (um sinalizador é denominado, em inglês, de flag). A saída do flag

ZA é levada à Unidade de Controle para ser empregado nas instruções de desvio condicional JZ e JNZ,

a serem apresentas na seção II.4.2.

Estudo do Microcontrolador Hipotético

Página 16

Figura 14 – Implementação do registrador A, com o flag Zero (ZA).

A porta P0, empregada para conectar periféricos de Entrada/Saída ao microcontrolador, é

constituída pelos componentes representados na figura 15.

Estudo do Microcontrolador Hipotético

Página 17

Figura 15 – Representação e implementação da porta P0.

De acordo com a figura 15, a estrutura da porta P0 é semelhante a dos registradores A e B, com

a adição de circuitos isoladores-inversores (MOSFETs) ligados às saídas Q’s dos flip-flops. Estes

isoladores operam como buffers inversores, podendo fornecer maiores correntes ao periférico de

Estudo do Microcontrolador Hipotético

Página 18

saída em relação aos níveis de corrente fornecidos pelos flip-flops. Como o bit do flip-flop é obtido da

saída Q’ e este é invertido pelo MOSFET, o nível lógico presente no pino P0.i (para i={0, 1, 2, 3, 4, 5, 6 e

7}) tem o mesmo valor do bit armazenado no flip-flop.

Na operação da porta P0 como saída, ou seja, o periférico recebe o dado do microcontrolador,

os bits de dado devem ser capturados do Bus e armazenados nos flip-flops. Este armazenamento irá

ocorrer quando a entrada LP0 receber nível lógico alto e o sinal Clk apresentar uma borda de subida.

Se LP0 receber um nível lógico baixo, o bit armazenado no flip-flop é realimentado para a entrada D,

não alterando o estado do flip-flop, mesmo quando este recebe uma borda de descida na entrada Clk.

Assim, caso, o flip-flop P0i tenha armazenado o bit “1”, a saída Q‘ terá o valor “0”, fazendo com

que o MOSFET opere em corte. Nesta situação, não há corrente de dreno (Id = 0) e o nível lógico alto é

aplicado ao pino P0.i, via resistor RPU10. Para um bit “0” armazenado no flip-flop, a saída Q’ terá valor

“1”, saturando o MOSFET. Nesta condição, a corrente de dreno é máxima e a tensão Vds será próxima

de 0 Volt, o que corresponde a nível lógico “0”.

Na operação como entrada, ou seja, o periférico fornece um dado para o microcontrolador, os

bits presentes nos pinos P0.0 a P0.7 são disponibilizados no Bus, quando a entrada EP0’ for ativada

(EP0’ = 0) e devem ser capturados pelo registrador A (neste microcontrolador hipotético, apenas o

registrador A é empregado nas operações de entrada/saída com periféricos).

Como, para a operação de entrada, há um MOSFET ligado ao pino P0.i e este, ou encontra-se

cortado ou encontra-se saturado, o estado do transistor pode alterar o bit fornecido pelo periférico.

Esta situação ocorre se o MOSFET estiver saturado e um nível lógico “1” for aplicado ao pino P0.i.

Neste caso, a tensão no pino é “puxada” para baixo e o bit lido será “0”. Para evitar este problema,

deve-se previamente carregar a porta P0 com o valor 111111112, levando os oito MOSFETs ao estado

de corte.

A Unidade Lógica e Aritmética (ULA), apresentada na figura 16, é um circuito combinacional11

responsável pela execução das operações lógicas e aritméticas

10

11

RPU – Resistor de Pull Up (elevador)

Um circuito combinacional não tem elementos de memória, assim a saída só depende dos valores da suas entradas.

Estudo do Microcontrolador Hipotético

Página 19

Figura 16 – Estrutura da Unidade Lógica e Aritmética (ULA).

De acordo com a figura 16, a ULA possui duas entradas (A e B) para operandos de um byte,

uma saída (F) de oito bits, uma entrada de carry (Cyi), uma saída de carry (Cyo) e seis entradas de

seleção da operação, sendo: ADD (soma), SUB (subtração), ANL (E lógico), ORL (OU lógico), CPL

(Complemento) e CMP (Comparação). Os operandos manipulados pela ULA devem ser capturados do

Bus de dados e carregados nos registradores temporários (Tmp1 e Tmp2). O resultado da operação

obtido na saída da ULA (F) é liberado para o Bus de dados quando o sinal EULA’ do buffer tri-state for

ativado (EULA’ = 0). O bit de carry (transporte) é gerado pela ULA para informar o estado das

operações aritméticas (ADD, SUB e CMP) e carregado no flip-flop Cy. Este bit de carry pode ser

empregado tanto pela própria ULA quanto pela Unidade de Controle para operações de desvio

condicional JC (jump if carry – salta se houver transporte) ou JNC (jump if not carry – salta se não

houver transporte)12. O flip-flop Cy é denominado de flag (sinalizador) de carry.

A memória de dados é uma RAM com 128 bytes (128 posições com oito bits por posição),

conforme ilustra o diagrama em blocos da figura 17.

Figura 17 – Diagrama da memória RAM e componentes associados.

Para endereçar esses 128 bytes são necessárias sete linhas de endereços (A0 a A6) e oito

linhas de dados (D0 a D7). O endereçamento da RAM é efetivado pelo registrador MRAM de oito bits,

que captura o endereço do Bus de dados quando a entrada LMRAM é ativada e ocorre uma borda de

subida em Clk.

A RAM possui duas entradas de controle, compreendendo: (i) CE’ (Chip Enable – habilitação da

pastilha) destinada ao controle do estado de alta impedância da RAM; e (ii) WE’ (Write Enable –

habilitação de escrita) destinada a definir se a operação na RAM será de escrita (R/W’ = 0) ou de

leitura (R/W’ = 1).

Como a RAM possibilita tanto a escrita (gravação) como a leitura (recuperação), o sinal R/W'

deve ser gerado pela Unidade de Controle quando uma instrução envolvendo a memória de dados for

executada.

Uma operação de escrita de um byte na RAM ocorre de acordo com a seguinte sequência de

operações: (i) o endereço da posição onde o byte será gravado deve ser carregado no registrador

12 Estas duas instruções JC e JNC não são implementadas, sendo indicadas como exercício complementar ao estudante.

Estudo do Microcontrolador Hipotético

Página 20

MRAM; (ii) o byte a ser armazenado na memória deve ser disponibilizado no Bus de dados; e (iii) a

Unidade de Controle determina que R/W' ← 0 (indicando uma operação de escrita) e CERAM’ ← 0 .

Uma operação de leitura de um byte da RAM ocorre de acordo com a seguinte sequência de

operações: (i) o endereço da posição de onde o byte será lido deve ser carregado no registrador

MRAM; (ii) a Unidade de Controle faz R/W' ← 1 (indicando uma operação de leitura) e CERAM’ ← 0; e

(iii) o dado liberado pela RAM será capturado por algum componente, de acordo com a instrução que

estiver sendo executada.

A ROM é empregada para armazenar as instruções que compõem o Firmware e possui

organização de 1 Kbytes (1.024 posições x 8 bits por posição). Para acessar as 1.024 posições são

necessárias 10 linhas de endereço (A0 a A9) e oito linhas de dados (D0 a D7) para a saída dos bytes

armazenados, conforme apresentado na figura 18.

Figura 18 – Estrutura da memória de programa (ROM).

O endereço de 10 bits é proveniente do registrador de endereçamento da ROM (MROM). Como

este registrador tem 16 bits, e somente 10 bits (A0 a A9) são utilizados, os 6 bits excedentes podem

ser empregados para expansão de memória, pois com 16 bits é possível endereçar até 65.536

posições = 64 K = 216.

O registrador MROM possui uma entrada para o sinal de Clock (Clk) e duas entradas de

controle, sendo: (i) entrada de carregamento (LMROM) que, quando ativada, carrega os 16 bits

oriundos do registrador Contador de Programa (PC) na próxima subida de Clk; e (ii) sinal de

incremento (+1MROM) que, quando ativado, incrementa em uma unidade o conteúdo de MROM. Este

sinal de +1MROM será ativado no processo leitura de dados ou endereços para determinadas

instruções, a ser detalhado no item II.4.1.

Quando a ROM é endereçada, o byte armazenado no endereço presente no MROM será

disponibilizado na saída de dados (pinos D0 a D7) e, portanto, no Bus de dados, após a ativação do

sinal OEROM‘ (Output Enable – habilitação de saída da ROM).

O Contador de Programa (PC – Program Counter), apresentado na figura 19, é o registrador

que retém o endereço do próximo opcode a ser buscado da ROM, ou seja, o PC contém o endereço da

próxima instrução a ser executada pela CPU.

Estudo do Microcontrolador Hipotético

Página 21

Figura 19 – (a) Diagrama dos registradores PC e MROM. (b) Composição do registrador PC.

O PC possui cinco entradas de controle sendo: (i) sinal de Clock (Clk); (ii) sinal de incremento

(+1PC) que, quando ativado, incrementa em uma unidade o conteúdo do PC (PC ← PC + 1); (iii) sinal

de carregamento (LPC) que habilita o carregamento de 8 bits do Bus de dados; (iv) sinal de limpeza

(CLRPC) que, quando ativado, zera o PC (PC ← 0000H); e (v) sinal de deslocamento para a esquerda

(SL8 – Shift Left), cuja finalidade é carregar os 8 bits menos significativos nos 8 bits mais significativos

do PC. Isto permite carregar 16 bits no PC a partir do Bus de dados, cujo tamanho é de 8 bits, sendo

empregado para carregar no PC um endereço de desvio, que ocorre nas instruções de salto (Jump).

A Unidade de Controle é constituída por um conjunto de circuitos responsável pela geração de

todos os sinais de controle do microcontrolador, abrangendo os componentes integrantes da CPU

(registradores de uso geral, registradores de uso específico, buffers tri-state e ULA), das memórias

RAM e ROM e da porta de saída P0.

Os sinais de controle são ativados seletivamente pela Unidade de Controle, de acordo com a

instrução que está sendo executada. Assim, uma instrução envolve um conjunto específico de sinais

de controle denominados de microinstruções, sendo detalhada no item II.5.

A execução completa de uma instrução, ou do seu conjunto de microinstruções, envolve três

ciclos, representados sob a forma de fluxograma na figura 20, e que são denominados de: (i) ciclo de

busca do opcode (opcode fetch); (ii) ciclo de decodificação; e (iii) ciclo de execução.

Estudo do Microcontrolador Hipotético

Página 22

Figura 20 – Ciclos de busca, decodificação e execução do programa (Firmware).

De acordo com a figura 20, após o Reset a Unidade de Controle realiza a busca de um código de

operação (opcode) na memória de programa (ROM). O opcode é, em seguida, decodificado visando

identificar se ele existe ou não e de que instrução ele se trata. No caso do opcode ser válido, a

instrução é executada e a Unidade de Controle retoma o ciclo de busca para um novo opcode. A

sequência do ciclo busca-decodifica-executa só é encerrada quando um opcode inexistente é buscado

da memória. Para retirar o microcontrolador do estado de parado, deve-se acionar o botão de Reset, o

que ocasiona o reinício da busca do primeiro opcode existente na ROM.

O conjunto de circuitos responsável pelos eventos descritos é denominado de Unidade de

Controle, cujo diagrama em blocos está apresentado na figura 21.

Estudo do Microcontrolador Hipotético

Página 23

Figura 21 – Estrutura da Unidade de Controle.

Para o diagrama da figura 21, ao se energizar o microcontrolador o sinal de Reset, produzido

pela rede RC, é aplicado à Unidade de Controle, informando que a execução do Firmware deve ser

iniciada. A partir do Reset, a Unidade de Controle inicia o ciclo de busca do opcode na memória ROM,

carregando-o no Registrador de Instrução (IR). Uma vez que o opcode foi armazenado no IR, inicia-se

o ciclo de decodificação, que ocorre quando o opcode é recebido pelo bloco denominado de

Decodificador de Instruções, cuja finalidade é ativar uma única saída correspondente ao código de

operação da instrução, mantendo as demais 16 saídas inativas. Em caso de opcode válido, ou seja, de

uma instrução existente, a Unidade de Controle inicia o ciclo de execução, ativando as microinstruções

correspondentes ao opcode decodificado. Uma vez concluído o ciclo de execução, a Unidade de

Controle retorna para um novo ciclo de busca. A parada do ciclo de busca - decodificação - execução

ocorre quando um opcode inválido for lido da ROM, o que, neste microcontrolador hipotético,

corresponde ao opcode fora do intervalo de 00H a 1FH (17 instruções válidas).

A velocidade de ativação dos sinais de controle, ou da execução das microinstruções, é

determinada pela frequência do sinal de Clock. Assim, quanto maior a frequência do Clock, mais rápida

será a execução do Firmware.

Estudo do Microcontrolador Hipotético

Página 24

Importante observar que os Flags de Cy e ZA, aplicados à Unidade de Controle, serão

empregados em instruções de desvio condicional, a ser abordado no item II.6.

O projeto do bloco da Lógica de Controle e Temporização pode ser desenvolvido segundo uma

das seguintes técnicas: (i) Controle Fixo13 (Hardwired Control); ou (ii) Controle por

Microprogramação (Microprogrammed Control). A técnica do Controle Fixo, a ser abordada neste

material, pode ser estudada a partir do diagrama em blocos apresentado na figura 22.

Figura 22 – Implementação da Unidade de Controle pela técnica de Lógica de Controle Fixo.

O bloco denominado de Lógica de Controle Fixo é um circuito combinacional que tem as

seguintes entradas: (i) os bits oriundos do Decodificador de Instruções; (ii) os pulsos de sincronização

gerados pelo Gerador de Temporização; (iii) os sinais dos Flag Cy e ZA; (iv) o sinal de sincronização

(Clk); e (iv) o sinal de Reset. Como saída, a Lógica de Controle Fixo produz os sinais de controle para

todos os componentes do hardware do microcontrolador.

De acordo com a figura 22, o Decodificador de Instruções é um circuito combinacional que

recebe como entrada o conteúdo do IR e leva a 1 a saída correspondente ao opcode válido. Assim, se o

opcode 00H for armazenado no IR, o qual corresponde à instrução NOP, a saída 00H irá para 1,

mantendo as demais em 0. Caso o Decodificador receba um opcode inválido, as 17 saídas terão valor 0,

ou seja, nenhuma saída será ativada. Neste microcontrolador hipotético, qualquer opcode inválido é

13 Também denominada de Lógica Aleatória.

Estudo do Microcontrolador Hipotético

Página 25

considerado como uma instrução de parada, cujo efeito é cessar a aplicação do sinal de Clock em todo

o hardware. O circuito que identifica o opcode inválido é denominado de Detector de opcode inválido e

é implementado com uma lógica OU envolvendo as 17 saídas do Decodificador de Instruções.

O bloco designado de Gerador de Temporização é um Contador em Anel (Ring Counter) que

produz as temporizações (T0, T1, ..., T5) e tem como função disciplinar a ativação dos sinais de

controle. A figura 23 apresenta as formas de onda geradas por este circuito.

Clk

T0

T1

T2

T3

T4

T5

Figura 23 – Formas de ondas geradas pelo Contador em Anel.

Para o projeto da Lógica de Controle Fixo, deve-se efetuar o estudo da execução das microinstruções

para cada uma das 17 instruções, incluindo o ciclo de busca do opcode na ROM. Este estudo é realizado por

intermédio dos diagramas de temporização dos sinais de controle, de acordo com o clock e os sinais

produzidos pelo Gerador de Temporização.

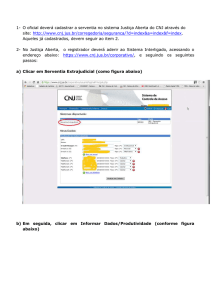

O diagrama de temporização para o ciclo de busca de opcode está apresentado na figura 24.

Estudo do Microcontrolador Hipotético

Página 26

Figura 24 – Diagrama de temporização para o ciclo de busca do opcode.

De acordo o diagrama de temporização da figura 24, a busca do opcode compreende os seguintes

eventos:

• no tempo de nível alto de T0, o sinal LMROM é ativado, habilitando o registrador MROM

receber o endereço diretamente do PC, responsável pelo armazenamento do endereço

da próximo opcode a ser buscado da ROM;

• na subida do Clk, em t2, ocorre o carregamento do endereço no MROM;

• a partir de t2, o endereço é aplicado aos pinos A0 até A9 da ROM (no tempo anterior à

t2, as linhas A0 até A9 continham o endereço do opcode da última instrução que fora

executada);

• em t3, quando inicia-se o tempo de nível alto de T1, os sinais CEROM’ e OEROM’ são

ativados, fazendo com que a ROM disponibilize o dado nas linhas D0 a D7, que, neste

caso, é o opcode;

• em T1, também é ativado o sinal LDIR, que habilita o carregamento do opcode no

registrador IR; e

• o carregamento do opcode no IR ocorre no tempo t4, quando há a subida do sinal Clk.

Observar que o ciclo de busca do opcode só necessita dos tempos T0 e T1. Os demais tempos do

Gerador de Temporização (T2 a T5), são empregados para os ciclos de decodificação e execução de cada

instrução.

Com base nos diagramas de temporização, pode-se mapear o momento em cada sinal de controle

será ativado de acordo com a instrução a ser executada, gerando uma matriz na qual as coordenadas das

linhas são os sinais de controle, as coordenadas das colunas o opcode decodificado e os elementos desta

matriz são os tempos T0 a T5, produzidos pelo Gerador de Temporização. A matriz dos sinais de controle

do microcontrolador hipotético está apresentada no quadro 1.

Estudo do Microcontrolador Hipotético

Página 27

T4

T4’

T3’

T3’

T3’

T2+T3

T3’

T3’

T2

T2+T3

T4’

T3

T3

T4’

06H

MOV A,n8

05H

T3’

T2

04H

T2

T2

03H

T2

T2+T3

02H

MOV B,#b MOV A,B MOV B,A MOV n8,A

T2

T2’

07H

MOV P0,A

T2

T2

08H

MOV A,P0

Estudo do Microcontrolador Hipotético

T4

T4

T4’

T4’

T4

T2

T2

T4

T3

T2

0AH

SUB

T3

T2

09H

ADD

T4’

T4

T4

T2

T3

T2

0BH

ANL

Página 28

T4’

T4

T4

T2

T3

T2

0CH

ORL

T4’

T4

T2

0DH

CPL

T4

T2

0EH

CMP

T4

T4

T3’+T5’

T3’+T5’

ZAT3+ZAT5

T3+T5

CERAM’

R/W’

LMRAM

EP0

LP0

Sinal

LS8

LMROM

ZAT2+ZAT4 +1MROM

T4

ZA’T3+ZA’T5 LPC

ZAT2+ZAT3 +1PC

11H

JZN

EULA’

CMP

CPL

ORL

ANL

SUB

ADD

LCy

LT1

LT2

LIR

ZAT3’+ZAT5’ ZA’T3’+ZA’T5’ OEROM’

ZAT3’+ZAT5’ ZA’T3’+ZA’T5’ CEROM’

ZA’T2+ZA’T4

ZA’T2+ZA’T3

10H

JZ

T2+T4

0FH

JMP

Quadro 1 – Matriz de tempos de ativação dos sinais de controle para cada instrução, incluindo a busca do

opcode.

T3’

T3’

T0

T1’

T1’

T1

LMROM

CEROM’

OEROM’

LIR

Sinal

LP0

EP0

LMRAM

R/W’

CERAM’

+1PC

LPC

LS8

+1MROM

LMROM

CEROM’

OEROM’

LIR

LT2

LT1

LCy

ADD

SUB

ANL

ORL

CPL

CMP

EULA’

Quadro 2 – Equações lógicas dos sinais de controle

Equação Lógica

08H.T2

07H.T2’

05H.T3+06H.T3

05H.T4’+06H.T4

05H.T4’+06H.T4

00H.T2+01H(T2+T3)+02H(T2+T3)+03H.T2+04H.T2+05H(T2+T3)+06H(T2+T3

)+07H.T2+08H.T2+09H.T2+0AH.T2+0BH.T2+0CH.T2+0DH.T2+0EH.T2+0FH(T2

+T4)+10H(ZA’T2+ZA’T3)+11H(ZAT2+ZAT3)

0FH(T3+T5)+10H(ZA.T3+ZA.T5’)+11H(ZA’.T3+ZA’.T5)

0FH.T4+10H.ZA.T4+11H.ZA’.T4

01H.T2+02H.T2+05.HT2+06.HT2+10H(ZA’.T2+ZA.T4)+11H(ZA.T2+ZA.T4)

T0

T1’+01.HT3’+02H.T3’+05H.T3’+06H.T3’+0FH(T3’+T5’)+10H(ZA.T3’+ZA.T5’)+11

H(ZA’.T3’+ZA’.T5’)

T1’+01.HT3’+02H.T3’+05H.T3’+06H.T3’+0FH(T3’+T5’)+10H(ZA.T3’+ZA.T5’)+11

H(ZA’.T3’+ZA’.T5’)

T1

09H.T3+0AHT3+0BHT3+0CHT3

09H.T2+0AHT2+0BHT2+0CHT2

09H.T4+0AHT4+0BHT4+0CHT4

09H.T4

0AH.T4

0BH.T4

0CH.T4

0DH.T4

0EH.T4

09H.T4’+0AH.T4’+0BH.T4’+0CH.T4’+0DH.T4’

Estudo do Microcontrolador Hipotético

Página 29

EULA’

CMP

CPL

ORL

ANL

SUB

ADD

LCy

LT1

+1MROM

LS8

LPC

+1PC

CERAM’

R/W’

LMRAM

EP0

LP0

LT2

T2

00H

T2

T2+T3

01H

MOV A,#b

NOP

Fetch

Sinal

A partir da matriz apresentada no quadro 1, pode-se equacionar os sinais de controle,

conforme apresentado na quadro 2.

LB

EB’

LA

EA’

LZA

02H.T3+04H.T2

03H.T2’+09H.T3’+0AH.T3’+0BH.T3’+0CH.T3’

01H.T3+03H.T2+06H.T4+07H.T2+09H.T4+0AH.T4+0BH.T4+0CH.T4

04H.T2’+05H.T4’+08H.T2’+09H.T2’+0AH.T2’+0BH.T2’+0CH.T2’+0DH.T2’

01H.T4+03H.T3+06H.T5+07H.T3+09H.T5+0AH.T5+0BH.T5+0CH.T5+0DH.T5

A partir destas equações, os circuitos para cada sinal de controle podem ser desenhados como,

por exemplo, o circuito do sinal LPC (do quadro 2, LPC = 0FH(T3 + T5) + 10H(ZAT3 + ZAT5’) +

11H(ZA’T3 +ZA’T5) = 0FH(T3 + T5) + 10HZA(T3 + T5’) + 11HZA’(T3 + T5)), apresentado na figura 25.

Figura 25 - Implementação do circuito para o sinal LPC.

II.5. Conjunto de Instruções

Uma instrução é uma ordem para que o hardware efetue alguma operação e produza algum

resultado. Uma sequência organizada de operações executada pelo hardware é denominada de

programa. Para se elaborar um programa, três conhecimentos devem ser dominados pelo

programador, compreendendo:

(i)

o algoritmo, que é o sequenciamento de operações que o hardware deve executar para

produzir o resultado desejado;

(ii)

os recursos que o hardware dispõe (registradores, operações da ULA, operações de E/S,

capacidade da memória RAM, entre outras) e como utilizá-los; e

(iii) o conjunto de instruções que o hardware é capaz de executar.

Estudo do Microcontrolador Hipotético

Página 30

A elaboração do algoritmo deve ser a primeira etapa a ser realizada na construção de um

programa. Uma vez concebida a solução algorítmica, ela deve ser codificada na linguagem de

programação do hardware. Assim, a codificação consiste em selecionar do conjunto de instruções

disponível aquelas que, quando executadas, produziram os resultados esperados.

Na sua forma mais reduzida, uma instrução é um código binário que deve ser armazenado na

memória de programa. Neste nível de hardware, a programação é denominada de linguagem de

máquina. Para se evitar a programação em linguagem binária utiliza-se a programação em um nível

de linguagem mais inteligível, denominada de linguagem de montagem (Assembly Language). Neste

nível de linguagem, cada instrução é escrita em uma forma mnemônica, de fácil leitura e

memorização.

O microcontrolador hipotético foi concebido para executar um conjunto simplificado de 17

instruções, observando o seguinte grupamento:

• instrução sem operação;

• instruções de movimento de dados;

• instruções lógicas;

• instruções aritméticas; e

• instruções de desvio.

O quadro 3 apresenta as 18 instruções que o microcontrolador é capaz de executar.

Quadro 3 – Conjunto de instruções do microcontrolador.

Opcode Mnemônico nBytes Operação

00

NOP

1

nenhuma

01

MOV

2

A ← byte; Se (A == 00H) ZA ← 1, Senão ZA ← 0

A,#byte

02

MOV

2

B ← byte

B,#byte

03

MOV A,B

1

A ← B; Se (A == 00H) ZA ← 1, Senão ZA ← 0

04

MOV B,A

1

B←A

05

MOV n8,A

2

RAM[n8] ← A

06

MOV A,n8

2

A ←RAM[n8]; Se (A == 00H) ZA ← 1, Senão ZA ← 0

07

MOV P0,A

1

P0 ← A

08

MOV A,P0

1

A ← P0; Se (A == 00H) ZA ← 1, Senão ZA ← 0

09

ADD A,B

1

A ← A + B; Se (A > FFH) Cy ←1, Senão Cy ← 0; Se (A == 00H) ZA ←

1, Senão ZA ← 0

0A

SUB A,B

1

A ← A - B; Se (A < 0) Cy ← 1, Senão Cy ← 0; Se (A == 00H) ZA ← 1,

Senão ZA ← 0

0B

ANL A,B

1

A ← A ^ B; Se (A == 00H) ZA ← 1, Senão ZA ← 0

0C

ORL A,B

1

A ← A ∨ B; Se (A == 00H) ZA ← 1, Senão ZA ← 0

0D

CPL A

1

A ← Ā; Se (A == 00H) ZA ← 1, Senão ZA ← 0

0E

CMP A,B

1

Se (A < B) Cy ← 1, Senão Cy ← 0

0F

JMP end16

3

PC ← end16

10

JZ end16

3

Se (ZA == 1) PC ← end16, Senão PC ← PC + 3

11

JNZ end16

3

Se (ZA == 0) PC ← end16, Senão PC ← PC + 3

Estudo do Microcontrolador Hipotético

Página 31

Na tabela 3, a coluna Opcode define o código de operação único de cada instrução e está

representado no sistema de numeração hexadecimal.

A coluna Mnemônico é a forma descritiva da instrução com a finalidade de facilitar a

memorização e leitura das instruções.

A coluna nBytes informa o tamanho da instrução em número de bytes. Este valor informa

quantas posições uma instrução ocupa na memória de programa (ROM). Conforme se observa na

tabela, o microcontrolador possui instruções de um, dois ou três bytes.

A coluna Operação é a representação simbólica da execução da instrução, com a indicação da

atuação dos flags ZA e Cy.

II.6. Descrição das Instruções

A seguir estão apresentadas as descrições de todas as instruções do microcontrolador.

Instrução: NOP (No Operation – Sem operação)

Opcode: 00H

Tamanho: 1 byte

Operação simbólica: Nenhuma

Ação: Não modifica o estado da CPU. Esta instrução é, em geral, empregada para duas finalidades: (i)

reservar espaço na memória de programa; e (ii) gastar tempo de execução do programa. Estas duas

finalidades serão abordadas na seção III, no assunto programação em assembly.

Exemplo:

Endereço(1) Código

Instrução

Comentário

0000

00

NOP

; sem operação

0001

00

NOP

; sem operação

0002

FF

END(2)

; fim do programa

(1) A coluna endereço indica a localização dos opcodes na memória ROM e, portanto, os

valores que o Contador de Programa (PC) assume na execução do programa.

(2) END não é uma instrução do microcontrolador. Ela é uma pseudo-instrução empregada

para informar ao hardware o término do ciclo de Busca.

Instrução: MOV A,#byte

Opcode: 01H

Tamanho: 2 bytes

Descrição: O prefixo “#” (sustenido) posicionado antes do byte, informa que o número que se segue é

uma constante de oito bits (um byte). O byte fonte será carregado no registrador destino A.

Operação simbólica: A ← byte; Se (A == 00H) ZA ← 1, Senão ZA ← 0.

Ação: Carrega o byte codificado após o sinal “#“ no registrador A. O byte é uma constante armazenada

na memória ROM, logo após o opcode da instrução MOV. O flag ZA é levado a 1 se o byte for igual a

00H. Caso o byte seja diferente de 00H, o flag ZA é levado a 0.

Estudo do Microcontrolador Hipotético

Página 32

Exemplo:

Endereço

0000

0002

Código

01 55

FF

Instrução

MOV A,#55

END

Comentário

; A ← 55H

; fim do programa

Resultado: A = 55H

Instrução: MOV B,#byte

Opcode: 02H

Tamanho: 2 bytes

Operação simbólica: B ← byte

Descrição: O prefixo “#” (sustenido) informa que o número que se segue é uma constante de oito bits

(um byte). O byte fonte será carregado no registrador destino B .

Ação: Carrega o byte definido após o sinal “#” no registrador B. O byte é uma constante armazenada

na memória ROM, logo após o opcode da instrução MOV.

Exemplo:

Endereço

0000

0002

Código

02 D3

FF

Instrução

MOV B,#D3

END

Comentário

; B ← D3H

; fim do programa

Resultado: B = D3H

Instrução: MOV A,B

Opcode: 03H

Tamanho: 1 byte

Descrição: O registrador B é a fonte do dado e o registrador A é o destino.

Operação simbólica: A ← B; Se (A == 00H) ZA ← 1, Senão ZA ← 0.

Ação: Carrega o registrador A com o byte armazenado no registrador B. Após a execução da instrução,

os registradores A e B terão os mesmos valores. Se o valor carregado no registrador A for igual a 00H,

o flag ZA será levado a 1, senão, será levado a 0.

.

Exemplo:

Endereço Código

Instrução

Comentário

0000

02 22

MOV B,#22

; B ← 22H

0002

03

MOV A,B

;A←B

0003

FF

END

; fim do programa

Resultado: A = 22H e B = 22H

Instrução: MOV B,A

Opcode: 04H

Estudo do Microcontrolador Hipotético

Página 33

Tamanho: 1 byte

Descrição: O registrador B é a fonte do dado e o registrador A é o destino.

Operação simbólica: B ← A.

Ação: Carrega o registrador B com o byte armazenado no registrador A. Após a execução desta

instrução os registradores A e B terão os mesmos valores.

Exemplo:

Endereço

0000

0002

0003

Código

01 4A

04

FF

Instrução

MOV A,#4A

MOV B,A

END

Comentário

; A ← 4AH

;B←A

; fim do programa

Resultado: A = 4AH e B = 4AH

Instrução: MOV n8,A

Opcode: 05H

Tamanho: 2 bytes

Descrição: O registrador A é a fonte do dado e o destino é a memória RAM, indicado por M[n8], onde

n8 é o endereço da posição destino. Como a RAM é de 128 bytes, o seguinte limite deve ser observado:

7FH ≥ n8 ≥ 00H (em decimal, 127 ≥ n8 ≥ 0).

Operação simbólica: M[n8] ← A.

Ação: Copia o byte armazenado no registrador A em uma determinada posição da memória RAM, cujo

endereço é o valor n8. Após a execução da instrução, o registrador A e a posição n8 da RAM terão os

mesmos valores.

Exemplo:

Endereço

0000

0002

0004

Código

01 7F

05 00

FF

Instrução

MOV A,#7F

MOV 00,A

END

Comentário

; A ← 7FH

; M[00] ← A

; fim do programa

Resultado: A = 7FH e M[00] = 7FH

Instrução: MOV A,n8

Opcode: 06H

Tamanho: 2 bytes

Descrição: A memória RAM é a fonte do dado e o registrador A é o destino. A posição da memória

RAM é indicada por M[n8], onde n8 é o endereço do byte que será carregado no registrador A.

Operação simbólica: A ←M[n8]; Se (A == 00H) ZA ← 1, Senão ZA ← 0.

Ação: O byte armazenado no endereço n8 da RAM é carregado no registrador A. Após a execução da

instrução, o registrador A e a posição n8 da RAM terão os mesmos valores.

Estudo do Microcontrolador Hipotético

Página 34

Exemplo:

Endereço

0000

0002

0004

0006

0008

Código

01 7F

05 00

01 22

06 00

FF

Instrução

MOV A,#7F

MOV 00,A

MOV A,#22

MOV A,00

END

Comentário

; A ← 7FH

; M[00] ← A

; A ← 22H

; A ← M[00]

; fim do programa

Resultado: A = 7FH e M[00] = 7FH (observar que a instrução MOV A,#22 não tem efeito ao final do

programa).

Instrução: MOV P0,A

Opcode: 07H

Tamanho: 1 byte

Descrição: O registrador A é a fonte do dado e a porta P0 é o destino.

Operação simbólica: P0 ← A

Ação: Copia na porta P0 o byte armazenado no registrador A, sendo este valor destinado ao periférico

de saída. Após a execução desta instrução, o registrador A e a porta P0 terão os mesmos valores.

Exemplo:

Endereço

0000

0002

0003

Código

01 F0

07

FF

Instrução

MOV A,#F0

MOV P0,A

END

Comentário

; A ← F0H

; P0 ← A

; fim do programa

Resultado: A = F0H e P0 = F0H

Instrução: MOV A,P0

Opcode: 08H

Tamanho: 1 byte

Operação simbólica: A ← P0; Se (A == 00H) ZA ← 1, Senão ZA ← 0.

Descrição: A porta P0 é a fonte do dado e o registrador A é o destino.

Ação: Copia no registrador A o byte armazenado na porta P0, sendo este valor oriundo do periférico

de entrada. Após a execução desta instrução, o registrador A e a porta P0 terão os mesmos valores.

Exemplo:

Endereço

0000

0001

Código

08

FF

Instrução

MOV A,P0

END

Comentário

; A ← P0

; fim do programa

Resultado: A = P0 (o valor de P0 corresponde ao byte fornecido pelo periférico de entrada).

Estudo do Microcontrolador Hipotético

Página 35

Instrução: ADD A,B

Opcode: 09H

Tamanho: 1 byte

Descrição: O registrador B e o registrador A são os operandos (ou parcelas) da soma. O resultado é

armazenado no registrador A.

Operação simbólica: A ← A + B; Se (A > FFH) Cy ←1, Senão Cy ← 0; Se (A == 00) ZA ← 1, Senão ZA

← 0.

Ação: Efetua a soma do conteúdo do registrador A com o conteúdo do registrador B e o resultado é

armazenado no registrador A. O valor anterior do registrador A é perdido. Caso o resultado da soma

seja maior do que 255 (FFH), o registrador A armazenará os oito bits menos significativos do

resultado e o flag de carry será levado ao estado de set (bit 1). Caso o resultado seja menor do que

255, o flag de carry é levado ao reset (bit 0). O flag ZA é levado ao set se o resultado da soma for igual a

00H. Caso o resultado da soma seja diferente de zero, o flag ZA é levado ao reset.

Exemplo:

Endereço

0000

0002

0004

0005

Código

01 5E

02 A7

09

FF

Instrução

MOV A,#5E

MOV B,#A7

ADD A,B

END

Comentário

; A ← 5EH

; B ← A7H

;A←A+B

; fim do programa

Operação:

ZA Cy registrador

binário

hexa decimal

A

0 1 0 1 1 1 1 0 5E

94

B

1 0 1 0 0 1 1 1 A7

167

0 1 A ← A + B 0 0 0 0 0 1 0 1 05

261*

* resultado: Cy = 1 e A = 05, onde: 256 (Cy) + 5 (reg. A) = 261

Resultado: A = 05H, B = A7H, ZA = 0 e Cy = 1

Instrução: SUB A,B

Opcode: 0AH

Tamanho: 1 byte

Descrição: O registrador B e o registrador A são os operandos da subtração. O resultado é

armazenado no registrador A.

Operação simbólica: A ← A - B;

Se (A < 00) Cy ←1, Senão Cy ← 0;

Se (A == 00) ZA ← 1, Senão ZA ← 0.

Ação: Efetua a subtração entre do conteúdo do registrador A e o conteúdo do registrador B, com o

resultado armazenado no registrador A. O valor anterior do registrador A é perdido. Caso o conteúdo

do registrador A seja menor do que o conteúdo do registrador B, antes da subtração, o flag de carry

Estudo do Microcontrolador Hipotético

Página 36

(na subtração funciona como borrow – empresta um) será levado a 1. Caso o conteúdo de A seja maior

do que o do B, o flag de carry é levado a 0. O flag ZA é levado a 1 se o resultado da subtração for igual a

00H. Caso o resultado seja diferente de 00H, o flag ZA é levado a 0.

Exemplo:

Endereço

0000

0002

0004

0005

Código

01 7F

02 A7

0A

FF

Instrução

MOV A,#7F

MOV B,#A7

SUB A,B

END

Comentário

; A ← 7FH

; B ← A7H

;A←A-B

; fim do programa

Operação: A subtração entre A e B (ou seja, A – B) é realizada pela ULA sob a forma: A + (-B), onde –B

é a representação em complemento de dois de B. O complemento de dois14 de um número binário b é

obtido efetuando-se o complemento de b (~b) e adicionando-se 1, ou seja: -b = ~b + 1.

Determinação do complemento de B

ZA Cy registrador

binário

hexa

B

1 0 1 0 0 1 1 1 A7

~B

0 1 0 1 1 0 0 0

+1

1

(-B)

0 1 0 1 1 0 0 1 59

Execução da subtração

A

0 1 1 1 1 1 1 1

+ (-B)

0 1 0 1 1 0 0 1

0 0 A ← A + (-B) 1 1 0 1 1 0 0 0

7F

59

D8*

decimal

127

89

216 (-40)

Resultado: A = D8H, B = A7H, ZA = 0 e Cy = 0

Instrução: ANL A,B

Opcode: 0BH

Tamanho: 1 byte

Descrição: O registrador B e o registrador A são os operandos da operação lógica E. O resultado é

armazenado no registrador A.

Operação simbólica: A ← A ∧ B; Se (A == 00) ZA ← 1, Senão ZA ← 0.

Ação: Efetua a operação lógica E (AND) entre do conteúdo do registrador A e o conteúdo do

registrador B, com o resultado armazenado no registrador A. O valor anterior do registrador A é

14

Na notação em complemento de dois, o bit mais significativo representa o sinal. Se este bit for igual a 1, o número é

negativo, se ele for igual a 0, o número é positivo. Para se encontrar o módulo deve-se efetuar a operação (~b + 1). Assim,

se b = D8H = 110110002, ele é um número negativo. O módulo vale: ~b = 001001112, ~b + 1 = 00101000 = 4010 e D8H = 4010.

Estudo do Microcontrolador Hipotético

Página 37

perdido. O flag ZA é levado a 1 se o resultado da operação E for igual 00H. Caso o resultado seja

diferente de 00H, o flag ZA é levado a 0.

Exemplo:

Endereço

0000

0002

0004

0005

Código

01 4A

02 A5

0B

FF

Instrução

MOV A,#4A

MOV B,#A5

ANL A,B

END

Comentário

; A ← 4AH

; B ← A5H

;A←A∧B

; fim do programa

Operação:

ZA registrador

A

0 1 0

B

1 0 1

1

A←A∧B 0 0 0

binário

hexa

0 1 0 1 0 4A

0 0 1 0 1 A5

0 0 0 0 0 00

Resultado: A = 00H, B = A5H e ZA = 1

Instrução: ORL A,B

Opcode: 0CH

Tamanho: 1 byte

Descrição: O registrador B e o registrador A são os operandos da operação lógica OU. O resultado é

armazenado no registrador A.

Operação simbólica: A ← A ∨ B; Se (A == 00) ZA ← 1, Senão ZA ← 0.

Ação: Efetua a operação lógica OU (OR) entre o conteúdo do registrador A e o conteúdo do

registrador B, com o resultado armazenado no registrador A. O valor anterior do registrador A é

perdido. O flag ZA é levado a 1, se o resultado da operação OU for igual 00H. Caso o resultado seja

diferente de 00H, o flag ZA é levado a 0.

Exemplo:

Endereço

0000

0002

0004

0005

Código

01 4A

02 A5

0B

FF

Instrução

MOV A,#4A

MOV B,#A5

ORL A,B

END

Comentário

; A ← 4AH

; B ← A5H

;A←A∨B

; fim do programa

Operação:

ZA registrador

A

0 1 0

B

1 0 1

0

A←A∨B 1 1 1

binário

hexa

0 1 0 1 0 4A

0 0 1 0 1 A5

0 1 1 1 1 EF

Estudo do Microcontrolador Hipotético

Página 38

Resultado: A = EFH, B = A5H e ZA = 0

Instrução: CPL A

Opcode: 0DH

Tamanho: 1 byte

Descrição: Esta é uma operação com um único operando armazenado no registrador A, que é tanto a

fonte quanto o destino.

Operação simbólica: A ← ~A; Se (A == 00) ZA ← 1, Senão ZA ← 0.

Ação: Efetua o complemento do conteúdo do registrador A. O valor anterior do registrador A é

perdido. O flag ZA é levado a 1 se o resultado da operação CPL for igual a 00H. Caso o resultado seja

diferente de 00H, o flag ZA é levado a 0.

Exemplo:

Endereço

0000

0002

0003

Código

01 83

0D

FF

Instrução

MOV A,#83

CPL A

END

Comentário

; A ← 83H

; A ← ~A

; fim do programa

Operação:

ZA registrador

binário

hexa

A

1 0 0 0 0 0 1 1 83

0

~A

0 1 1 1 1 1 0 0 7C

Resultado: A = 7CH e ZA = 0

Instrução: CMP A,B

Opcode: 0EH

Tamanho: 1 byte

Descrição: Os bytes armazenados nos registradores A e B são comparados e o flag Cy, se levado ao

estado de set, indicará a condição de A < B.

Operação simbólica: A - B; Se (A < B) Cy ←1, Senão Cy ← 0.

Ação: Efetua a subtração entre do conteúdo do registrador A e o conteúdo do registrador B, porém o

resultado é desprezado. Caso o conteúdo do registrador A seja menor do que o conteúdo do

registrador B, o flag de carry (na subtração funciona como borrow – empresta um) será levado ao

valor 1. Caso o conteúdo de A seja maior do que o B, o flag de carry é levado a 0.

Exemplo:

Endereço

0000

0002

Código

01 80

02 84

Instrução

MOV A,#80

MOV B,#84

Comentário

; A ← 80H

; B ← 84H

Estudo do Microcontrolador Hipotético

Página 39

0004

0005

0E

FF

CMP A,B

END

; compara A com B e afeta Cy

; fim do programa

Operação:

ZA Cy

registrador

binário

hexa

decimal

A

1 0 0 0 0 0 0 0 80

128

B

1 0 0 0 0 1 0 0 84

132

0 1

A-B

1 1 1 1 1 1 0 0 FC*

252 (-4)

* Resultado desprezado. Os conteúdos dos registradores A e B não se

alteram após a comparação.

Resultado:

A = 80H, B = 84H, ZA = 0 e Cy = 1

Instrução: JMP end16

Opcode: 0FH

Tamanho: 3 bytes

Descrição: O mnemônico JMP significa JuMP (salto) e a instrução é empregada para desviar o fluxo de

execução do programa. Este desvio é implementado com o carregamento do Contador de Programa

(PC) com o endereço da memória ROM para onde o programa deve ser executado.

Operação simbólica: PC ← end16

Ação: Efetua um desvio incondicional na execução do programa para o endereço codificado na

instrução (end16). Na execução desta instrução, o PC (Contador de Programa) assume os dois bytes

de end16. Os dois bytes de end16 devem compor um endereço válido no espaço de 1K da memória de

programa.

Exemplo: Implementar uma contagem crescente em módulo 25610 no registrador A, indefinidamente.

Endereço

0000

0002

0004

0005

0008

Código

01 00

02 01

09

0F 00 04

FF

Instrução

MOV A,#00

MOV B,#01

ADD A,B

JMP 0004

END

Comentário

; A ← 00H

; B ← 01H

; A ← A+ B

; PC ← 0004H

; fim do programa

Instrução: JZ end16

Opcode: 10H

Tamanho: 3 bytes

Descrição: O mnemônico JZ significa Jump Zero (salta se for zero) e a instrução é empregada para

desviar o fluxo de execução do programa, caso o byte armazenado no registrador A seja igual a 00H.

Estudo do Microcontrolador Hipotético

Página 40

Este desvio é implementado com o carregamento condicional do Contador de Programa (PC) com o

endereço da memória ROM para onde o programa deve ser executado.

Operação simbólica: Se (A == 00H) PC ← end16, Senão PC ← PC + 3;

Ação: Efetua um desvio na execução do programa, caso o conteúdo do registrador A seja igual a 00H.

Esta condição é definida pelo estado do flag ZA. Deste modo, se o flag ZA seja igual a 1, ou seja, o valor

corrente do registrador A é igual 00H, o PC é carregado com o endereço de desvio (PC ← end16), caso

contrário, o programa segue seu fluxo normal de execução (PC ← PC + 3).

Exemplo: Testar o conteúdo da porta P0. Caso ele seja igual a 00H, carregar o registrador B com o

byte 55H, caso contrário, carregá-lo com 66H.

Endereço

0000

0001

0004

0006

0009

000B

Código

08

10 00 09

02 66

09 00 0B

02 55

FF

Instrução

MOV A,P0

JZ 0009

MOV B,#66

JMP 000B

MOV B,#55

END

Comentário

; A ← P0

; se (A == 00H) PC ← 0009

; senão B ← 66H

; PC ← 000BH

; B ← 55H

; fim do programa

Instrução: JNZ end16

Opcode: 11H

Tamanho: 3 bytes

Descrição: O mnemônico JNZ significa Jump Not Zero (salta se não for zero) e a instrução é

empregada para desviar o fluxo de execução do programa, caso o byte armazenado no registrador A

seja diferente de 00H. Este desvio é implementado com o carregamento condicional do Contador de

Programa (PC) com o endereço da memória ROM para onde o programa deve ser executado.

Operação simbólica: Se (A != 00H) PC ← end16, Senão PC ← PC + 3;

Ação: Efetua um desvio, caso o conteúdo do registrador A seja diferente de 00H. Esta condição é

definida pelo estado do flag ZA. Deste modo, caso o flag ZA seja igual a 0, ou seja, o valor corrente do

registrador A é diferente de 00H, o desvio é executado (PC ← end16) . Caso contrário, o programa

segue seu fluxo normal de execução (PC ← PC + 3).

Exemplo: Testar o conteúdo da porta P0. Caso ele seja diferente de 00H, carregar o registrador B com

o byte 55H, caso contrário, carregá-lo com 66H.

Endereço

0000

0001

0004

0006

0009

000B

Código

08

11 00 09

02 66

09 00 0B

02 55

FF

Instrução

MOV A,P0

JNZ 0009

MOV B,#66

JMP 000B

MOV B,#55

END

Comentário

; A ← P0

; se (A != 00H) PC ← 0009

; senão B ← 66H

; PC ← 000BH

; B ← 55H

; fim do programa

Estudo do Microcontrolador Hipotético

Página 41

III. PROGRAMAÇÃO EM LINGUAGEM DE MÁQUINA

III.1. Linguagem de Programação

Os componentes eletrônicos que constituem o hardware operam em dois estados mutuamente

exclusivos (ligado ou desligado) para representarem os dois dígitos do sistema de numeração binário

(1 ou 0). Assim, um programa para ser interpretado pelo hardware deve ser carregado na memória

ROM tendo as suas instruções codificadas na forma binária. Este programa irá gerar no hardware a

execução das microinstruções que correspondem aos sinais de controle, gerados pela Unidade de

Controle, para os componentes envolvidos com as instruções, conforme apresentado na seção II.

Um programa em binário é denominado de programa em linguagem de máquina e era a forma

de programação dos primeiros computadores digitais desenvolvidos na década de 40. Esta forma de