Captulo 4

Logica Seq

uencial

4.1 Introduc~ao

Nos circuitos combinacionais, as sadas em um instante t dependiam unica e exclusivamente das

entradas do circuito naquele mesmo instante, ou seja, do estado atual de suas entradas. Nos

circuitos que estudaremos neste captulo, as sadas n~ao dependem mais somente do estado atual

das entradas, mas tambem de estados anteriores do circuito.

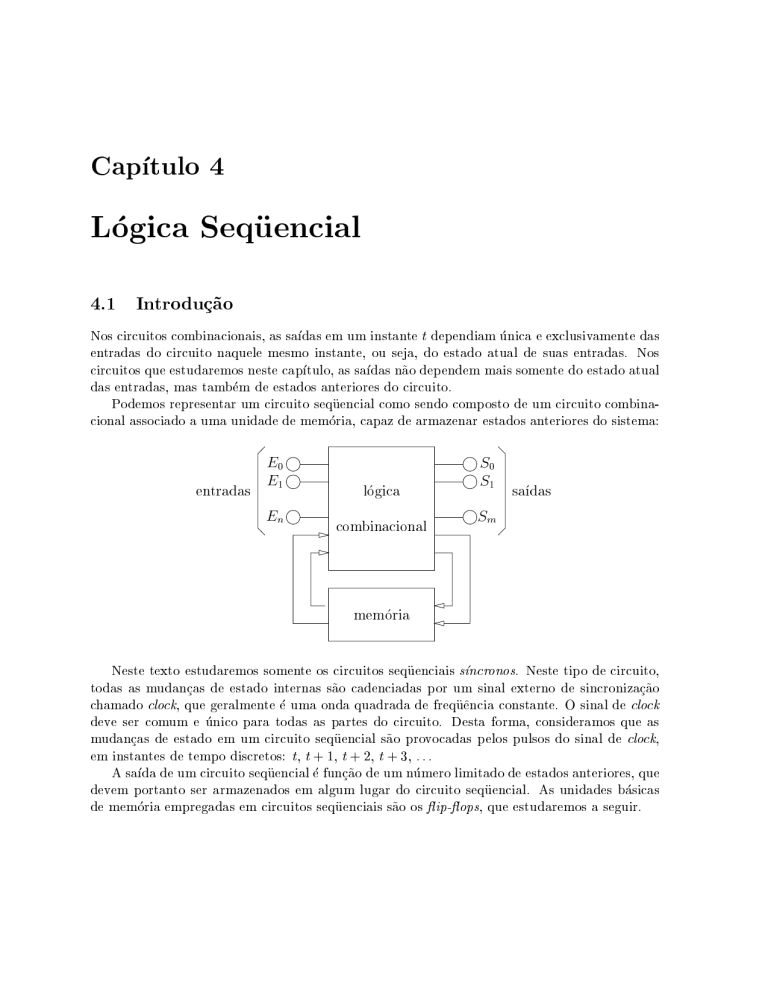

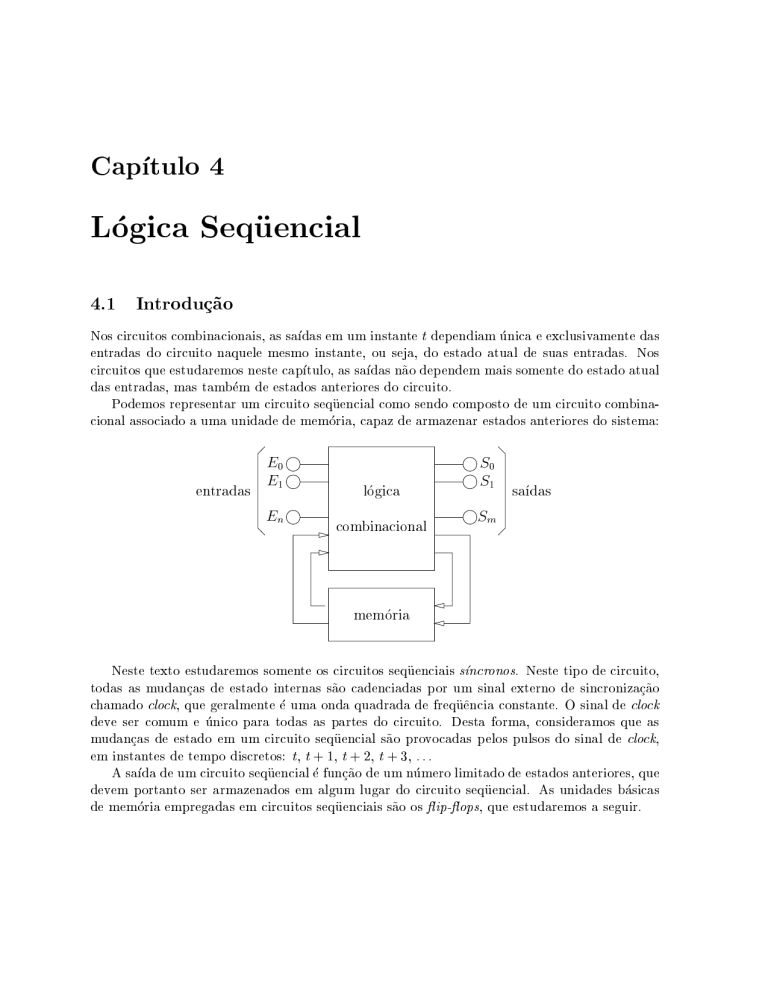

Podemos representar um circuito sequencial como sendo composto de um circuito combinacional associado a uma unidade de memoria, capaz de armazenar estados anteriores do sistema:

E0

E

entradas 1

En

logica

combinacional

S0

S1 sadas

Sm

memoria

Neste texto estudaremos somente os circuitos sequenciais sncronos. Neste tipo de circuito,

todas as mudancas de estado internas s~ao cadenciadas por um sinal externo de sincronizac~ao

chamado clock, que geralmente e uma onda quadrada de frequ^encia constante. O sinal de clock

deve ser comum e unico para todas as partes do circuito. Desta forma, consideramos que as

mudancas de estado em um circuito sequencial s~ao provocadas pelos pulsos do sinal de clock,

em instantes de tempo discretos: t, t + 1, t + 2, t + 3, . . .

A sada de um circuito sequencial e func~ao de um numero limitado de estados anteriores, que

devem portanto ser armazenados em algum lugar do circuito sequencial. As unidades basicas

de memoria empregadas em circuitos sequenciais s~ao os ip-ops, que estudaremos a seguir.

50

4.2 Flip-ops

Um ip-op (gangorra, em ingl^es) e um dispositivo que possui dois estados internos estaveis e

complementares, sendo por isso tambem chamado de biestavel. O estado interno de um ip-op

vale \0" ou \1", e pode permanecer indenidamente em um deles, em funca~o de suas entradas.

Desta forma, um ip-op pode armazenar 1 bit de informaca~o digital, e por isso constitui a

celula basica de memoria. Um ip-op normalmente apresenta um conjunto de entradas capaz

de alterar seu estado interno, e duas sadas apresentando respectivamente seu estado interno e

o complemento deste.

E1

entradas

Q

Flip-op

E2

Q

sadas

estado interno

Existem diversos tipos de ip-ops com comportamentos distintos, mas que podem ser transformados entre si. A seguir veremos os tipos mais conhecidos:

4.2.1 Flip-op RS (Reset-Set)

O ip-op de tipo RS (Reset-Set) e o mais simples desses dispositivos, e pode ser facilmente

construdo a partir de duas portas n~ao-E, como mostra a gura abaixo:

S

Q

R

Q

Mantendo as entradas R e S inativas (1), temos dois estados possveis de equilbrio para essa

estrutura, que podemos observar na gura abaixo:

S

1

1

1

1

0

1

R

1

1

0

0

Q

Q

S

1

1

0

0

1

0

R

1

1

1

1

Q

Q

51

A determinac~ao do estado das sadas de um ip-op RS em um instante futuro (Qt+1 e Qt+1 )

deve levar em conta suas entradas atuais Rt e S t e o estado interno atual Qt do mesmo:

S t Rt Qt Qt+1 Qt+1

1

2

3

4

5

6

7

8

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

1

1

1

0

0

0

1

1

1

0

0

1

1

1

0

Vamos analisar as situaco~es possveis para as entradas do ip-op:

Nas linhas 1 e 2, temos S t = Rt = 0, e por consequ^encia Qt+1 = Qt+1 = 1, o que

corresponde a uma situaca~o \proibida" no funcionamento normal do ip-op (as duas

sadas sempre devem ser complementares).

As linhas 3 e 4, nas quais S t = 0 e Rt = 1 correspondem a uma situac~ao de Set, ou seja,

impomos o valor \1" ao estado seguinte Qt+1 do ip-op, pouco importando seu estado

atual Qt .

As linhas 5 e 6, nas quais S t = 1 e Rt = 0 correspondem a uma situaca~o de Reset, ou seja,

impomos o valor \0" ao estado seguinte Qt+1 do ip-op, pouco importando seu estado

atual Qt .

Na situaca~o das linhas 7 e 8 temos S t = Rt = 1, e o ip-op armazena seu estado anterior:

Qt+1 = Qt .

Apos estas constatac~oes, a tabela anterior pode ser resumida assim:

S R Qt+1

0

0

1

1

0

1

0

1

proibido

1 (set)

0 (reset)

Qt (estado anterior)

A partir da tabela acima podemos construir o mapa de Karnaugh e obter a func~ao logica que

representa o comportamento do ip-op RS. Como os estados onde Rt = St = 0 s~ao proibidos,

vamos considerar a func~ao nestes pontos como sendo irrelevante (X). Obtemos o seguinte mapa,

e a func~ao logica associada:

Q RS

0

1

00 01 11 10

X 1

X 1 1

;!

Qt+1 = Rt + StQt

O ip-op RS tambem pode ser construdo a partir de portas n~ao-OU, apresentando um

comportamento similar:

52

S

Q

Q

R

Podemos modicar o ip-op RS para incluir uma entrada de controle, que pode servir por

exemplo para sincroniza-lo em relac~ao a um sinal de relogio externo (clock):

S

Q

clock

Q

R

Neste novo circuito as entradas R e S s~ao ditas sncronas em relac~ao ao sinal de clock Ck.

Temos ent~ao a seguinte tabela-verdade:

Ck S R Qt+1

0 X X Qt

1 0 0 Qt

1 0 1 0 (reset)

1 1 0 1 (set)

1 1 1 proibido

Podemos ainda acrescentar a estrutura do ip-op RS duas entradas do tipo clear e preset,

para alterar imediatamente o estado do ip-op sem necessidade das entradas R e S (ou seja,

de forma assncrona em relaca~o ao sinal de clock):

clear

S

Q

clock

Q

R

preset

53

Pela tabela verdade podemos observar que as entradas preset e clear n~ao podem operar

simultaneamente:

PS CLR Qt+1

0

0

1

1

0

1

0

1

proibido

1

0

operac~ao normal

4.2.2 Nveis e transi

c~oes

Os circuitos vistos ate o momento t^em entradas sensveis a nvel, cujo funcionamento e baseado

em nveis logicos constantes e bem denidos (0 ou 1). Este comportamento, desejavel em circuitos combinacionais, pode provocar problemas em circuitos sequenciais sncronos. Por exemplo,

o circuito do ip-op RS com entrada de sincronizac~ao (clock) vai estar ativo durante toda a

duraca~o de cada pulso de clock. Com isto, ele pode mudar de estado diversas vezes em cada

pulso de clock, caso as entradas mudem durante esse intervalo. Para contornar este problema

foram criadas as entradas sensveis a transica~o, que s~ao consideradas ativas somente durante as

transic~oes de nvel logico do sinal aplicado. Com isso uma entrada pode ser sensvel a quatro

diferentes tipos de excitaca~o:

Nvel logico alto: o sinal aplicado vale 1.

Nvel logico baixo: o sinal aplicado vale 0.

Transic~ao positiva: o sinal aplicado passa de 0 a 1.

Transic~ao negativa: o sinal aplicado passa de 1 a 0.

O sinal de clock e normalmente aplicado a entradas sensveis a transic~ao, positiva ou negativa.

Transico~es positivas e negativas s~ao representadas em tabelas-verdade respectivamente pelos

smbolos " e #. A gura abaixo indica os pontos de sensibilidade de uma entrada em relac~ao ao

sinal de clock, e indica os smbolos usados para representar cada tipo de entrada:

transic~ao positiva

nvel alto

nvel alto

nvel baixo

nvel baixo

clock

transic~ao negativa

4.2.3 Flip-op D (Data)

transica~o positiva

dispositivo

transica~o negativa

Neste tipo de ip-op a sada Q assume o valor de uma entrada de dados D sempre que for

habilitado pelo sinal de clock. Este tipo de dispositivo e bastante empregado na construc~ao de

registradores de deslocamento e no armazenamento de dados (buer). Sua representac~ao e sua

tabela-verdade s~ao as seguintes:

54

PS

D

CLR

Q

FF-D

clock

Q

Ck Dt Qt+1

0 X Qt

"

Dt Dt

1 X Qt

A partir da tabela podemos escrever que na transica~o Qt+1 = Dt .

4.2.4 Flip-op T (Toggle)

Neste tipo de ip-op a sada Q e invertida (toggled) quando a entrada T esta ativa e o sinal

de clock a habilitar. Este tipo de dispositivo e bastante empregado em contadores e divisores

de frequ^encia, pois seu comportamento permite a divis~ao por dois da frequ^encia do sinal de

entrada. Sua representac~ao e sua tabela-verdade s~ao as seguintes:

PS

T

clock

CLR

FF-T

Q

Q

Ck Tt Qt+1

0 X Qt

"

0 Qt

"

1 Qt

A partir da tabela podemos escrever que na transica~o Qt+1 = T t Qt + Tt Qt = Tt Qt . Para

compreender melhor o funcionamento deste tipo de ip-op, vamos observar seu comportamento

temporal:

55

clock

T

Q

t

Durante o perodo em que T = 1, a cada transic~ao positiva do clock o nvel da sada Q e

invertido. Com isso, o sinal da sada tem a metade da frequ^encia do sinal de clock.

4.2.5 Flip-op JK

O ip-op de tipo JK apresenta um comportamento misto entre os ip-ops RS e T. Ele possui

duas entradas J e K (que equivalem respectivamente as entradas S e R dos ip-ops RS) e uma

entrada de clock. Para os estados normais, o comportamento e o mesmo do ip-op RS, mas

quando J = K = 1 (denido como estado proibido no ip-op RS), a sada e complementada,

como ocorre no ip-op T. Com isso, podemos denir a seguinte representaca~o e tabela-verdade

para o ip-op JK:

PS

CLR

J

K

FF-JK

clock

Ck Jt Kt Qt+1

0 X X Qt

"

0 0 Qt

Q

Q

0 1

0

1 0

1

1 1 Qt

O ip-op JK e bastante popular, pois a partir dele podemos obter os demais ip-ops sem

necessidade de circuitos adicionais, como veremos na sec~ao 4.2.7.

A equac~ao de estado do ip-op JK pode ser obtida a partir de seu mapa de Karnaugh:

Q J K 00 01 11 10

0

1 1 ;! Qt+1 = Jt Qt + K t Qt

1

1

1

"

"

"

56

4.2.6 Flip-op mestre-escravo

Antes da disponibilidade de ip-ops com entradas sensveis a transica~o, uma estrutura especial

denominada ip-op mestre-escravo era usada para isolar as entradas instaveis e sincronizar o

sistema em relaca~o ao clock. O circuito normalmente usado para implementar ip-ops mestreescravo e composto por dois ip-ops RS em cascata, e pode ser visto na gura a seguir:

mestre

escravo

Qm

Sm

Rm

Qm

Qs

Qs

clock

Vamos analisar o que ocorre em um ip-op mestre-escravo em um pulso completo de clock.

No incio, com a descida do sinal de clock no escravo, este e desconectado do mestre. Ao nal da

subida, as entradas do mestre s~ao habilitadas e este comeca a atualizar seu estado interno em

funca~o as entradas. O mestre permanece assim ate o incio da descida do pulso de clock, quando

suas entradas s~ao desabilitadas, e ao nal da descida seu estado e transferido ao escravo. Com

isso, a sada do ip-op escravo e completamente isolada de eventuais oscilac~oes nas entradas

Sm e Rm. A gura a seguir ilustra esse comportamento.

registra entrada do mestre

desabilita entradas do mestre

clock

t

isola mestre do escravo

transfere estado ao escravo

O ip-op de tipo mestre-escravo caiu em desuso com o surgimento de entradas sensveis a

transic~ao, sendo raramente usado hoje em dia.

4.2.7 Convers~ao entre ip-ops

Os ip-ops apresentados t^em comportamentos similares, e podem ser facilmente convertidos

entre si, atraves de conex~oes simples e do uso de algumas portas adicionais. Vejamos alguns

exemplos:

Convers~ao de ip-op JK em ip-op D:

57

D

J

K

Q

FF-JK

Q

clock

Convers~ao de ip-op JK em ip-op T:

T

J

K

Q

FF-JK

Q

clock

Convers~ao de ip-op RS em ip-op T:

R

T

Q

FF-RS

clock

Q

S

Convers~ao de ip-op RS em ip-op JK:

K

R

FF-RS

clock

J

S

Q

Q

Convers~ao de ip-op D em ip-op T:

T

clock

D

Q

FF-D

Q

58

4.2.8 Par^ametros operacionais

Para a operac~ao correta dos ip-ops alguns par^ametros devem ser respeitados, sobretudo no que

diz respeito as caractersticas temporais dos sinais de entrada. Os par^ametros mais importantes

s~ao:

Frequ^encia maxima fmax : e a maxima frequ^encia admitida para o sinal de clock, ou seja, a

maxima frequ^encia de operac~ao do dispositivo.

Tempo de setup tsetup: e o tempo mnimo de presenca do sinal em uma entrada de dados

antes da ocorr^encia do pulso de clock.

Tempo de perman^encia thold: e o tempo mnimo que o sinal deve permanecer em uma entrada de dados apos a transic~ao do clock.

Tempo de preset tpreset: e o tempo mnimo que uma entrada do tipo preset ou clear precisa

estar ativa para efetuar sua func~ao.

Largura de pulso tw : e o tempo mnimo que o clock precisa permanecer em um nvel alto

(caso a porta seja sensvel a ") ou baixo (caso a porta seja sensvel a #) para que possa ser

conavel.

A gura abaixo ilustra esses par^ametros, que s~ao fortemente dependentes da tecnologia

empregada para a construc~ao do dispositivo. Alguns destes valores ser~ao revistos no captulo ??,

mas os manuais de dados tecnicos dos dispositivos (Data Sheets dos fabricantes) os apresentam

em detalhe.

tsetup thold

D

Clock

CLR

tw

tpreset

Q

4.3 Diagramas de estado

Podemos representar o comportamento de um circuito sequencial atraves de equac~oes logicas

ou de tabelas-verdade. Essa forma de representac~ao somente e viavel para circuitos simples,

contendo apenas um ip-op. Quando a complexidade do circuito aumenta, torna-se necessario

empregar outras formas de representaca~o para denir seu comportamento de maneira el e sem

inconsist^encias ou ambiguidades. Uma ferramenta muito util para a representaca~o do comportamento de circuitos sequenciais complexos e o diagrama de estados, tambem chamado aut^omato

nito, que veremos nesta sec~ao.

59

4.3.1 Estrutura basica

Um diagrama de estados e uma construc~ao graca composta por um conjunto de estados (indicados por crculos) e de transico~es (indicados por arcos com setas). Os estados representam todas

as situac~oes possveis para o sistema, e as transico~es indicam as mudancas de estado possveis,

e em que condic~oes elas s~ao provocadas (os valores das entradas que as provocam). O estado

inicial do sistema e indicado por um crculo duplo.

Vejamos por exemplo o diagrama de estados de um semaforo, indicado na gura a seguir.

Esse diagrama possui os estados verde (estado inicial), amarelo, vermelho e parado. As transico~es

entre estados est~ao indicadas pelas setas, com os nomes dos eventos que as provocam.

avancar

avancar

vermelho

verde

conserto

problema

avancar

amarelo

problema

problema

parado

No caso especco dos circuitos sequenciais sncronos, o diagrama de estados possui algumas

caractersticas importantes que devem ser levadas em conta em sua interpretaca~o. A primeira e

o seu aspecto sncrono: o diagrama deve indicar as mudancas possveis no sistema no proximo

proximo pulso de clock, em func~ao do valor das entradas do circuito naquele momento.

Outra caracterstica diz respeito a nomeaca~o dos arcos que representam as transico~es: um

determinado arco leva de um estado atual ao seu proximo estado, e seu rotulo indica a combinac~ao de entrada que ativa aquela transic~ao e o valor de sada que ela ira provocar. A gura

abaixo ilustra esse funcionamento:

estado atual

A

proximo estado

B

01

1

entrada

sada

A interpretaca~o da transic~ao acima e a seguinte: no proximo pulso de clock, se o sistema

estiver no estado interno A e ocorrer a entrada 01, ent~ao o sistema passara ao estado B e a sada

passara a valer 1.

4.3.2 Um exemplo: o somador serial

Vamos usar o diagrama de estados para representar o comportamento de um circuito um pouco

mais complexo: um somador completo serial. Este circuito tem duas entradas At e Bt que

60

recebem os dois dgitos binarios a somar, e uma sada St , que apresenta a soma obtida. Alem

disso, o circuito armazena o excesso Ct;1 (carry) da soma anterior e considera esse valor na soma

atual. Desta forma, podemos somar numeros binarios longos, processando um bit por pulso de

clock.

00110110010111

01011101110011

At

P

St

10010100001010

Bt

clock

A partir das entradas At e Bt e do excesso da ultima soma Ct;1 podemos construir a seguinte

tabela-verdade para a soma atual St e seu excesso Ct :

Ct;1 At Bt St Ct

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

O valor a ser memorizado e o ultimo excesso, que constitui portanto o estado interno do

sistema. Com isso podemos deduzir que o sistema possui dois estados internos: um quando

Ct;1 = 0, que chamaremos q0, e outro quando Ct;1 = 1, que chamaremos q1 . Podemos ent~ao

construir o diagrama de estados que representa seu comportamento, considerando como entradas

o par At Bt e como sada a soma St :

00

0

01

1

11

0

q0

10

1

01

0

q1

00

1

10

0

11

1

O diagrama acima permite representar de forma sucinta e sem ambiguidades o comportamento esperado para o somador serial. Esses diagramas ser~ao de suma import^ancia para a

analise e projeto de circuitos sequenciais sncronos, por isso sua estrutura deve ser perfeitamente

compreendida.

61

4.3.3 Tabelas de estados

Uma forma alternativa de representac~ao do comportamento de um circuito sequencial e sob

a forma de uma tabela, que indica para cada estado e para cada combinac~ao das entradas, o

proximo estado e o valor da sada (sob a forma de fraca~o). Para o somador serial podemos

construir a seguinte tabela de estados (que pode ser obtida da tabela-verdade ou do diagrama

de estados):

q AB

q0

q1

00 01 10 11

q0

0

q0

1

q0

1

q1

0

q0

1

q1

0

q1

0

q1

1

O diagrama de estados e a tabela de estados contem exatamente a mesma informac~ao e por

isso s~ao equivalentes.

4.3.4 Diagramas de estado dos ip-ops

Podemos construir os diagramas de estado dos ip-ops a partir das tabelas-verdade e das

equac~oes logicas vistas ate o momento para os mesmos. O diagrama de estado de um ip-op

e bastante simples, porque a sada se confunde com o proximo estado interno do sistema (Q e

ao mesmo tempo sada e estado). Vejamos como cam os diagramas de estado dos principais

ip-ops:

Flip-

op RS: Considerando como entrada o par R S e como sada Q:

11

0

01

0

10

1

q0

00

?

11

1

q1

01

0

10

1

00

?

Flip-

op D: Considerando como entrada D e como sada Q:

1

1

0

0

q0

q1

0

0

Flip-

op T: Considerando como entrada T e como sada Q:

1

1

62

1

1

q1

q0

0

0

0

1

1

0

Flip-

op JK: considerando como entrada o par JK e como sada Q:

01

0

00

1

11

1

10

1

q0

q1

11

0

01

0

00

0

10

1

4.4 An

alise de circuitos sequenciais s

ncronos

O comportamento de um circuito sequencial e denido por uma sequ^encia de estados que evolui

em func~ao de seu estado atual e das entradas do circuito essa evoluc~ao e cadenciada por um

sinal de clock. A partir das denico~es apresentadas no incio deste captulo, podemos propor a

seguinte estrutura generica para um circuito sequencial sncrono:

entradas

E0

E1

logica

En

Y1

Yr

ip-op

ip-op

...

ip-op

sadas

Sm

combinacional

Y0

estado

atual

S0

S1

X0

X1

Xr

excitaca~o

dos

ip-ops

clock

Na estrutura acima, a parte combinacional fornece as sadas S do circuito e os sinais de

controle X que ir~ao excitar os ip-ops, ambos em func~ao de suas entradas E e de seu estado

63

atual Y . Os ip-ops armazenam o estado Y do sistema, cuja evoluc~ao e cadenciada pelo sinal

de clock.

4.4.1 Objetivo

As relac~oes entre entradas, estado atual, sadas e proximo estado podem ser completamente

especicadas atraves de um diagrama de estados, como vimos na sec~ao 4.3. O objetivo principal

da analise de um circuito sequencial sncrono e a obtenca~o de um diagrama de estados indicando

seu comportamento, e o estudo deste para a compreens~ao do funcionamento do circuito. Para a

analise de um circuito devem ser efetuados os seguintes passos:

1. Identicar as variaveis (sinais) de entrada, de sada, de controle dos ip-ops (excitac~ao)

e de estado.

2. Obter as equaco~es relativas a parte combinacional do circuito, atraves das tecnicas ja

estudadas no captulo 3:

Si (t) =

Xk (t) =

F (E0 (t) : : : En (t) Yo (t) : : : Yr (t))

G (E0 (t) : : : En (t) Yo (t) : : : Yr (t))

3. Escrever as equac~oes de proximo estado de cada ip-op, em func~ao do tipo de ip-op,

de seu estado atual e das entradas de controle Xi :

Yi(t + 1) =

H(Yi (t) Xi (t))

4. Montar uma tabela-verdade relacionando cada uma das entradas E (t), sadas S (t), estados

X (t) e proximos estados X (t + 1), com a seguinte forma:

E0 (t) . . . En (t) X0 (t) . . . Xr (t) S0 (t) . . . Sm (t) X0 (t + 1) . . . Xr (t + 1)

0

...

...

...

0

...

0

...

...

...

0

...

0

...

...

...

0

...

0

...

...

...

0

...

5. A partir da tabela, construir o diagrama de estados do circuito.

A seguir veremos como a tecnica de analise e aplicada, atraves do estudo de dois exemplos.

4.4.2 Um exemplo

Vamos analisar o circuito da gura a seguir, para obter seu diagrama de estados:

1

J1

K1

clock

FF1

Q1

J2

K2

FF2

Q2

J3

K3

FF3

Q3

S

64

O circuito pode ser redesenhado para colocar em evid^encia a separac~ao existente entre suas

partes combinacional e sequencial (o sinal de clock dos ip-ops ca subentendido):

S

Q1

Q2

Q3

FF1

FF2

FF3

J1

K1

1

J2

K2

J3

K3

Nosso primeiro passo na analise consiste em identicar todas as variaveis envolvidas:

Vari

aveis de entrada: nenhuma

Vari

aveis de sada: S

Vari

aveis de controle: J1 K1 J2 K2 J3 K3

Vari

aveis de estado: Q1 Q2 Q3

A seguir vamos identicar e renar as equac~oes:

Sada:

S (t) = Q3 (t)

Controle:

J1 (t) = K1 (t) = 1

J2 (t) = K2 (t) = Q1 (t)

J3 (t) = K3 (t) = Q1 (t)Q2 (t)

65

Proximo estado:

Q1 (t + 1) = J1 (t)Q1 (t) + K 1 (t)Q1 (t)

= 1Q1 (t) + 0Q1 (t)

= Q1 (t)

Q2(t + 1) = J2 (t)Q2 (t) + K 2 (t)Q2 (t)

= Q1 (t)Q2 (t) + Q1 (t)Q2 (t)

= Q1 (t) Q2 (t)

Q3 (t + 1) = J3 (t)Q3 (t) + K 3 (t)Q3 (t)

= Q1 (t)Q2 (t)Q3 (t) + (Q1 (t)Q2 (t))Q3 (t)

= (Q1 (t)Q2 (t)) Q3 (t)

A partir desses dados podemos construir a tabela-verdade para esse circuito. Para sua

construc~ao, devem ser enumeradas todas as combinaco~es possveis para as entradas E (t) e estados

dos ip-ops Q(t). A partir desses dados e das equaco~es obtidas, podem ser determinadas as

sadas do sistema S (t) e os estados futuros dos ip-ops Q(t + 1). Deve-se observar que cada

combinaca~o de estados dos ip-ops corresponde a um estado interno qi diferente para o sistema.

Entradas

|

|

|

|

|

|

|

|

|

n

o

q0

q1

q2

q3

q4

q5

q6

q7

Estado atual

Sadas

Proximo estado

Q1(t) Q2 (t) Q3 (t) S (t) Q1 (t + 1) Q2 (t + 1) Q3 (t + 1)

0

0

0

0

1

0

0

0

0

1

1

1

0

1

0

1

0

0

1

1

0

0

1

1

1

1

1

1

1

0

0

0

0

1

0

1

0

1

1

0

1

1

1

1

0

0

0

0

1

1

1

1

1

0

0

0

no

q4

q5

q6

q7

q2

q3

q1

q0

A partir da tabela-verdade obtida podemos montar o diagrama de estados do circuito, que

representa seu comportamento temporal:

;

0

q0

q4

;

0

q2

;

0

;

;

1

q7

q6

0

;

1

q3

;

1

q5

;

1

q1

66

O diagrama de estados do circuito permite observar facilmente que a sequ^encia de valores da sada do circuito sera composta alternadamente por quatro \0" e quatro \1":

000011110000111100001111. . .

4.4.3 Outro exemplo

Vamos analisar o circuito da gura a seguir, para obter seu diagrama de estados:

X

Z

Q1

Q2

Q2

FF1

FF2

D1

D2

Primeiramente vamos identicar todas as variaveis envolvidas:

Variaveis de entrada: X

Variaveis de sada: Z

Variaveis de controle: D1 D2

Variaveis de estado: Q1 Q2

A seguir vamos identicar e renar as equac~oes:

Sada:

Z (t) = X (t) + Q2 (t)

Controle:

D1 (t) = Q1 (t) + Q2 (t)

D2 (t) = X (t)Q1 (t)

67

Proximo estado:

Q1 (t + 1) = D1 (t)

= Q1 (t) + Q2 (t)

Q2 (t + 1) = D2 (t)

= X (t)Q1 (t)

A partir desses dados podemos construir a tabela-verdade para esse circuito:

Entradas

X (t)

0

0

0

0

1

1

1

1

Estado atual

Sadas

Proximo estado

n Q1 (t) Q2 (t) Z (t) Q1 (t + 1) Q2 (t + 1)

q0 0

0

0

1

0

q1 0

1

1

0

0

q2 1

0

0

1

0

q3 1

1

1

1

0

q0 0

0

1

1

0

q1 0

1

1

0

0

q2 1

0

1

1

1

q3 1

1

1

1

1

o

no

q2

q0

q2

q2

q2

q0

q3

q3

Finalmente podemos montar o diagrama de estados do circuito:

q1

01

1

1

1

q0

1

1

q2

q3

0

1

0

0

0

0

1

1

Como vimos anteriormente, podemos tambem representar o diagrama de estados na forma

de uma tabela de estados:

estado

entradas

atual X (t) = 0 X (t) = 1

q0

q1

q2

q3

q2

0

q0

1

q2

0

q2

1

q2

1

q0

1

q3

1

q3

1

4.5 Projeto de circuitos sequenciais s

ncronos

O projeto de circuitos sequenciais sncronos segue uma abordagem analoga a utilizada no processo de analise, mas em sentido inverso. Desta forma, o projeto pode ser decomposto nos seguintes

passos:

68

1. Descrica~o completa da operaca~o desejada para o circuito, envolvendo:

identicaca~o das entradas e sadas

identicaca~o dos estados internos (n ip-ops para 2n estados)

denic~ao do comportamento desejado, atraves de um diagrama de estados.

2. Determinac~ao da tabela-verdade para o circuito, com base nos valores possveis para as

entradas e estados internos do circuito. Esta tabela tambem devera conter colunas para

os sinais de excitac~ao dos ip-ops, em func~ao do tipo de ip-op escolhido.

3. Minimizac~ao das func~oes correspondentes a parte combinacional do circuito, ou seja, sadas

e controles dos ip-ops.

4. Construc~ao do circuito nal.

Para a determinac~ao da tabela-verdade teremos de empregar \tabelas de excitac~ao" para os

ip-ops, que permitem determinar os valores das entradas de controle em funca~o da transic~ao

de estado desejada. Essas tabelas podem ser facilmente deduzidas a partir das tabelas-verdade

dos ip-ops. Por exemplo, para o ip-op JK temos:

Qt Jt Kt Qt+1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

1

1

1

0

1

0

Qt Qt+1 Jt Kt

;!

0

0

1

1

0

1

0

1

0 X

1 X

X 1

X 0

De maneira similar podemos obter a tabela de excitaca~o para o ip-op D:

Qt Dt Qt+1

0

0

1

1

0

1

0

1

0

1

0

1

Qt Qt+1 Dt

;!

0

0

1

1

0

1

0

1

0

1

0

1

4.5.1 Um exemplo

Neste exemplo vamos projetar um circuito para implementar o somador serial cujo comportamento foi apresentado na sec~ao 4.3.2. Nosso primeiro passo e determinar a operaca~o desejada

para o circuito, e para isso vamos determinar os seguintes dados:

Entradas: os bits a somar: A(t) e B (t)

Sada: a soma acumulada: S (t)

Estados internos: dois estados, indicando o excesso da ultima operaca~o efetuada: sem

carry (q0 ) e com carry (q1 ).

69

Comportamento: indicado no diagrama de estados apresentado na sec~ao 4.3.2.

Como temos dois estados internos, precisaremos de apenas uma variavel de estado Q(t) e

por consequ^encia apenas um ip-op.

Neste ponto podemos montar a tabela-verdade do circuito. Ja conhecemos At , Bt , St , Qt

e Qt+1 , apresentados no diagrama de estados. Devemos ent~ao escolher um tipo de ip-op

para a implementac~ao e obter as colunas correspondentes a sua excitaca~o. Essas colunas ser~ao

determinadas a partir de cada par \estado atual ! estado futuro" para cada ip-op, usando

a tabela de excitac~ao do ip-op escolhido. Escolhendo um ip-op JK ou D, nossa tabela de

estados assume a seguinte forma:

entradas estado atual sadas proximo estado excitac~ao dos ip-ops

At Bt

0

0

1

1

0

0

1

1

Qt

0

1

0

1

0

1

0

1

St

0

0

0

0

1

1

1

1

0

1

1

0

1

0

0

1

Qt+1

Jt Kt

0

0

0

1

0

1

1

1

0

0

0

1

X

X

X

X

X

X

X

X

1

0

0

0

Dt

0

0

0

1

0

1

1

1

Com a tabela construida, podemos passar a determinac~ao das func~oes combinacionais necessarias a gerac~ao da sada e das excitac~oes do ip-op. Para St podemos construir o seguinte

mapa de Karnaugh:

Q AB

00 01 11 10

1

1

1

1

0

1

;!

St = At Bt Qt

Para Jt temos:

Q AB

0

1

00 01 11 10

1

X X X X

;!

Jt = At Bt

Para Kt temos:

Q AB

0

1

00 01 11 10

X X X X

1

;!

Kt = At B t = At + Bt

A partir das funco~es mnimas obtidas podemos sintetizar a parte combinacional do circuito,

que acoplada ao ip-op nos dara o circuito nal:

70

At

Bt

St

Q FF

J

K

clock

O circuito acima pode ser apresentado de uma forma mais agradavel e intuitiva:

At

Bt

St

J

K

FF Q

clock

4.5.2 Outro exemplo

Vamos construir um circuito para implementar o comportamento descrito atraves do seguinte

diagrama de estados:

q1

1

0

0

0

q0

0

0

0

0

1

0

q2

1

1

Nosso primeiro passo e determinar a operaca~o desejada para o circuito, e para tal vamos

determinar os seguintes dados:

71

Entrada: uma entrada, que chamaremos Et

Sada: uma sada, que chamaremos St

Estados internos: o sistema possui tr^es estados (q0 , q1 e q2 ), o que nos leva a um mnimo

de dois ip-ops e portanto duas variaveis de estado Q1t e Q2t , cuja combinac~ao nos

permitira a indicac~ao do estado do sistema:

Q1t Q2t

0

0

1

1

estado

q0

q1

q2

0

1

0

1

sem uso

Comportamento: indicado no diagrama de estados apresentado acima.

Neste ponto podemos montar a tabela-verdade do circuito. Ja conhecemos Et , St , Q1t , Q2t ,

Q1t+1 e Q2t+1 , apresentados no diagrama de estados. Escolhendo um ip-op JK, devemos

ent~ao determinar J 1t , K 1t , J 2t e K 2t :

entrada

Et

0

0

0

0

1

1

1

1

estado atual sada

no Q1t Q2t St

q0 0

0

0

q1 0

1

0

q2 1

0

0

| 1

1

X

q0 0

0

0

q1 0

1

0

q2 1

0

1

| 1

1

X

proximo estado excitac~ao dos ip-ops

no Q1t+1 Q2t+1 J 1t K 1t J 2t K 2t

q0

0

0

0 X

0

X

q0

0

0

0 X X

1

q0

0

0

X 1

0

X

| X

X

X X X X

q1

0

1

0 X

1

X

q2

1

0

1 X X

1

q2

1

0

X 0

0

X

| X

X

X X X X

Com a tabela assim construida, podemos passar a determinaca~o das func~oes combinacionais

necessarias a geraca~o da sada e das excitaco~es dos ip-ops, em func~ao da entrada Et e dos

estados Q1t e Q2t . Para St podemos construir o seguinte mapa de Karnaugh:

Et Q1 Q2 00 01 11 10

0

1

X

X

1

;!

St = Et Q1t

;!

J 1t = Et Q2t

Para as excitac~oes J 1t , K 1t , J 2t e K 2t temos:

Et Q1 Q2 00 01 11 10

0

1

1

X X

X X

Et Q1 Q2 00 01 11 10

0

1

X X X

X X X

1

;!

K 1t = E t

72

Et Q1 Q2 00 01 11 10

0

1

X X

X X

1

;!

Et Q1 Q2 00 01 11 10

0

1

X

X

1

1

X X

X X

;!

J 2t = Et Q1t

K 2t = 1

A partir das funco~es mnimas obtidas podemos sintetizar a parte combinacional do circuito,

que acoplada aos ip-ops nos dara o circuito nal:

Et

St

Q1

Q1

Q2

Q2

FF1

FF2

J1

K1

J2

K2

1

4.6 Principais circuitos sequenciais s

ncronos

Nesta sec~ao veremos alguns circuitos sequenciais sncronos de uso bastante frequente, e portanto

facilmente encontrados na forma de chips completos. Esses circuitos podem tambem ser sintetizados atraves da tecnica de projeto vista na seca~o anterior. Abordaremos aqui os registradores

de deslocamento e os contadores.

4.6.1 Registradores de deslocamento

Um registrador de deslocamento e um arranjo linear de n ip-ops capaz de armazenar n bits

de informac~ao. A cada pulso de clock os dados podem ser deslocados uma posica~o para a

direita ou para a esquerda, de acordo com a implementac~ao do registrador, o que justica o

nome desse dispositivo. Os dados podem ser carregados no registrador de forma paralela (todos

simultaneamente, atraves de entradas especiais) ou sequencial, atraves de um dos extremos do

73

registrador e fazendo uso do mecanismo de deslocamento de bits. A gura a seguir mostra

o diagrama simplicado de um registrador de deslocamento para a direita com 8 bits (foram

omitidos o sinal de clock e as entradas de controle):

entrada paralela

E0 E1 E2 E3 E4 E5 E6 E7

Es

Ss

entrada

serial

sada

serial

S0 S1 S2 S3 S4 S5 S6 S7

sada paralela

As duas setas indicam os sentidos possveis do uxo de dados no interior do registrador de

deslocamento:

uxo sequencial: os dados uem para a direita na cad^encia do clock. O primeiro ipop assume o valor da entrada serial Es , e o dado do outro extremo, que ja atravessou o

registrador, e apresentado na sada serial Ss. Portanto, a cada pulso de clock o dado mais

antigo (a direita) e descartado e um novo dado entra no registrador (a esquerda). Desta

forma, um dado demora n pulsos de clock para atravessar um registrador de deslocamento

de n bits.

uxo paralelo: o conteudo do registrador pode ser acessado atraves das sadas paralelas,

e pode ser totalmente alterado fazendo-se uso das entradas paralelas. Essas operaco~es

normalmente podem ser efetuadas de maneira assncrona.

Podemos compreender melhor o funcionamento de um registrador de deslocamento analisando seu comportamento temporal. O diagrama de tempo a seguir mostra o comportamento de

um registrador de deslocamento de 4 bits com o conteudo inicial 1000 (apenas um bit ativo no

primeiro registro), e com Es = 0:

clock

S0

S1

S2

S3

Segundo a maneira como a informac~ao ui no interior de um registrador de deslocamento,

podemos classica-lo em quatro grupos:

74

Serie-serie: como cada bit demora n pulsos de clock para atravessar o registrador, este

dispositivo e usado em linhas de retardo digitais, para criar atrasos no sinal digital (por

exemplo, em c^amaras de eco digitais podem ser usados registradores com milhares de bits).

Serie-paralelo: os dados s~ao carregados em serie e retirados atraves da sada paralela.

Esta estrutura e normalmente usada para em comunicaca~o de dados, para converter sinais

seriais (na linha telef^onica) em sinais paralelos (no interior do computador).

Paralelo-serie: exerce a funca~o inversa do anterior, sendo por isso tambem empregado em

comunicac~ao de dados.

Paralelo-paralelo: a carga e descarga do registrador e feita atraves das portas paralelas.

Pode ser usado para deslocar (shift) valores binarios, ou para armazena-los temporariamente (bu er).

Veremos a seguir algumas estruturas simples para a implementac~ao dos registradores de

deslocamento. Empregamos ip-ops de tipo D por serem os que melhor se enquadram neste

tipo de aplicac~ao, e por sua simplicidade. Para construir um registrador de deslocamento serieserie, basta acoplarmos ip-ops tipo D em serie:

Es

clock

D FF Q

D FF Q

D FF Q

D FF Q

Ss

O registrador serie-paralelo tem uma implementaca~o similar, bastando extrair a sada individual de cada ip-op para compor a sada paralela. Para construir os registradores paralelo-serie

e paralelo-paralelo, usamos as entradas preset e clear de cada ip-op para carregar o registrador

com os valores presentes na entrada paralela:

E0

E1

E2

En

pr clr

D FF Q

pr clr

D FF Q

pr clr

D FF Q

pr clr

D FF Q

carregar

Es

clock

Ss

75

Podemos tambem construir um registrador bidirecional, cujo sentido de deslocamento (da

esquerda para a direita ou vice-versa) e estabelecido atraves de uma porta de controle M :

M = 1: esquerda ! direita: Eed ! FF1 ! FF2 ! FF3 ! FF4 ! Sed

M = 0: direita ! esquerda: Ede ! FF4 ! FF3 ! FF2 ! FF1 ! Sde

M

M

Sde

Ede

Eed

Sed

clock

1

D

Q

2

D

Q

3

D

Q

4

D

Q

4.6.2 Contadores

Contadores s~ao circuitos sequenciais que permitem contar pulsos de uma entrada, apresentando

a contagem sob a forma de um numero binario, em uma sada com n bits. Os contadores t^em

muitas aplicac~oes, dentre as quais a contagem de eventos, a divis~ao de frequ^encia, o sequenciamento de operaco~es, etc.

Podemos classicar os contadores segundo diversos par^ametros:

Sincronismo: um contador pode ser sncrono, quando todos os seus ip-ops est~ao sob o

comando de um mesmo clock, ou assncronos, quando os ip-ops podem ser excitados

por clocks distintos.

Sentido: um contador pode contar de forma ascendente ou descendente, ou ambos.

Programaca~o: um contador pode efetuar uma contagem entre dois extremos xos, ou

podemos estabelecer os valores inicial e nal para a contagem.

O contador de implementac~ao mais simples e o assncrono ascendente, que pode ser facilmente

obtido atraves da associac~ao de ip-ops tipo T em cascata:

76

1

T Q

T Q

T Q

T Q

Q

Q

Q

Q

FF

FF

clock

Q0

FF

Q1

FF

Q2

Q3

O circuito acima permite contar 16 passos, de 00002 a 11112 , em sentido ascendente, como

mostra o diagrama temporal a seguir:

clock

Q0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

Q1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

Q2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

Q3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

Caso seja necessaria uma contagem com sada sequencial, podemos associar a saida do

contador um decodicador 4 16, e assim teremos na sada do decodicador uma sequ^encia

S0 ! S1 ! S2 ! ! S15 que evolui a cada pulso do clock. Tambem podemos ver o circuito

anterior como um divisor de frequ^encia: para um sinal de clock de frequ^encia fc, a sada Q0 tem

frequ^encia fc=2, a sada Q1 tem frequ^encia fc=4 e assim por diante.

Para a construca~o de um contador assncrono descendente basta usar as sadas Q para

associar os ip-ops. O contador da gura a seguir efetua o ciclo 0000 ! 1111 ! 1110 !

1101 ! 1100 ! ! 0000:

1

clock

T Q

T Q

T Q

T Q

Q

Q

Q

Q

FF

FF

Q0

FF

Q1

FF

Q2

Q3

77

Podemos associar os dois circuitos e obter um contador ascendente-descendente, sob o comando de uma porta de controle M : caso M = 1 teremos uma contagem ascendente, e caso

M = 0 ela sera descendente:

M

1

T Q

T Q

Q

Q

FF

FF

O projeto de contadores sncronos pode ser feito facilmente atraves da tecnica de projeto

descrita neste captulo. Duas estruturas de contadores sncronos s~ao bastante conhecidas: o

contador sncrono com transporte serie ou com transporte paralelo. Estes nomes indicam a

forma como a evoluc~ao dos bits menos signicativos do contador s~ao consideradas na evoluc~ao

dos bits mais signicativos. Ambas as estruturas s~ao apresentadas a seguir (para 4 bits):

1

FF

FF

T Q

FF

T Q

FF

T Q

T Q

clock

Q0

1

FF

Q1

FF

T Q

Q2

FF

T Q

Q3

FF

T Q

T Q

clock

Q0

Q1

Q2

Q3

78

Para a construc~ao de contadores sncronos decrescentes ou bidirecionais podem ser seguidos

os mesmos procedimentos apresentados para os contadores assncronos, ou seja, usar Q ao inves

de Q ou associar uma logica de controle para selecionar entre Q e Q.

Os contadores vistos ate o momento permitem contar M = 2n passos, onde n e o numero

de ip-ops usados. Podemos no entanto construir contadores para operar com um valor M

qualquer, que chamaremos contadores em modulo M. Por exemplo, um contador em modulo 5

permite contar 5 passos, percorrendo o ciclo 000 ! 001 ! 010 ! 011 ! 100 ! 000 ! .

O primeiro passo para a construc~ao de um contador em modulo M e a determinac~ao do

numero de ip-ops necessarios para a contagem. Isso pode ser feito com base no numero de

dgitos binarios necessarios para representar os estados do contador. Por exemplo, um contador

em modulo 6 (610 = 1102 ) ira precisar de 3 ip-ops, enquanto um contador em modulo 26 ira

necessitar de 5 ip-ops (pois 2610 = 110102 ).

A seguir deve-se construir um contador assncrono usando os ip-ops necessarios. Para

obter a contagem ate M , deve-se conectar todas as sadas ativas no estado M a uma porta AND

que ira ativar as entradas clr de todos os ip-ops. Assim, quando a contagem atingir M , a

porta AND sera ativada e os ip-ops voltar~ao a zero, reiniciando a contagem. O circuito a

seguir usa essa tecnica para implementar um contador em modulo 26 (ou seja, que vai de 0 a

25):

1

clock

T Q

T Q

T Q

T Q

clr

clr

clr

clr

FF

FF

Q0

FF

Q1

T Q

FF

Q2

FF

clr

Q3

Q4

4.7 Exerc

cios

1. Projete um registrador em anel de 3 bits, com deslocamento para a direita. Qualquer que

seja o valor inicial, o valor de cada bit e deslocado para a direita, e o ultimo a direita passa

a ser o primeiro a esquerda. O bit da esquerda e o mais signicativo. Use ip-ops de tipo

D.

2. Projete um contador de 3 bits com clear, usando ip-ops de tipo T.

3. Projete um contador crescente-decrescente de 2 bits em codigo Gray. Se a entrada U = 1

o contador e crescente, e sen~ao e decrescente. Esse tipo de contador e usado para controlar

motores de passo bidirecionais.

4. Projete um contador programavel obedecendo as caractersticas da tabela a seguir, usando

ip-ops de tipo JK:

79

entradas modo de

operac~ao

0 0 n~ao muda

0 1 modulo 3

1 0 modulo 5

1 1 modulo 7

x1 x2

5. Considere um somador paralelo de 4 bits, no qual X e o sinal de controle, e A e B s~ao

os registradores de 4 bits. Se X = 0 nenhuma operaca~o e efetuada, mas se X = 1 e

realizada a soma dos registradores A e B , e o resultado e depositado no registrador A.

Projete o circuito do somador, considerando que o mesmo pode ser decomposto em celulas

somadoras de 1 bit (o excesso ou carry de cada estagio deve servir como entrada para o

estagio seguinte).

6. Construa o diagrama de estados do gerador pseudo-aleatorio de rudo cujo circuito e apresentado a seguir:

output

D Q

D Q

FF

FF

D Q

D Q

FF

FF

clock

7. Projete um circuito detector de paridade par serial para palavras de 8 bits, usando ipops de tipo D, e responda: a) quantos pulsos de relogio s~ao necessarios para detectar a

paridade de uma palavra b) compare o circuito obtido com o detector de paridade paralelo

apresentado na sec~ao 3.6.

8. Obtenha o diagrama de estados do circuito a seguir:

1

J Q

J Q

J Q

K

K

K

FF

FF

clock

9. Obtenha o diagrama de estados do circuito a seguir:

FF

output

80

EEL5310 - Sistemas Digitais - EEL/UFSC - Prof. Carlos Maziero

output

J Q

J Q

K Q

K Q

FF

clock

input

10. Projete um divisor de frequ^encia por 10.

FF