28/3/2011

Família Intel 80x86

Arquitetura de Computadores

Ao se falar em processadores, é

inevitável deixar de citar a Intel

Corporation e sua influente

família 80x86, que é formada

pelos principais processadores

utilizados pelos computadores

pessoais.

Este

capítulo

dedica-se

a

apresentar uma visão geral deste

modelo de arquitetura e estudar

os principais componentes e

respectivas tarefas desta família

de processadores.

Arquitetura dos Processadores Intel

80x86

Prof. Marcos Quinet

Universidade Federal Fluminense – UFF

Pólo Universitário de Rio das Ostras - PURO

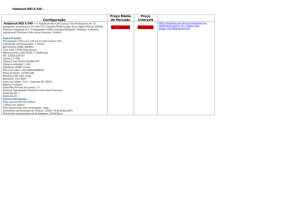

Intel 8086

2

Intel 8086

A família 80x86 começou em junho de 1978,

com

o

lançamento

do

processador

8086/8088*, que teve várias versões até 1982,

quando foi substituído pelo 80286.

A primeira versão lançada foi constituída por

29.000 transistores, e apresentava um

desempenho de 0.33 MIPS, a uma velocidade

de 5 MHz

Foram ainda lançadas versões de 8 e 10 MHz,

sendo que esta última atingia um desempenho

de 0.75 MIPS

3

O 8086 veio atender às necessidades de

aplicações que exigiam processamento de 16

bits, maior capacidade de memória, modos de

endereçamento mais sofisticados (para facilitar

a execução de programas escritos em

linguagem de alto nível) e suporte para

sistemas operacionais multiprogramados

A figura a seguir ilustra os principais elementos

da arquitetura do 8086

4

1

28/3/2011

Intel 8086

Intel 8086

O Intel 8088 possui a mesma organização do

8086, as únicas diferenças estão no tamanho da

fila de instruções (8 bytes no 8086 e 4 bytes no

8088) e no barramento de dados (16 bits no

8086 e 8 bits no 8088); devido as semelhanças,

estudaremos o 8086

A arquitetura do 8086 é dividida em 2 unidades

principais: a unidade de execução (EU –

Execution Unit) e a unidade de interface de

barramento (BIU – Bus Interface Unit)

5

Intel 8086

6

Intel 8086 – Unidade de Execução

Enquanto a EU abrange a unidade lógica e

aritmética e a unidade de controle, a BIU é

responsável por controlar os acesso externos à

memória principal e aos dispositivos de E/S

Se durante sua execução uma instrução requer

um acesso a um dado armazenado na memória,

a EU solicita o acesso a BIU

7

A ULA opera sobre dados de 8 ou 16 bits;

associado a ela existe um conjunto de 4

registradores de uso geral, denominados AX,

BX, CX e DX

Cada um destes registradores de 16 bits é

formado por uma metade inferior (AL, BL, CL e

DL) e por uma superior (AH, BH, CH e DH), onde

podem ser realizados acessos individuais,

constituindo cada metade um registrador de 8

bits

8

2

28/3/2011

Intel 8086 – Unidade de Execução

Intel 8086 – Unidade de Execução

Função dos registradores:

◦ AX: acumulador em instruções aritméticas e

lógicas;

◦ BX: usado por algumas instruções para armazenar

ponteiros para dados armazenados na memória

◦ CX: usado em instruções especiais, como o

controle de loop

◦ DX: usado como uma extensão do reg. AX em

instruções de multiplicação e divisão, armazenando

a metade superior de um produto de 32 bits ou de

um dividendo de 32 bits

Além dos de uso geral, existem na EU

registradores indexadores e apontadores, são

eles:

◦ SI (Source Index) e DI (Destination Index): utilizados

em operações envolvendo cadeias de caracteres

(strings)

◦ SP (Stack Pointer) e BP (Base Pointer) são

normalmente usados para realizar o acesso a pilha

em chamadas e retorno de rotinas; SP aponta para

o topo da pilha e o BP para a área de dados locais,

na pilha, da rotina em execução

◦ Flags e Operandos são usados para registrar

informações sobre o resultado de operações

aritméticas e lógicas e ainda, alguns bits de controle

9

10

Intel 8086 – Unidade da

Interface de Barramento

Intel 8086 – Unidade da

Interface de Barramento

Todos os acessos à memória e às interfaces de

E/S são controlados pela BIU. O 8086 possui

um barramento de endereço de 20 bits, que

suporta uma M.P. de até 1 MB

O 8086 acessa a memória organizada de forma

segmentada; nesta organização a memória é

dividida logicamente em blocos chamados

segmentos, cada um com um endereço-base

distinto

Uma locação de memória é referenciada

através de seu deslocamento (offset)

11

A BIU possui um conjunto de registradores de

segmento, onde cada registrador armazena dos

16 bits mais significativos do endereço-base do

segmento.

A cada acesso realizado, o valor do endereçobase é concatenado à esquerda com quatro bits

‘0’, formando um endereço de 20 bits; a este

endereço é somado o deslocamento (através de

um somador dedicado da BIU), resultando no

endereço da alocação

O deslocamento é um valor de 16 bits, o que

limita os segmentos a um tamanho máximo de

64 KB

12

3

28/3/2011

Intel 8086 – Unidade da

Interface de Barramento

Intel 8086 – Unidade da

Interface de Barramento

No 8086, um programa residente na memória é

dividido em 4 segmentos:

Para cada um destes segmentos existe um

registrador que armazena os 16 bits mais

significativos do endereço-base do segmento

correspondente. Estes registradores são:

◦ Segmento de código: contém as instruções do

programa;

◦ Segmento de dados: corresponde a área de

dados do programa;

◦ Segmento de pilha: área que se destina a pilha do

programa

◦ Segmento extra: área de dados adicional

◦

◦

◦

◦

CS: Code Segment register;

DS: Data Segment register;

SS: Stack Segment register;

ES: Extra Segment register.

13

Intel 8086 – Unidade da

Interface de Barramento

14

Intel 8086 – Unidade da

Interface de Barramento

Os quatro segmentos de um programa são

referenciados de acordo com o tipo de acesso a

memória, por exemplo, buscas de instruções são

feitas dentro do segmento de código indicado

pelo valor corrente no registrador de segmento

CS

No acesso a instruções, o deslocamento é dado

pelo conteúdo do registrador IP (Instruction

Pointer), que indica a próxima instrução a ser

buscada na memória

O reg. IP é diferente do contador de programas,

que indica a próxima instrução a ser executada

15

Acesso a dados em memória acontecem dentro

do segmento indicado pelo registrador DS, e o

deslocamento é gerado pelo programa, de

acordo com o modo de endereçamento usado

Acesso a dados também podem ocorrer dentro

do segmento extra, apontado pelo registrador

ES

Acesso à pilha ocorrem dentro do segmento de

pilha indicado pelo registrador SS

16

4

28/3/2011

Intel 8086 – Busca Antecipada

de Instruções

Intel 8086 – Busca Antecipada

de Instruções

O 8086 conta com um mecanismo de busca

antecipada de instruções (instruction prefetch),

para que o passo de busca de instrução seja

desvinculado dos demais passos de execução da

instrução

Desta forma, novas instruções podem ser

buscadas antecipadamente enquanto uma

instrução anterior ainda está sendo executada

Na busca antecipada, a fase de busca e a fase

de execução são separadas, e o tempo de busca

da instrução seguinte é “mascarado” pelo tempo

de execução da instrução corrente.

Na busca antecipada de instruções, é utilizada

uma fila de instruções, para manter as

instruções buscadas antecipadamente, até serem

buscadas pela EU

Uma

instrução

trazida

antecipadamente

permanece nesta fila até ser retirada pela EU

Em uma arquitetura sem busca antecipada, o PC

indica a próxima instrução a ser executada, que é

exatamente a próxima instrução a ser buscada

17

18

Intel 8086 – Busca Antecipada

de Instruções

Intel 8086 – conjunto de instruções

A busca antecipada reduz o tempo médio de

conclusão de cada instrução

Consequentemente, o tempo para executar um

certo número de instruções é menor, otimizando o

desempenho

Após o 8086, várias técnicas de paralelismo de

operações foram desenvolvidas, como no

pipelining e arquiteturas super-escalares

As instruções do 8086 podem ser classificas nos

seguintes grupos:

◦

◦

◦

◦

Instruções aritméticas;

Instruções lógicas;

Instruções de manipulação de strings;

Instruções de transferência de dados;

◦ Instruções de transferência de controle.

A arquitetura do 8086 é do tipo memória-registrador,

logo, as operações lógicas e aritméticas especificam

explicitamente 2 operandos, sendo que que um deles

atua como operando-fonte e operando-destino

◦ Apenas um dos operandos pode se encontrar na

memória

19

20

5

28/3/2011

Intel 8086 – conjunto de instruções

Intel 8086 – conjunto de instruções

As instruções aritméticas operam sobre números de 8

ou 16 bits, com ou sem sinal

Estão disponíveis instruções aritméticas específicas

para BDC

As instruções lógicas implementam as operações

booleanas básicas, instruções para deslocamento

aritmético e instruções para rotação do conteúdo de

registradores

Operações de manipulação de strings incluem:

movimentação

entre

regiões

de

memória,

comparação, procura de caracteres dentro da string e

transferência entre registradores e a memória

As instruções de transferência de dados

podem ser:

◦ de uso geral, que incluem as transferências

de dados entre registradores, registradores e

memória e acesso à pilhas;

◦ especiais,

utilizadas

para

carregar

registradores de segmento, salvar/carregar o

registrador de estado e para realizar o

acesso a interfaces de E/S

21

Intel 80286

Intel 8086 – conjunto de instruções

Instruções de transferência de controle podem

ser classificadas como:

◦ Condicionais: um desvio pode ou não ser

executado, dependendo se a condição testada pela

instrução é ou não verdadeira;

◦ Incondicionais: o desvio sempre é efetuado; são

instruções de chamada/retorno de rotinas e

instruções de controle de loop

22

Estão disponíveis instruções de transferência de

controle especiais, como INT, que provoca uma

interrupção, usada para implementar uma

chamada ao sistema operacional

23

As principais novidades na arquitetura do

80286 foram a execução de instruções em

pipeline e o suporte para memória virtual

Na arquitetura do 80286 foi implantado o

conceito de unidades independentes, que

realizam funções específicas:

◦ A unidade de barramento controla os acessos a

memória e interfaces de E/S, e realiza a busca

antecipada de instruções, colocadas em uma fila

na unidade de barramento

24

6

28/3/2011

Intel 80286

Intel 80286

A unidade de instrução decodifica as

instruções,

colocando

as

instruções

decodificadas em uma fila; a instrução

decodificada fornece de maneira mais

detalhada todas as informações necessárias à

execução da instrução

A unidade de controle, a ULA e o conjunto de

registradores formam a unidade de execução

◦ A unidade de execução retira da fila da UI as

instruções já decodificadas

◦ A ULA do 80286 é de 16 bits e o conjunto de

registradores é idêntico ao do 8086

25

26

Intel 80286

Intel 80286 – modos de operação

A unidade de endereço é responsável por

controlar a memória virtual, o que torna possível

a execução de programas com tamanho de

código maior do que a capacidade da memória

principal

27

O 80286 pode operar em dois modos,

chamados modo real e modo protegido

No modo real, o 80286 opera com um modelo

de memória semelhante ao do 8086, contando

com uma memória segmentada de 1 Mbyte

No modo protegido é utilizada a memória

virtual; neste modo, é dividida em 16384

segmentos, cada um com 64 Kbytes de

capacidade

Em teoria, seria possível executar programas

com até 1 Gbyte de tamanho, mas devido ao

barramento de endereço externo de 24 bits, o

tamanho máximo de MP é de 16 Mbytes

28

7

28/3/2011

Intel 80286 – modos de operação

No modo protegido é possível a execução de

sistemas operacionais multiprogramados de

maneira mais eficiente, uma vez que provê

proteção entre segmentos pertencentes a

diferentes programas

É importante observar que estes dois modos de

operação são estáticos: quando o 80286 é

iniciado, começa a operar no modo real; a

execução de uma instrução especial comuta sua

operação para o modo protegido, e permanece

neste modo até que seja reiniciado

Intel 80286 – modos de operação

Programas para o 8086 não podem ser

executados no modo protegido, pois quando o

sistema passa a funcionar neste modo, os

registradores de segmento assumem funções

diferentes daquelas no 8086 (uma limitação

corrigida no 80386)

As diversas unidades no 80286 podem operar

simultaneamente, realizando tarefas que fazem

parte da execução de diferentes instruções,

implementando a técnica conhecida como

pipeline; no 8086 a execução é puramente

sequencial

29

Intel 80386

30

Intel 80386

Devido a um período de transição, foram

lançadas duas versões do Intel 80386:

◦ SX: barramento de dados externo é de 16 bits;

◦ DX: barramento de dados externo é de 32 bits;

A arquitetura do 80386 é formada por oito

unidades lógicas, cujas funções básicas são:

◦ Bus Interface Unit (Unidade de barramento):

responsável por controlar os acessos externos à

memória e interfaces de E/S; recebe os pedidos de

acesso à memória de várias outras unidades

31

32

8

28/3/2011

Intel 80386

Intel 80386

Prefetch unit: realiza a busca antecipada de

instruções; possui uma fila de instruções, com

capacidade de 16 bytes, que solicita acessos à

memória para a unidade de barramento sempre

que a fila estiver parcialmente vazia ou quando

uma instrução de transferência de controle é

executada

Decode unit: retira uma instrução da fila de

instruções e gera uma instrução decodificada,

que é armazenada na fila de instruções

decodificadas (decoded queue) que, por sua

vez, são retiradas pela unidade de controle para

serem executadas

A unidade de dados (data unit) é formada por

uma ULA e um conjunto de registradores de 32

bits, representado abaixo:

31

16

15

0

AH

AX

AL

BH

BX

BL EBX

EAX

CH

CX

CL

ECX

DH

DX

DL

EDX

ESP

EBP

ESI

EDI

33

34

Intel 80386

Intel 80386

Existem 4 registradores de dados de 32 bits

(EAX, EBX, ECX e EDX) nos quais podem ser

feitos acessos a metade inferior de cada um,

como registradores de 16 bits (AX, BX, CX e

DX) que, por sua vez, podem ser considerados

como formados por dois registradores de 8 bits,

mantendo a compatibilidade com arquiteturas

anteriores

Os registradores apontadores ESP e EBP e os

registradores indexadores ESI e EDI são

realizados acesso apenas como registradores

de 32 bits

35

A memória virtual do 80386 é gerenciada pela

três unidades restantes: protection unit,

segmentation unit e paging unit

O 80386 implementa um modelo de memória

virtual organizada em segmentos e páginas;

◦ A unidade de proteção verifica se um endereço se

encontra dentro dos limites de um segmento;

◦ As unidades de segmentação e paginação

realizam a conversão entre endereços virtuais e

endereços reais

36

9

28/3/2011

Intel 80386

Intel 80386

Além dos modos real e protegido, já existentes no

80286, o 80386 possui mais um modo, chamado

modo 8086 virtual

Neste modo, programas desenvolvidos para o

8086 podem ser executados em um ambiente

multiprogramado protegido

No 80386 é possível comutar livremente do modo

protegido para o modo real e vice-versa, o que

ocorre, por exemplo, na abertura de uma janela

MS-DOS na interface gráfica Windows (que

executa em modo protegido), possibilitando a

execução de programas escritos para o 8086

(modo virtual)

A arquitetura do 80386 inclui todas as instruções

disponíveis nas versões anteriores, além de

várias outras, com destaque para as de teste de

bits, procura de caracteres em strings e

movimentação e conversão de dados

No 80386 estão disponíveis 11 modos de

endereçamento (incluindo os usados em

versões anteriores) além de um novo

componente utilizado no cálculo do endereço

efetivo, chamado escala (scale)

37

Intel 80386

38

Intel 80486

Escala é um fator (1, 2, 4 ou 8) que multiplica o

índice nos modos de endereçamento indexado

A escala facilita o acesso a vetores com

elementos de 16, 32 ou 64 bits; por exemplo,

para percorrer um vetor com elementos de 32

bits, são necessários incrementos de 4 bytes no

endereço efetivo

Se for utilizada uma escala 4, cada incremento

de 1 do índice resulta, após a multiplicação do

índice pela escala, no incremento de 4 bytes no

endereço efetivo

39

Do ponto de vista arquitetural, o 80486 é

basicamente uma extensão da arquitetura do

80386, contendo uma memória cache de 8

Kbytes e uma unidade de ponto flutuante

Em sistemas baseados no 80386 a memória

cache e a unidade de ponto flutuante são

externos ao processador

40

10

28/3/2011

Intel 80486

Intel 80486

Uma estratégia de mercado muito utilizada nesta

época e que é empregada até hoje são as

diferentes versões de implementação, oferecendo

diferentes recursos com custos variados

◦ 80486-SX: não possui a unidade de ponto flutuante

integrada com o processador, apenas a memória

cache

◦ 80486-DX: possui unidade de ponto flutuante e

cache integradas com o processador; a frequência

de clock do processador é a mesma usada nos

ciclos de barramento para acessos à memória e

interfaces de E/S

41

42

Intel 80486

Intel 80486 – memória cache

80486-DX2: a frequência de clock interna ao

processador é o dobro da frequência externa

usada nos ciclos de barramento, o que permite a

compatibilidade entre versões mais novas do

processador com hardware de sistemas mais

antigos e lentos

Foi lançada ainda uma versão DX4 do 80486,

com o clock interno triplicado, mas ficou pouco

conhecida por ter sido lançada após o Pentium

O 80486 possui uma cache com capacidade de

8 kbytes, para o armazenamento de instruções

e dados, organizada em 128 conjuntos de 4

linhas cada

tag

controle

linha 0 (16 bytes)

linha 1

linha 2

conjunto 0

linha 3

...

...

...

conjunto 127

43

44

11

28/3/2011

Intel 80486 – memória cache

Intel 80486 – memória cache

O 80486, assim como a maioria dos

processadores, utiliza um modelo de cache nassociativa por conjunto

Um endereço de cache é composto pelos

seguintes campos:

◦ Byte, formado pelos 4 bits menos significativos;

◦ Conjunto, formado pelos 7 bits seguintes;

◦ Tag, formado pelos 21 bits mais significativos do

endereço.

Observe que o tamanho destes campos está

relacionado com a configuração da cache, que

pode variar entre diferentes processadores

45

46

Intel 80486 – memória cache

Intel 80486 – memória cache

A não coincidência do tag do endereço com os

tags armazenados no conjunto indica que o byte

referenciado não se encontra na cache (cache

miss)

É usado um bit de controle para saber se o bloco

armazenado em uma linha selecionado foi ou

não modificado desde o seu carregamento na

cache

No caso da substituição de blocos, o bit de

controle serve para determinar se o bloco

selecionado pode ser simplesmente descartado

ou deve atualizar o dado correspondente na M.P.

47

A memória cache no 80486 utiliza a política de

substituição LRU (Least Recently Used)

Para minimizar os caches misses residuais, o

80486 implementa uma memória cache

secundária, em uma estrutura conhecida como

memória cache de dois níveis

A quantidade de memória cache varia

dependendo do modelo do 80486; a cache

primária é integrada ao processador e possui um

tamanho de no máximo 64 Kbytes; a cache

secundária é externa ao processador e pode

chegar a capacidade de 512 Kbytes

48

12

28/3/2011

Intel 80486 – memória virtual

Intel 80486 – memória virtual

Como possui suporte a memória virtual, o 80486

pode operar em dois modos:

◦ No modo real, o mecanismo de memória virtual é

desativado, e o modelo de memória é idêntico ao

do 8086: os programas visualizam uma memória

segmentada, com um tamanho máximo de 1 Mbyte

◦ No modo protegido, o mecanismo de memória

virtual é ativado, e o espaço de endereçamento é

de 64 Tbytes, enquanto o tamanho do espaço de

endereçamento real é de 4 Gbytes

O 80486 suporta os modelos de memória virtual

segmentada e paginada

O endereçamento virtual é organizado em

segmentos com tamanho entre 1 byte e 4

Gbytes, e cada segmento, por sua vez, pode ser

subdivido em páginas com 4 Kbytes de tamanho

O exemplo a seguir ilustra duas situações: na

primeira, a utilização de memória virtual apenas

segmentada; na segunda, com a paginação

ativada, o DAT de segmentação gera um

endereço linear, que por sua vez é convertido

pelo DAT de paginação no endereço real

O uso da memória virtual requer uma unidade de

MMU (Memory Management Unit), que contém o

hardware necessário ao uso da memória virtual

49

Intel 80486 – memória virtual

50

Intel 80486 – memória virtual

OBS: DAT (Dynamic Address Translator): realiza o

mapeamento entre um endereço físico real e um

endereço virtual, gerado pelo sistema

51

Na M.V. segmentada, o DAT considera que os

endereços virtuais são formados por um seletor

de segmento (segment selector) de 14 bits e um

deslocamento (offset) de 32 bits

O seletor de segmento é formado pelos 14 bits

mais significativos de um dos registradores de

segmento disponíveis

O deslocamento é o próprio endereço gerado

pelo programa, e indica a posição do byte onde

será feito o acesso em relação ao início do

segmento

52

13

28/3/2011

Intel 80486 – memória virtual

segmentada

Intel 80486 – memória virtual

segmentada

Os 13 bits mais significativos do seletor de

segmento são usados para indexar uma tabela

de descritores

A tabela de descritores desempenha o papel da

tabela de mapeamento: cada entrada da tabela

contém um descritor de segmento que, dentre

outras informações, indica o endereço-base do

segmento na memória principal

O endereço-base da tabela de descritores é

armazenada em um registrador específico, o

DTR (Description Table Register)

53

Intel 80486 – memória virtual

segmentada

54

Intel 80486 – memória virtual

segmentada

55

O seletor de segmento é concatenado ao

endereço em DRT, resultando no endereço de

um descritor de segmento

O deslocamento é então somado ao endereçobase do segmento indicado pelo descritor de

segmento, resultando no endereço real do byte

referenciado

56

14

28/3/2011

Intel 80486 – memória virtual

paginada

Intel 80486 – memória virtual

paginada

Na paginação do 80486, o mapeamento é feito

em dois níveis: primeiro, existe uma tabela de

diretório, que indica os endereços-base das

tabelas no segundo nível

O campo recebido do DAT de segmentação é

dividido logicamente em três campos:

◦ Diretório: com 10 bits, para acessar uma entrada

na tabela de diretório;

◦ Tabela: com 10 bits, é usado para o acesso a uma

entrada em uma das tabelas de página;

◦ Deslocamento: com 12 bits, indica a posição do

byte dentro da página

Cada tabela no segundo nível é chamada de

tabela de página, e contém os endereços-base

das páginas na memória principal

57

58

Intel 80486 – memória virtual

paginada

59

15