Exercícios para a 1ª Prova

Sistemas Embarcados

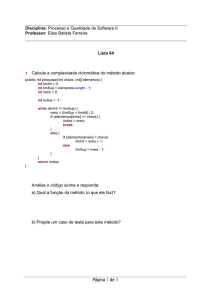

Exercício 1

Desenvolva uma função em Assembly Cortex-M3, seguindo

o padrão ATPCS, que efetue a soma de dois vetores e

com elementos cada:

extern void soma_vet(int m, int A[], int B[],

int S[]);

A soma de dois vetores é representada por:

, para

.

Exercício 2

Analise atentamente as funções em Assembly Cortex-M3

dadas a seguir:

Função 1: implementa R1:R0 = R1:R0 + R3:R2

PUBLIC soma

SECTION .text : CODE (2)

THUMB

soma: ADDS R0, R0, R2

ADC R1, R1, R3

BX LR

Exercício 2

Função 2: implementa R1:R0 = R1:R0 – R3:R2

PUBLIC subt

SECTION .text : CODE (2)

THUMB

subt: RSBS R0, R2, R0

SBC R1, R1, R3

BX LR

Exercício 2

Função 3: implementa R0 = R0 * R1

PUBLIC mult

SECTION .text : CODE (2)

THUMB

mult: MUL R0, R0, R1

BX LR

Exercício 2

Função 4: implementa R1:R0 = R0 * R1

PUBLIC mult

SECTION .text : CODE (2)

THUMB

mult: SMULL R0, R1, R0, R1

BX LR

Indique na tabela do próximo slide quais protótipos de

função em linguagem C correspondem às funções

implementadas em Assembly (padrão ATPCS).

Exercício 2

Correspondência

Protótipo de função em linguagem C

extern int mult(int a, int b); //

retorna a*b

extern int soma(int a, int b); //

retorna a+b

extern long long subt(long long a,

long long b); // retorna a–b

extern unsigned long long

mult(unsigned a, unsigned b); //

retorna a*b

Exercício 3

Ainda com relação às funções implementadas

em Assembly no Exercício 2:

a) Explique o que ocorreria se a instrução ADDS

R0, R0, R2 fosse substituída pela

instrução ADD R0, R0, R2 na Função 1.

b) Explique o que ocorreria se a instrução MUL

R0, R0, R1 fosse substituída pela

instrução MUL R1, R0, R1 na Função 3.

Exercício 4

R11

R12

R13

R14

R15

=

=

=

=

=

0x88776655

0x44332211

0x10001000

0x00001006

0x00000FFA

Dados os conteúdos dos registradores acima,

complete a tabela do próximo slide, que representa

o estado da memória RAM interna de um

microcontrolador LPC1343, após a execução da

seguinte instrução:

STMFD SP!, {R11-R12}

Exercício 4

Endereço

0x10001009

0x10001008

0x10001007

0x10001006

0x10001005

0x10001004

0x10001003

0x10001002

0x10001001

0x10001000

0x10000FFF

0x10000FFE

0x10000FFD

0x10000FFC

0x10000FFB

0x10000FFA

0x10000FF9

0x10000FF8

0x10000FF7

Conteúdo

Exercício 5

Refaça o Exercício 4, preenchendo a tabela que representa

o estado da memória RAM interna, após as instruções:

a)

b)

c)

d)

STMEA SP!, {R11-R12}

STMIA SP!, {R11-R12}

STMDB SP!, {R11-R12}

PUSH {R11-R12}

Qual é a função do “!” existente nas instruções acima? O

que ocorrerá caso o “!” seja removido?

Exercício 5

Quais seriam as instruções complementares a

cada uma das instruções anteriores para uso

coerente de uma estrutura de pilha? Nesse caso,

seria desejável não utilizar o “!” nas instruções?

Exercício 6

Dado o diagrama em blocos da memória EPROM dado no

próximo slide, responda:

a) Dada a organização interna indicada no diagrama qual

é a capacidade desta memória em Kbits?

b) Qual seria a organização externa desta memória para

um barramento de dados de

bits?

c) Qual seria a quantidade de sinais de endereço ( )

necessária para a organização externa do item b?

d) Que tipo de circuito deve ser implementado nos

blocos A e B para a organização externa do item b?

e) Quais são os dois sinais de controle comumente

encontrados em memórias EPROM?

Exercício 6