Arquitetura do PC e Barramento ISA

Cap5: 1/24

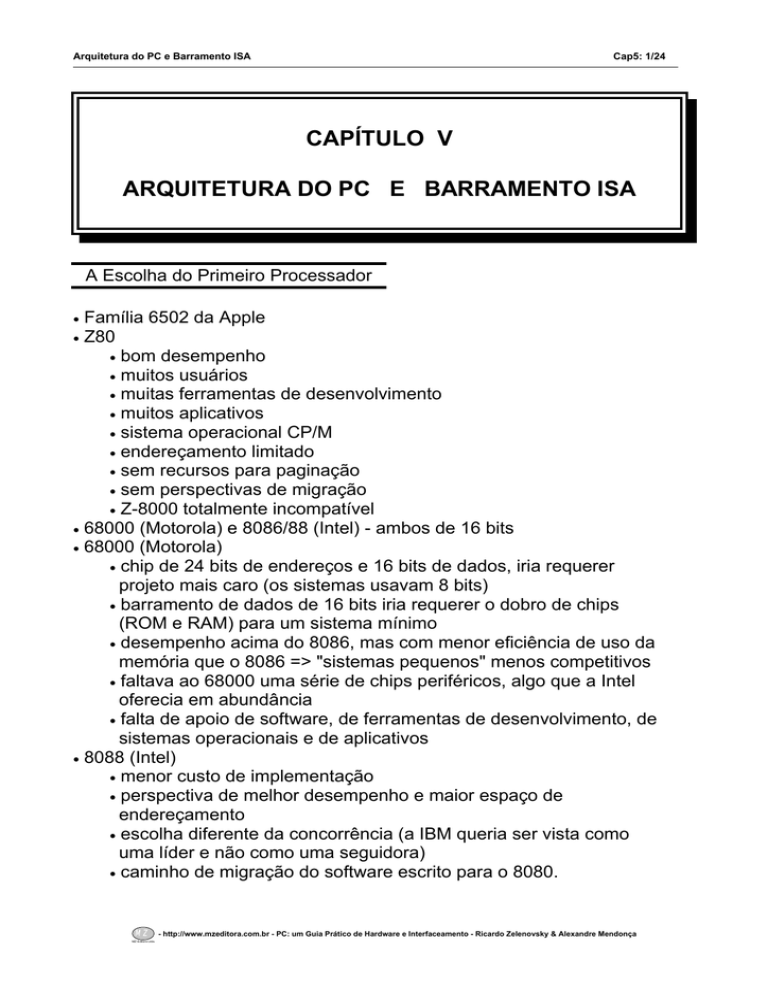

CAPÍTULO V

ARQUITETURA DO PC E BARRAMENTO ISA

A Escolha do Primeiro Processador

Família 6502 da Apple

• Z80

• bom desempenho

• muitos usuários

• muitas ferramentas de desenvolvimento

• muitos aplicativos

• sistema operacional CP/M

• endereçamento limitado

• sem recursos para paginação

• sem perspectivas de migração

• Z-8000 totalmente incompatível

• 68000 (Motorola) e 8086/88 (Intel) - ambos de 16 bits

• 68000 (Motorola)

• chip de 24 bits de endereços e 16 bits de dados, iria requerer

projeto mais caro (os sistemas usavam 8 bits)

• barramento de dados de 16 bits iria requerer o dobro de chips

(ROM e RAM) para um sistema mínimo

• desempenho acima do 8086, mas com menor eficiência de uso da

memória que o 8086 => "sistemas pequenos" menos competitivos

• faltava ao 68000 uma série de chips periféricos, algo que a Intel

oferecia em abundância

• falta de apoio de software, de ferramentas de desenvolvimento, de

sistemas operacionais e de aplicativos

• 8088 (Intel)

• menor custo de implementação

• perspectiva de melhor desempenho e maior espaço de

endereçamento

• escolha diferente da concorrência (a IBM queria ser vista como

uma líder e não como uma seguidora)

• caminho de migração do software escrito para o 8080.

•

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 2/24

Alguns PCs

•

PC original

CPU 8088

Circuitos de controle

4,77 MHz

do teclado

Soquete para

Circuitos de controle

coprocessador 8087

do gravador K-7

Temporizadores

Canal de áudio

e contadores - 8253

controlado por software

4 Canais de DMA

8237

Teclado de 84 teclas

Gravador

Alto-falante

BIOS

40 KB ROM

NMI e 8 interrupções

RAM do sistema com 4

8259

Bancos de 16 KB x 9 bits

Barramento de expansão e

slots de interface

5 Slots

Barramento

de dados

com 8 bits

(62 pinos).

Figura 5.1. O PC original.

•

PC XT

CPU 8088

Circuitos de controle

4,77 MHz

do teclado

Soquete para

Circuitos de controle

coprocessador 8087

Temporizadores

do gravador K-7

Canal de áudio

e contadores - 8253

4 Canais de DMA

8237

controlado por software

BIOS

40 KB ROM

NMI e 8 interrupções

RAM do sistema com 4

8259

Bancos de 64 KB x 9 bits

Barramento de expansão e

slots de interface

Teclado de 84 teclas

Gravador

Alto-falante

adaptador de HD,

portas, etc.

8 Slots

Barramento

de dados

com 8 bits

(62 pinos).

Figura 5.2. O PC XT.

•

PC XT com 8086/10MHz

•

PC AT 286

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 3/24

CPU 80286

6 a 25 MHz

Soquete para

coprocessador 287

Temporizadores

e contadores - 8254

7 Canais de DMA,

4 de 8 bits e 3 de 16 bits

NMI e 16 interrupções

2 x 8259

Circuitos de controle

do teclado

Relógio permanente e

RAM CMOS (64 bytes)

Canal de áudio

controlado por software

BIOS

64 KB ROM

RAM do sistema

128 KB x 9 bits

Teclado de 101 teclas

Bateria

Alto-falante

8 Slots

Barramento

de dados

com 8

ou 16 bits

Barramento de expansão e

slots de interface

Figura 5.3. Típico PC AT.

•

PS/2 - MCA da IBM e PC 386 - AT da Compaq

Arquitetura do PC XT

Lógica para

Temporização,

Decodificação

de Memória e I/O

Barramento

Local

(Local Bus)

Cristal

14,31818 MHz

4,77 CPU

MHz

8284

8088

Contr.

Barram.

Latches

Ender.

IRQ7

Dados

Endereço para DMA

245

D0-D7

A0-A15

A0-A7

245 (2x) 244

CKT

Estado

Espera

245

Controle

Endereços

Dados

Contr.

Inter.

8259

...

Endereços

(3x) 373

Coproc.

Matem.

8087

IRQ0

8 Slots de 62 Pinos

8288

Transc.

Dados

Pedido

Espera

Controle

244

Dados

245 (2x)158

RAM

Dinâmica

DMA

8237

Controle

Endereços

A16-A19

Control.

Reg. Pag.

DMA

670

ROM

BIOS

BASIC

(4x) 2764

A8-A15

373

Interface

Paralela

8255

Cheque de

Paridade

Lógica

NMI

Chaves de

Configuração

Teclado

Gravador

K-7

Contador

Temporiz.

8253

Figura 5.4. Diagrama de blocos do PC XT.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 4/24

MN/*MX → terra para o modo máximo

AD0...AD7 → linhas de endereços e dados multiplexados

A8...A15 -→ linhas de endereços não multiplexados

A16/S3...A19/S6 → endereços e estado multiplexados

CLK → relógio de 4,77 MHz com ciclo de carga de 33%

*RQ/*GT0 → conectado ao *RQ/*GT0 do coprocessador matemático

*RQ/*GT1 →- não utilizado

LOCK → não utilizado

INTR → pedido de interrupções gerado pelo controlador de interrupções

NMI → interrupção não mascarável

READY → usado para inserção de estados de espera em:

• todos os acessos de I/O

• todos os ciclos de DMA

• circuito conectado ao barramento de expansão

RESET → sinal de inicialização

QS0 e QS1 → permite que o coprocessador acompanhe a fila interna

TEST → conectado à saída BUSY do 8087

*S0, *S1 e *S2 → ligados ao 8288 (controlador de barramento), onde são

decodificados.

•

Circuito de relógio e base de tempo

14,313818 MHz

4,77 MHz

Barramento

de Expansão

8253

OUT 0

Data/Hora

8284

14,31818

MHz

1/3

1/ 4

1.19 MHz

OUT1

OUT2

Refresco

DRAM

Áudio

Figura 5.5. Geração do relógio no PC XT.

•

ROM do sistema

• inicialização do sistema

• diagnóstico de "power on" e checagem do sistema

• determinação da configuração do sistema

• "Basic Input/Output System" (BIOS)

• "Boot Strap Loader"

• padrão de bits para os primeiros 128 caracteres do conjunto total

de 256 caracteres (para o monitor de vídeo)

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

FFFFFh

Cap5: 5/24

(5 x) 2764

ROM

F6000h

F5FFFh

F4000h

F3FFFh

40 KB

8 KB

FFFFFh

FE000h

FDFFFh

BIOS e Sistema

Interpretador Basic

32 KB

F6000h

EPROM

8 KB

Não

Usado

NOTA: Depois do RESET,

a primera instrução

a ser executada é a que

está no endereço FFFF0h

16 KB

F0000h

Figura 5.6. ROMs existentes no PC XT.

•

RAM do sistema

•

Contadores/temporizadores

•

DMA do sistema

•

Interrupções do sistema

Arquitetura do PC AT

•

CPU 80286

•

Relógios iniciais de 6 e 8 MHz

•

ISA ("Industry Standard Architecture")

• adição de um segundo conector de 36 pinos (2 x 18), adjacente

ao de 62 pinos (2 x 31) que existia no PC XT

• recursos para barramento de dados de 8 ou 16 bits

• recursos para endereçamento de memória de 20 e 24 bits

• adição de 3 canais de DMA de 16 bits

• adição de mais 6 níveis de interrupção

• ciclos de barramento com maior velocidade

• apoio para ciclos de I/O sem estados de espera ("0 wait state")

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 6/24

Lógica para

Temporização e

Decodificação

de Memória e I/O

Barramento

Local

Cristal

12 MHz

(Local Bus)

Contr.

Barram. Controle

6 Slots de 62+36 Pinos

82288

CPU

Latches

Ender. Endereços

80286

(4x) 373

82284

A0-A23

6 MHz

Transc.

Dados Dados

Copro.

Matem.

80287

Pedido

Espera

IRQ0

...

IRQ15

245

D0-D15

D0-D15

A0-A23

(2x) 245 (3x) 244

CKT

Estado

Espera

A1-A8

A0-A7

245

Controle

Endereços

Dados

Contr.

Inter.

8259

A9-A16

A8-A15 A16-A23

244

Control.

DMA

8237

RAM

Dinâmica

Cheque de

Paridade

Dados

Lógica

NMI

Chaves de

Configuração

Control.

Teclado

Endereços

245 (2x)158

373

Reg. Pag.

DMA

74LS612

Controle

ROM

BIOS

2 Slots de 62 Pinos

Endereço para DMA

Teclado

8042

Gravador

K-7

Contador

Temporiz.

8254

Relógio

Permanente

MC146818

Figura 5.8. Diagrama em blocos dos primeiros PC AT 286.

•

Slots de expansão

Painel Traseiro

62

pinos

36

pinos

1

1

1

1

1

1

1

1

B A

B A

B A

B A

B A

B A

B A

B A

31

31

31

31

31

31

31

31

1

1

1

1

1

1

slots AT de 8 bits

semelhantes

aos do XT

D C

D C

D C

D C

D C

D C

18

18

18

18

18

18

Slots de 16 bits

Figura 5.9. Configuração dos slots dos primeiros PC AT.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

•

Cap5: 7/24

Alterações da parte XT para o ISA

• pino B8, não usado no XT, passou a ser "*0WS"

• "IRQ2" passou a ser "IRQ9"

• "MEMR" e "MEMW" viraram "SMEMR" e "SMEMW"

• CLK de 4,77 MHz passou a ser de 8 MHz (ou 8,33 MHz)

Sinais ISA herdados do PC XT

Unidade

de

Interface

com o

Barramento

do

Sistema

A0-A19

20

D0-D7

8

*DACK 0-3 4

DRQ 1-3 3

IRQ 2-7

6

*IOR

1

*IOW

1

*SMEMR 1

*SMEMW 1

ALE

1

OSC

1

CLK

1

TC

1

RESET DRV 1

AEN

1

*I/O CH CK 1

I/O CH RDY 1

GND

+5 V

+12 V

-5 V

-12 V

5 Slots

de

Expansão

3

2

1

1

1

(61 Sinais usados em um conector de 62 pinos)

Figura 5.10. Sinais originais do barramento de expansão.

•

OSC (oscilador), saída: 14,31818 MHz

CLK("Clock"), saída: 4,77 MHz (8086/88) e 8 ou 8,33 MHz (286 em

diante)

•

•

RESET DRV ("Reset Driver"), saída: inicialização dos periféricos

•

SA0-SA19, (endereços) saídas: linhas de endereços

•

SD0-SD7, (dados) bidirecional: linhas de dados

•

ALE ("Address Latch Enable"), saída: início de ciclo de barramento

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 8/24

*I/O CH CK ("I/O Channel Check"), entrada (coletor aberto): gera a

interrupção não mascarável (NMI)

•

I/O CH RDY ("I/O Channel Ready"), entrada (coletor aberto): permite

alongar os ciclos do barramento

•

•

IRQ 2-7 ("Interrupt Request" de 2 até 7), entrada: pedidos de interrupção

*IOR ("I/O Read"), saída: leitura em I/O (nos ciclos de I/O) ou leitura em

memória (nos ciclos de DMA)

•

*IOW ("I/O Write"), saída: escrita em I/O (nos ciclos de I/O) ou escrita em

memória (nos ciclos de DMA)

•

*SMEMW ("Memory Write"), saída: escrita no primeiro megabyte de

memória

•

*SMEMR ("Memory Read"), saída: leitura no primeiro megabyte de

memória

•

•

DRQ 1-3 ("DMA Request" de 1 até 3), entrada: pedidos de DMA

*DACK 0-3 ("DMA Acknowledge" de 0 até 3), saída: reconhecimento de

pedidos de DMA

•

AEN ("Address Enable"), saída: AEN = 0 => ciclo de I/O e AEN = 1 =>

ciclo de DMA

•

TC ("Terminal Count"), saída: término do número programado de

transferências por DMA

•

•

GND, +5 VDC, +12 VDC, -5 VDC, -12 VDC

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

GND

RST DRV

+ 5V

IRQ2

- 5V

DRQ2

- 12V

reservado

+ 12V

GND

*MEMW

*MEMR

*IOW

*IOR

*DACK3

DRQ3

*DACK1

DRQ1

*DACK0

CLOCK

IRQ7

IRQ6

IRQ5

IRQ4

IRQ3

*DACK2

TC

ALE

+ 5V

OSC

GND

Cap5: 9/24

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

(a)

*I/O CH CK

SD7

GND

RST DRV

SD6

SD5

SD4

+ 5V

IRQ9

- 5V

SD3

SD2

SD1

SD0

DRQ2

- 12V

*0WS

+ 12V

I/O CH RDY

AEN

SA19

GND

*SMEMW

*SMEMR

SA18

SA17

*IOW

*IOR

SA16

*DACK3

SA15

SA14

SA13

DRQ3

*DACK1

DRQ1

SA12

SA11

SA10

*DACK0

CLOCK

IRQ7

SA9

SA8

SA7

IRQ6

IRQ5

IRQ4

SA6

SA5

SA4

SA3

SA2

SA1

SA0

IRQ3

*DACK2

TC

ALE

+ 5V

OSC

GND

*MEM CS 16

*I/O CS 16

IRQ10

IRQ11

IRQ12

IRQ15

IRQ14

*DACK0

DRQ0

*DACK5

DRQ5

*DACK6

DRQ6

*DACK7

DRQ7

+ 5V

*MASTER

GND

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

*I/O CH CK

SD7

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

*SBHE

LA23

LA22

LA21

LA20

LA19

LA18

SD6

SD5

SD4

SD3

SD2

SD1

SD0

I/O CH RDY

AEN

SA19

SA18

SA17

SA16

SA15

SA14

SA13

SA12

SA11

SA10

SA9

SA8

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

LA17

*MEMR

*MEMW

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

(b)

Figura 5.11. (a) Slot original do PC XT. (b) Conector ISA, para 286,

386, 486, etc.. Notar as diferenças nos pinos B4, B8, B11 e B12.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 10/24

Sinais ISA introduzidos com o PC AT

Unidade

de

Interface

com o

Barramento

do Sistema

20

SA0-SA19

/

8

SD0-SD7

/

4

*DACK0-3

/

3

DRQ1-3

/

6

IRQ3-7, 9

/

*IOR' *IOW' *SWMR' *SMEW4

/

1

ALE

/

2

OSC, CLK

/

1

TC

/

1

RESET DRV

/

2

AEN, *0WS

/

*I/O CH CK, I/O CH RDY 2

/

3

GND

/

2

+5 V

/

1

+12 V

/

1

-5 V

/

1

-12 V

/

LA17-23

/

SD8-SD15

/

*DACK 0, 5, 6, 7

/

DREQ 0, 5, 6, 7

/

IRQ 10, 11, 12, 14, 15

/

*MEMR' *MEMW

/

*MEM CS16, *I/O CS16

/

*SBHE

/

*MASTER

/

+5 V

/

GND

/

Slot

de 62

Pinos

Herdado dos

Primeiros PCs

7

8

4

4

5

2

2

1

Slot

de 36

Pinos

1

Acrescentado

1

a Partir do AT

1

Figura 5.12. Sinais que trafegam pelos slots de expansão ISA.

*SBHE ("System Bus High Enable"), saída: tipo *BHE - habilita acesso à

parte alta do barramento

•

*SBHE

0

0

1

1

A0

0

1

0

1

Função

Transferência de 16 bits

Transferência do byte alto

Transferência do byte baixo

Inativo

Figura 5.13. Decodificação dos modos de transferência de dados.

*MEMR ("Memory Read"), saída: leitura a partir do segundo megabyte de

memória

•

*MEMW ("Memory Write"), saída: escrita a partir do segundo megabyte

de memória

•

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

•

Cap5: 11/24

DRQ 5-7 ("DMA Request 5 a 7"), entrada: novos pedidos de DMA

*DACK 5-7 ("DMA Acknowledge 5 a 7"), saída: novos reconhecimentos

de pedidos de DMA

•

DRQ 0/*DACK 0, entrada/saída: pedido/reconhecimento do canal 0, usado

no XT e não usado no AT

•

*MEM CS16 ("Memory Chip Select 16 bits"), entrada coletor aberto:

aciona barramento de 16 bits em ciclos de memória

•

*I/O CS16 ("I/O Chip Select 16 bits"), entrada coletor aberto: aciona

barramento de 16 bits em ciclos de I/O

•

•

*MASTER, entrada: solicitação para mestre de barramento

IRQ 10, 11, 12, 14 e 15 ("interrupt request"), entradas: novos pedidos de

interrupção

•

LA 17-23 ("unlatched address 17-23"), saídas. complemento das linhas

de endereço

•

•

SD 8-15 (dados), bidirecionais: complemento das linhas de dados

Ciclos de barramento

Ciclo de barramento para a leitura da memória

• Ciclo de barramento para a escrita na memória

• Ciclo de barramento para a leitura de um dispositivo de I/O

• Ciclo de barramento para escrita em um dispositivo de I/O

• Ciclo de barramento para reconhecimento de interrupção

• Ciclo de escrita via DMA

• Ciclo de leitura via DMA

•

•

Ciclos no PC XT

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 12/24

T1

T2

T3

T4

CLOCK

(relógio)

ALE

SA0 - SA19

Endereço Válido

*MEMR

SD0 - SD7

OBSERVAÇÕES:

*MEMW=*IOR=*IOW=HIGH

Dado Válido

(entregue pela memória)

IO CH RDY=HIGH (ativado)

Figura 5.14. Ciclo de barramento original para leitura da memória (no PC XT).

•

Ciclos do Barramento ISA

• 8 ou 8,33 MHz ?

• placa-mãe insere 1 estado de espera nos ciclos de memória

• placa-mãe insere 3 estados de espera nos ciclos de I/O

• ativação de *0WS retira estados de espera introduzidos pela placamãe

T1

TW

T2

Relógio (8 MHz) do

Barramento ISA

ALE

endereço válido

SA0-SA19, *SBHE

LA17-LA23

endereço válido

*SMEMR ou *MEMR

Data Setup

SD0-SD15

Data Hold

Dado Válido

*MEM CS16

I/O CH RDY

Figura 5.20. Ciclo para leitura de memória, com um estado de espera (ISA).

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

T1

Cap5: 13/24

TW1

TW2

TW3

TW4

T2

Relógio (8 MHz) do

Barramento ISA

ALE

endereço válido

SA0-SA15 *SBHE

*IOR

Data

Setup

Dado

Válido

SD0-SD15

(gerado pela placa ISA)

Data

Hold

*I/O CS16

I/O CH RDY

Figura 5.22. Ciclo para leitura de I/O, com quatro estados de espera (ISA).

T1

TW1

TW2

TW3

TW4

T2

Relógio (8 MHz) do

Barramento ISA

ALE

SA0-SA15 *SBHE

endereço válido

*IOW

Data

Setup

SD0-SD15

(gerado pela CPU)

Dado

Válido

Data

Hold

*I/O CS16

I/O CH RDY

Figura 5.23. Ciclo para escrita de I/O, com quatro estados de espera (ISA).

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

DMA IDLE

Cap5: 14/24

DMA 1

DMA 2

DMA 3

DMA 4

DMA IDLE

Relógio DMA

DRQ XX

AEN

*DACK XX

SA0-SA19, *SBHE

endereço válido

LA17-LA24

endereço válido

*SMEMR ou *MEMR

*IOW

SD0 - SD15

dado

Data

Setup

Data

Hold

I/O CH RDY

Figura 5.24. Ciclo de barramento para leitura por DMA (escrita em I/O) (ISA).

Geração de estados de espera

T1

T2

T3

TW

T4

CLOCK

READY

Ready Desativado

Máximo

Ready Setup

(Entrada READY da CPU)

Hold Time

Figura 5.26. Sistema normalmente "ready" inserindo um estado de espera.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 15/24

+5V

Cristal

X1

X2

CPU

8088

F/*C

R

RES

C

*RDY/WAIT

DMA WAIT

8284

AEN1

CLK

RDY1

CLK

RESET

RESET

READY

READY

+5V

AEN2

RDY2

Figura 5.27. Conexão do 8284 com a CPU.

DECODIFICADOR

ADR BITS

SELECIONA I/O

SELECT

ADR

VCC

AEN(A11)

AEN

4K7

Coletor Aberto

4

*IOR(B14)

2

1

2

74LS00

3

*IOW(B13)

3

P Q

R

CLK

C Q

L

D

5

1

2

I/O CH RDY (A10)

74LS05

6

74LS74

1

RESET(B02)

2

3

74LS02

1

3

4

6

11

13

14

CLK(B20)

9

1

D1

D2

D3

D4

D5

D6

Q1

Q2

Q3

Q4

Q5

Q6

2

5

Seleção do Número

de Estados de Espera

7

10

12

15

CLK

CLR

SW DIP-5

74LS174

Figura 5.31. Circuito para gerar estados de espera,

em ciclos de leitura ou escrita em I/O.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 16/24

VCC

Coletor Aberto

4

2

*DACK1(B17)

*DACK2(B26)

1

2

13

*DACK3(B15)

3

12

74LS10

P Q

R

CLK

C

L Q

D

1

5

2

I/O CH RDY (A10)

74LS05

6

74LS74

1

RESET(B02)

2

1

3

74LS02

CLK(B20)

1

2

3

4

6

11

13

14

D1

D2

D3

D4

D5

D6

9

1

CLK

CLR

74LS04

Q1

Q2

Q3

Q4

Q5

Q6

Seleção do Número

de Estados de Espera

2

5

7

10

12

15

1

2

3

4

8

7

6

5

SW1 DIP-4

74LS174

Figura 5.33. Circuito para gerar estados de espera para qualquer canal de DMA.

T1

TW1

TW2

T2

Relógio (8 MHz) do

Barramento ISA

ALE

SA0-SA19, *SBHE

endereço válido

*MEMR ou *MEMW

SD0-SD15

Data

Setup

Dado

Válido

Data

Hold

*MEM CS16

I/O CH RDY

Adição um

Estado de Espera (TW2)

RDY Setup

RDY Hold

Figura 5.35. Temporização para inserir estados

de espera em ciclos de acesso à memória (ISA).

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 17/24

T1

TW1

TW2

TW3

TW4

T2

Relógio (8 MHz) do

Barramento ISA

ALE

SA0-SA15, *SBHE

endereço válido

*IOR ou *IOW

SD0-SD15

Data

Setup

Dado

Válido

Data

Hold

*IO CS16

I/O CH RDY

Adição um

Estado de Espera (TW4)

RDY Setup

RDY Hold

Figura 5.36. Temporização para provocar estados

de espera em ciclos de acesso a I/O (ISA).

DMA IDLE

DMA 1

DMA 2

DMA 3

DMA WAIT

DMA 4

DMA IDLE

Relógio DMA

DRQ XX

AEN

*DACK XX

SA0-SA19

endereço válido

LA17-LA24

endereço válido

*MEMR ou *IOR

*MEMW ou *IOW

SDO -SD15

dado

Data Setup

I/O CH RDY

Inserido um

Estado de Espera

RDY Setup

Data Hold

RDY Hold

Figura 5.37. Temporização para provocar estados de espera em ciclos de DMA.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 18/24

T1

T2

Relógio (8 MHz)

do Barramento

BALE

A, *SBHE

endereço válido

Leitura ou Escrita

Dado

Válido

Data Setup

Data Hold

SD0-SD15

*MEM ou *I/O CS16

* 0WS

*0WS Setup

*0WS Hold

Figura 5.38. Temporização para ativação do sinal *0WS.

Outros barramentos

•

Barramento EISA ("Extended Industry Standard Architecture")

• 8,33 MHz

• 32 bits de dados

• configuração de placas por software

• 100 novos sinais em profundidade

• modo rajada

•

Barramento MCA ("Micro Channel Architecture")

• patente da IBM

• desempenho semelhante ao EISA

•

Barramento VESA Local Bus ("Video Equipment Standard Association")

• consórcio de 120 companhias

• 33 MHz

• 32 bits e previsão para 64 bits

• dependência do processador (486)

• carrega o barramento => máximo de 3 slots

• aplicações principais: placas de vídeo, rede e disco

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

CPU

Cap5: 19/24

(Barramento Local)

Cache

Subsistema

de

Memória

Controlador

VL BUS

VL BUS

Controlador

Gráfico

Controlador

de Disco

32 BITS / 33 MHz

Controlador de

Barramento ISA

Placa

de Rede

Barramento ISA

16 BITS / 8 MHz

Placa

FAX

I/O

I/O

I/O

Modem

Figura 5.41. Barramento local (VL-BUS) proposto por VESA.

•

Barramento PCI ("Peripheral Component Interconnect")

• plug and play

• permite até 10 carregamentos elétricos (um deles pode ser um

controlador para barramento ISA)

• trabalha com 32 ou 64 bits a uma velocidade de 33 MHz ou 66

MHz

• não carrega demais o barramento da CPU

• não possui dependência com o processador, por não se tratar de

um barramento local

• conceitos de iniciador e alvo

• especificação permite a comunicação entre diversos barramentos

isolados eletricamente através de uma Ponte PCI-PCI

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 20/24

Subsistema

de

Memória

(Barramento Local)

CPU

Cache

Ponte

PCI

Barramento PCI

Controlador

Gráfico

Placa

de Rede

Memória

I/O

32/64 bits / 33/66 MHz

Ponte

ISA

Controlador

de Disco

Barramento ISA 16 bits / 8 MHz

I/O

Placa

FAX

Modem

Vídeo

Aúdio

Animado

Memória

I/O

Figura 5.43. Arquitetura PCI.

•

Barramento USB ("Universal Serial Bus")

•

Barramento AGP ("Accelerated Graphics Port")

•

Barramento FireWire - IEEE 1394-A

Chipsets modernos

Chipset é um grupo de circuitos integrados destinados a uma tarefa

específica, como, por exemplo, construir um computador. No caso dos

PCs, o chipset traz integrado uma série de dispositivos auxiliares, tais

como: controladores de interrupções, de DMA e de memória dinâmica,

temporizadores, pontes PCI e ISA, etc.. Cada chipset define um

computador diferente.

•

importância do chipset

•

440BX e 440GX => barramentos de 100 MHz

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 21/24

430VX 430HX 430TX 440FX 440BX 440GX

Triton II Triton III Triton IV

Início 96 Início 96 Início 97 Início 97 Início 98 Início 98

Mediano Ponta Mediano Mediano Ponta

Ponta

Médio

Alto

Alto

Médio

Alto

Alto

Nome

Lançamento

Mercado

Custo

Clock (MHz) 50, 60, 66 50, 60, 66 50, 60, 66 50, 60, 66 60, 66, 100 60, 66, 100

Nr. CPU’s

1

2

1

2

1

2

Limite cache

512 KB 512 KB 512 KB

possível cache 64 MB 512 MB 64 MB

1 GB

2 GB

2 GB

Paridade

Não

Sim

Não

Sim

Sim

Sim

USB

Não

Sim

Sim

Sim

Sim

Sim

AGP

Não

Não

Não

Não

Sim

Sim

Oscilador

66 MHz

CPU

66 MHz

P5/66 MHz

Relógio

Barramento 66MHz

Local

64 bits

Chipset

66MHz

430LX

"Mercury"

PCI

ISA

I/O

16 bits

I/O

8MHz

I/O

32 bits

Ponte ISA

I/O

64 bits

33MHz Ponte PCI

RAM

Cache

I/O

I/O

Figura 5.46. Diagrama em blocos com o Pentium de 66 MHz,

ressaltando-se a velocidade e tamanho dos diversos barramentos.

Oscilador

66 MHz

66MHz

P5 MMX 200 MHz

xn

CPU

n=3

66MHz

Barramento 64 bits

Local

Chipset

430TX

"Triton IV"

66MHz

Ponte PCI

64 bits

RAM

Cache

Figura 5.47. Computador com P5 MMX 200 MHz, onde se deve notar o multiplicado por n (n = 3).

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Oscilador

66 MHz

Cap5: 22/24

66MHz

128 bits

BSB

P5-II 300 MHz

xn

CPU

Cache

150 MHz

66MHz

64 bits

FSB

Chipset

66MHz

64 bits

440 FX

RAM

Ponte PCI

Figura 5.48. Computador com P5-II/300 MHz, onde se pode notar

o BSB (Back Side Bus) e o FSB (Front Side Bus) de 66 MHz.

Oscilador

100 MHz

100MHz

BSB

P5-II 400 MHz

x n CPU

FSB

128 bits

Cache

200 MHz

100MHz

64 bits

Chipset

100MHz

64 bits

440 BX

PCI

ISA

16 bits

32 bits

8MHz

Ponte ISA

I/O

I/O

I/O

33MHz

I/O

Ponte PCI

RAM

I/O

I/O

Figura 5.49. Computador com P5-II/400 MHz, onde se pode notar

o BSB (Back Side Bus) e o FSB (Front Side Bus) de 100 MHz.

•

chipsets para PC100 (memórias síncronas)

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 23/24

Velocidade

MB/s

3500

3200

3000

2400

2500

2000

1500

1000

800

540

500

8

133

8

133

0 ISA PCI FSB BSB

ISA PCI FSB BSB

P5-II/300 MHz

P5-II/400 MHz

Figura 5.50. Comparação de velocidade entre os diversos barramentos

presentes em computadores com P5-II de 300 MHz e 400 MHz.

Exercícios

5-3) Qual o tempo mínimo, em períodos de clock de barramento, para

realizar um acesso de I/O, a 16 bits (ISA), quando:

endereço base a

ser acessado

utilização da

linha *0WS

utilização da

linha *I/OCS16

par

par

par

par

ímpar

ímpar

ímpar

ímpar

sim

sim

não

não

sim

sim

não

não

sim

não

sim

não

sim

não

sim

não

resposta (em

clocks ISA)

5-4) Qual a diferença entre os sinais *MEMR dos dois conectores que

compõem o barramento ISA: o de 62 pinos e o de 36 pinos ?

5-11) Um técnico mediu a largura do pulso *IOW no barramento ISA de um

computador antigo sendo aproximadamente igual a 450 ηs. Estime o número

de estados de espera introduzidos pela placa-mãe do sistema ? Qual a

duração de um ciclo de barramento ISA para I/O neste computador ?

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Arquitetura do PC e Barramento ISA

Cap5: 24/24

5-13) O que pode acontecer se, por engano, o projetista utilizar um 7404, ao

invés do 7405, para acionar a linha I/O CH RDY ?

5-15) Ao depurar um circuito, um técnico verificou que o sinal *I/O CS 16

estava sendo erroneamente ativado durante o ciclo de I/O gerado pelas

instruções

mov dx,300h

in ax,dx

.

Supondo que fossem desejados dois ciclos de barramento para a realização

da comunicação (basta não utilizar o sinal *SBHE), que tipo de problema

aquela ativação de *I/O CS 16 causaria ?

5-16) Repita o problema anterior, só que agora com o ciclo gerado por

mov dx,300h

in al,dx

.

5-17) Repita o problema anterior, só que agora com o ciclo gerado por

mov dx,300h

in eax,dx .

5-19) (Concurso para o Quadro de Engenheiros Militares do Exército especialidade eletrônica - 1997)

Um microprocessador, ao executar o programa listado abaixo, envia uma

série de dados para um periférico mapeado no endereço 90h. Considerando

que a execução de cada instrução leve exatamente 1 período de relógio,

faça um gráfico de nível lógico (0 ou 1) versus tempo (em períodos de

relógio) para cada um dos três bits menos significativos do dado escrito no

endereço 90h.

Programa:

mov ax,0

out 90h,ax

mov bx,5

LABEL:

mov ax,bx

inc ax

out 90h,ax

dec bx

jnz LABEL

mov ax,0

out 90h,ax

halt

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.