Matéria teórica de Arquitectura de Computadores

Componentes de processador.

Um processador é constituído por registos, acumulador, ALU( unidade lógica

aritmética): apontador de instruções; registador de instruções; descodificador de

instruções.

Explique resumidamente o objectivo da arquitectura RISC e as suas

características.

A arquitectura RISC é uma arquitectura que utiliza um número de instruções

reduzidas mas não mínimo, sendo os modos de endereçamento também reduzidos; os

formatos das instruções são fixos e facilmente descodificados; utiliza unidades de

controlo de tipo hardware em vez de microprogramáveis; acesso à memória é feito

através de “load’s” e “store’s”, que são o suporte para as linguagens de programação de

alto nível ( utilização de compiladores para optimizar a performance); execução de uma

instrução num único ciclo de relógio (ler 2 registos adicionar armazena o

resultado no registo); programação mais fácil.

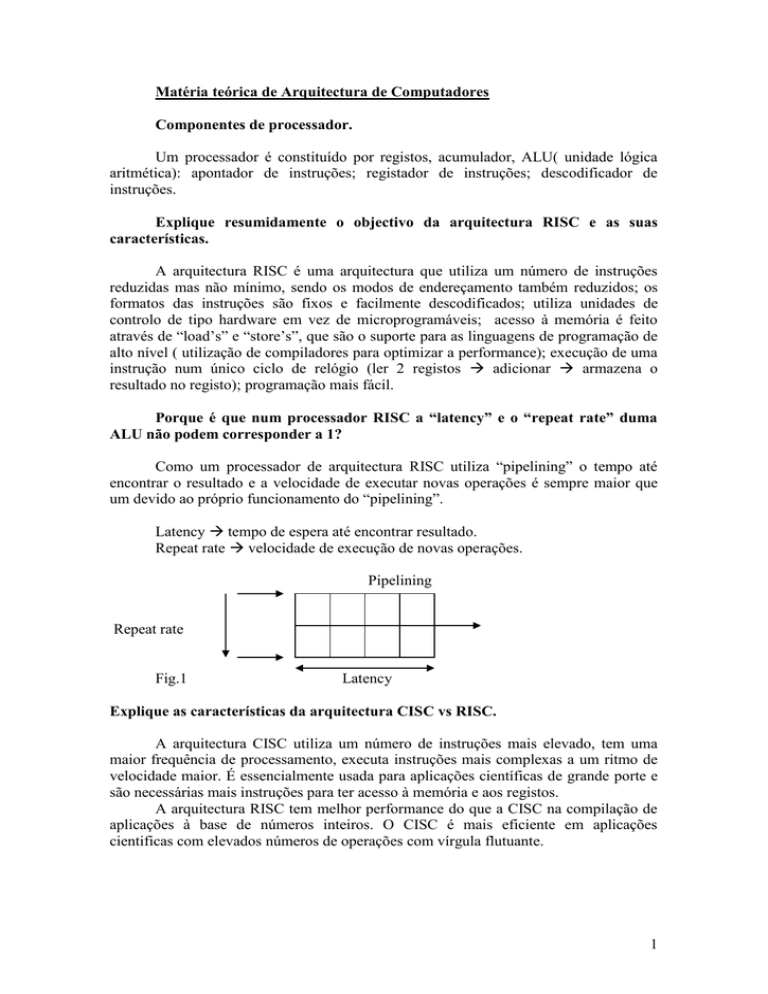

Porque é que num processador RISC a “latency” e o “repeat rate” duma

ALU não podem corresponder a 1?

Como um processador de arquitectura RISC utiliza “pipelining” o tempo até

encontrar o resultado e a velocidade de executar novas operações é sempre maior que

um devido ao próprio funcionamento do “pipelining”.

Latency tempo de espera até encontrar resultado.

Repeat rate velocidade de execução de novas operações.

Pipelining

Repeat rate

Fig.1

Latency

Explique as características da arquitectura CISC vs RISC.

A arquitectura CISC utiliza um número de instruções mais elevado, tem uma

maior frequência de processamento, executa instruções mais complexas a um ritmo de

velocidade maior. É essencialmente usada para aplicações científicas de grande porte e

são necessárias mais instruções para ter acesso à memória e aos registos.

A arquitectura RISC tem melhor performance do que a CISC na compilação de

aplicações à base de números inteiros. O CISC é mais eficiente em aplicações

cientificas com elevados números de operações com vírgula flutuante.

1

CPU

CPU

Reg

+

*

Reg

+

I

D

*

L1

I

L1

D

L2

L2

L3

L3

Main Memory

Main Memory

RISC – memória

Alfa Digital 21164

MPP SMP

CISC – memória

Pentium II

MPP SMP

Fig.2

Faça um desenho de um CPU simples com todos os registos necessários, a ALU e

ao sistema de barramento (BUS), etc. O sistema tem de funcionar.

CPU

Data Processing Unit

AC

MQ

CIRCUITOS

LÓGICOS

ARITMÉTICOS

I/O

DR

IBR

PC

IR

AR

MAIN

MEMORY

ADDRESS

CICUITOS DE

CONTROLO

SINAIS DE

CONTROLO

Program Control Unity

Fig.3

2

Qual o perfil que uma empresa deve tomar ao desenvolver um projecto?

Uma empresa, antes de desenvolver um projecto tem de definir qual o perfil, as

características do sistema a criar. Tem de ponderar:

- Software;

- Hardware;

- Sistema MPP,SMP ou PVP;

- Arquitectura CISC ou RISC;

- Memória;

- Dispositivos de I/O (input/output);

Dê pelo menos 4 aspectos importantes a ter em conta na compra de uma

máquina.

- Confiabilidade da empresa;

- Preço;

- Cumprimento/performance;

- Atendimento ao utilizador (aplicações, programação);

Componentes a ter em conta na compra de um computador:

CPU cabinet sheet metal, plastic, cables, nuts, batts, shipping box, manuais,

power suply e fans

CPU board IV, FPU, MMU, cache, DRAM, video logic, dispositivos de I/O,

printer circuit board.

Dispositivos de I/O teclado, rato, monitor, disco rígido, drives (disquetes,

cd’s)

Preço =custo dos componentes + direct cost + gross margin + desconto

Quais os elementos do preço PVP de um computador?

RAM; CPU; Cache; Disco Rígido; Placa de vídeo; dispositivos de I/O; Garantia;

Refrigeração; Dimensões da caixa.

Nota: É mais fácil baixar o preço do que aumentar a performance. Encontrar um

bom computador com uma boa performance é muito difícil.

Se não tiver resultados “benchmark” disponíveis, que pode fazer para

comparar a performance?

Podemos utilizar algoritmos de corridas assíncronas para comparar a

performance.

Assuma que deve comprar um grande computador para um laboratório

com aplicações cientificas e pode seleccionar entre n sistemas diferentes. Dê pelo

menos 4 aspectos importantes a ter em conta.

- Velocidade do CPU

- Tamanho da RAM

- Tamanho da Cache

- Placa de vídeo

3

- Tamanho e tempo de acesso do disco rígido

- Monitor

A arquitectura deve ser apropriada à utilização do sistema a adquirir. No

caso de serem necessárias muitas operações em vírgula flutuante a arquitectura

RISC será a mais apropriada. Caso sejam necessárias muitas operações em inteiros,

a arquitectura CISC é a mais indicada.

Sistemas multiprocessadores (tipos):

Vectorial – processadores fabricados para casos específicos.

Escalar – processadores normais (só podem arrancar com uma instrução).

Super escalar – o processador pode arrancar com mais de uma instrução.

PVP (Parallel Vector Processor)

Contém um reduzido número de processadores VP’s, cada um capaz de pelo

menos, 1 Gf/s de performance. O crossbar switch conecta os VP’s à shared memory

(SM). Normalmente não usam cache mas possuem um grande número de registos de

vector e um buffer de instrução.

VP

VP-vector processador

SM- shared memory

VP

…

VP

Crossbar Switch

SM

Fig.4

SM

SM

SMP (Symetric Multiprocessor)

Usa “commodity microprocessors” com caches “on” e “off” “chip”. Os

processadores estão conectados à memória partilhada através de um bit de alta

velocidade, em alguns SMP é adicionado ao bus um “crossbar switch”.

Estes sistemas são muito usados em aplicações comerciais, tais como, bases de

dados, sistemas de transacção on-line, armazéns de dados, etc.

O facto dos sistemas serem simétricos é muito importante, pois cada processador

tem igual acesso à SM, aos dispositivos de I/O e ao sistema operativo. Deste modo

alcança-se um alto nível de paralelismo, o que não é alcançado por um sistema

assimétrico ou “masterslave”.

PC

PC- microprocessador e cache

SM- shared memory

I/OB- input/output bus

PC

...

PC

Crossbar Switch

SM

SM

I/OB

Fig.5

4

MPP (Massively Parallel Processor)

Usa “commodity microprocessors” ao processar “nodes”. Usa memória física

distribuída após processar “nodes”. Usa um interconector com alta comunicação

“bandwith” e baixa latência. Pode ser escalonável até centenas ou milhares de

processadores.

MB

MB

PC

MB- memória do bus

PC- microprocessador e cache

LM- memória local

NIC- network interface circuit

LM

PC

.......

NIC

Fig.6

LM

NIC

Custom Designed Network

DSM (Distributed Shares Memory Machine)

A directoria é usada para suportar a distribuição coerente das caches. A memória

é distribuída fisicamente pelos diferentes “nodes”. O sistema hardware e software criam

a ilusão de um único espaço de endereços para os utilizadores das aplicações.

MB

MB- memória do bus

PC- microprocessador e cache

LM- memória local

DIR- cache e directório

NIC- network interface circuit

MB

PC

LM

PC

......

LM

DIR

DIR

NIC

NIC

Fig.7

Custom Designed Network

COW (Cluster of Workstation)

São variantes dos MPP a um preço mais baixo. Cada “node” de uma COW é

uma “workstation” completa, excepto os periféricos. Os “nodes” estão ligados através

de uma “low-cost commodity network” tal como a Ethernet, etc. O interface da network

está “loosely coupled” ao I/O bus. Existe sempre um disco local ( o que não acontece no

MPP). Em cada “node” reside um completo sistema operativo. Têm muitas vantagens

em termos de custo à performance, em relação aos MPP’s.

5

MB

MB- Memory bus

PC- microprocessor and cache

Bridge- interface entre memory bus

LD- Local disk

NIC- Network interface circuit

I/OB- IO Bus

MB

PC

PC

M

M

Bridge

LD

……

I/OB

NIC

Fig.8

Bridge

LD

I/OB

NIC

Commodity Network (Ethernet, etc)

COW vs MPP

Prevê-se que no futuro MPP e COW convergem, assim que existirem Gbit/s

networks, para conectar os “nodes” da COW.

MPP:

- Usados para computação de alto nível.

- Têm segurança implícita.

- Valorizam um alto número de tarefas executadas pela máquina e uma elevada

performance dos I/O e da memória.

- São mais caros e não têm suporte OS de som para processamento de sinal em

tempo real.

COW:

- Satisfazem as necessidades iterativas e de multitarefas nas aplicações.

- Necessitam de segurança especial

- Oferecem um fácil acesso aos sistemas de B.D. de larga escala.

- Não suportam DSM ou não têm “single system image”.

Explique resumidamente os 3 benchmarks Linpack.

O Linpack é um programa para resolver um denso sistema de equações lineares

através da factorização de matrizes em LU.

Os três Benchmarks Linpack são:

- Linpack 100x100 não está permitida a optimização do programa linpack.

- Linpack 1000x1000 pode ser optimizado utilizando as bibliotecas do

vendedor.

- Linpack NxN de forma a que a dimensão tire o maior partido do

processador.

6

Explique resumidamente os dois benchmarks da SPEC.

O SPEC 95 fornece a medida da performance em computação intensiva do

processador, hierarquia de memória e componentes do compilador de um computador

para fins comparativos.

SPEC CINT95 um conjunto de 8 benchmarks de inteiros intensivos e sem

vírgula flutuante.

SPEC CFP95 um conjunto de 10 benchmarks de vírgula flutuante.

Podemos definir a performance de uma máquina como P =f*n onde f é a

frequência do relógio e n o número de instruções em cada ciclo de relógio. Então,

porque é que necessitamos de benchmarks?

Os benchmarks servem para verificar a performance de uma máquina quando

corre um determinado software e não a performance da máquina enquanto hardware.

Qual a principal diferença entre Linpack e SPEC?

A principal diferença é que enquanto o Linpack mede a performance mais ao nível do

processador, a SPEC mede a performance em todo o sistema, desde o processador,

passando pelos vários tipos de memória, até ao disco rígido. Deste modo, não basta ter

somente um bom processador é também necessário, memórias e discos com tempo de

acessos mínimos.

Benchmarks:

O objectivo dos benchmarks é medir a performance do processador na

computação intensiva, assim como a performance da hierarquia de memória e dos

componentes do compilador, num dado sistema de computação, de modo a fazer

posteriores comparações. Ou seja, benchmarks são testes que têm por objectivo avaliar

as máquinas a nível de performances. São testes feitos com aplicações reais. Estas

aplicações reais podem ser:

- 100% matemáticas: ex. Linpack (álgebra linear), BLAS (biblioteca)

- Aplicações mistas: uma parte em vírgula flutuante, mas a maioria é inteira (ex.

SPEC – conjunto de subrotinas).

Linpack vs SPEC

Linpack

O Linpack é um pacote de software (bibliotecas) para utilizar vectores e

matrizes. Os programa Linpack podem ser caracterizados como programas que têm uma

elevada percentagem de operações aritméticas em vírgula flutuante. As operações são

em vírgula flutuante. Têm por objectivo a resolução de sistemas de equações lineares

através da decomposição LU com pivotação parcial.

Tipos:

- 100x100 incógnitas - serve para ordenação de todos os sistemas testados. A

ordenação é sem optimização do software.

- 1000x1000 incógnitas – informação adicional com optimização.

7

- NxN – medir qual o pico de performance de uma máquina.

Rpeak (performance teórica) = N (nº de processadores) * f (ciclos de relógio)

* I (issuing dual quad)

Os programas podem ser caracterizados como programas que têm uma elevada

percentagem de operações aritméticas em vírgula flutuante.

Tem fins lucrativos. Testam a memória e o poder matemático.

SPEC:

A SPEC utiliza uma máquina de referência. A rapidez da máquina é comparada

com a máquina de referência.

Não tem fins lucrativos. Testam o poder matemático e as máquinas. São

aplicações reais. Testam jogos, programas e compilação.

SPECint95 – 8 programas benchmarks com operações inteiras:

- 099.go jogo, inteligência artificial;

- 124.m88ksim simulação;

- 126.gcc programação e compilação;

- 129.compress compressão;

- 130.li interpretador, tradutor, linguagem;

- 132.ijpeg imagem, tratamento e compressão;

- 134.perl manipulação de texto e números;

- 147.vortex construção e manipulação de Bases de Dados;

SPECfp95 – 10 programas com operações com vírgula flutuante

- 101.tamcatu tradução geométrica, dinâmica de fluídos;

- 102.sulin pressão do tempo, resolve equações usando aproximações;

- 103.suzcor física quântica (utilização da teoria Q.G. para computação de

massa);

- 104.hydrozd astrofísica (cálculo de jacto galácticos);

- 107.mgrid electromagnetismo (cálculo de um campo em 3D);

- 110.applu matemática (resolve sistemas de matrizes com pivotação);

- 125.twb3D simulação;

- 141.apsi precisão do tempo (estatística da temperatura);

- 145.fpppp química (derivativas de multi-electrões);

- 146.wave electromagnética (resolução de equações de Maxwell).

Métrica (categorias):

Inteiros vs Floating-point

Conservativa vs Agressiva

Velocidade vs Número de operação

8

Temos então as seguintes métricas compostas:

Speed

SPECint

Agre

ssiva

95

Throughput

SPECint_rate

95

SPECfl9

SPECfl_rate9

5

5

cons

SPECint

SPECint_rate

ervativa

_base95

_base95

SPECfl_

SPECfl_rate_

base95

base95

Explique a hierarquia da memória, utilizando, como exemplo, um dos

microprocessadores mais potentes do mercado.

Tamanho/Capacidade

Registo

s

Cache

Memória principal

Memória secundária

Velocidade

Reg

+

*

MB

MB

Registos

Cache

(HP PA 8000)

Memória principal

512 MB

Memória secundária

512 MB

Fig.9

Quais os microprocessadores mais potentes no mercado?

- Mips R10K

- Dec Alpha

- HP PA 8000

- 1860

Explique o pipelining dentro do chip 8086.

busca

espera

Executa

busca

busca

executa

Leitura de

dados

executa

Como há um salto as

instruções que já estavam na fila

são apagadas.

busca

espera

busca

executa

Busca

Espera

Fig.10

9

Porque é que um chip DEC Alpha tem uma Branch History Table?

Para guardar a informação dos saltos calculados através do processo de “Branch

Prediction” numa execução “Out-of-order”. Como se trata de um processador pipelining

e superescalar esta “Branch History Table” permite aumentar a sua performance pois

trata o salto de forma a não bloquear o pipelining.

Explique a execução “Out-of-order”.

É a execução de instruções fora de ordem, utilizando o processo de “Branch

Prediction” e de dependência de instruções. Numa máquina superescalar “Out-of-order”

cada instrução é legível para começar a execução logo que os seus operandos se tornem

disponíveis indiferentemente da sequência original das instruções. O hardware rearranja

as instruções de forma a manter as várias unidades de execução ocupadas.

Explicar o princípio de pipelining na adição em vírgula flutuante.

adder

Compara expoentes

shifter

Alinha mantissas e

compara expoentes

adder

Soma

mantissas

adder - shifter

Normaliza resultado

Fig.11

1º Compara os expoentes é feita a subtracção dos expoentes.

2 º Alinha mantissas e iguala expoentes um fixed-point adder identifica o

expoente mais pequeno cuja mantissa pode ser modificada para formar uma nova

mantissa Xn, ficando (Xn,Ye) = (Xn,Xe).

3º Somar as mantissas as mantissas Xn e Yn, agora alinhadas, são

somadas. Esta soma dos n fixed-point pode produzir um resultado não normalizado.

4º Normalizar o resultado contando o número K dos primeiros zeros da

mantissa trocando as posições dos dígitos da mantissa para normalizá-la, fazendo o

correspondente ajuste no expoente.

Sem utilizar o pipelining teríamos, para um registo de 64 bits, 64*4=256 ciclos,

com o pipelining vamos ter 64+3=67 ciclos.

Um chip Dec Alpha, com um consumo de 30W, uma voltagem de 3.3 volts, e

uma velocidade de 200 Mhz, tem 431 pinos. Destes pinos, 140 são para a fonte de

alimentação. Porquê 140 em vez de apenas 2?

Quando se dá um aumento ou diminuição de utilização do processador, a energia

necessária aumenta ou diminui, levando à necessidade de um aumento ou diminuição

dos pinos a serem utilizados. Poderiam ser dois pinos mas para poderem alimentar todo

o chip sem se dar um sobre-aquecimento teriam de ser pinos maiores.

10

In Order

Múltiplas instruções são “fetched” em cada ciclo. O servidor consecutivo de

instruções permite que estas possam ser executadas ao mesmo tempo se os operadores

estiverem válidos. Senão, o processador “stalls” em qualquer instrução com operandos

não válidos.

A execução Out-of-Order

Num processador com execução “in-order”, cada instrução depende da instrução

anterior a qual produziu o seu operando. A execução não pode ter início até que esses

operandos se tornem válidos. Se os operandos não forem válidos, devido à exigência da

execução “in-order”, o “stall” normalmente atrasa todas as instruções subsequentes.

Numa máquina superescalar assim que os operandos estejam disponíveis, o

hardware encarrega-se de re-arranjar as instruções ocupadas. Este processo é designado

chamamento (endereçamento) dinâmica.

Registos Flag Registam excepções: precisão, overflow,underflow, zero

divide, operando desnormalizado, operações inválidas.

Program Counter Contém a nova posição onde vamos encontrar a nova

instrução.

Instrução Queue Fila com instruções para serem descodificadas.

Registos de segmentação Servem para facilitar a programação.

Paralelismo Permite aos CPU’s trabalhar com blocos de memória diferentes

ao mesmo tempo.

Problema do Prefetcher:

Quando chega a um salto (jump) e o CPU ainda não chegou lá.

Problemas:

1) Funciona através do sistema operativo.

2) Funciona em pacotes.

Provoca atrasos.

Soluções:

1) Salta aleatoriamente para cima ou continua.

2) Espera pelo CPU até que ele execute o salto (jump).

Prefetching:

O prefetching de instruções é uma técnica onde o processador pode requisitar

um bloco de cache antes do momento em que seria realmente necessário. Esta técnica

permite ao compilador antecipar-se à necessidade de um bloco de instruções,

colocando-os o mais perto possível do CPU.

Como funciona?

1º- O compilador assume que serão necessárias mais instruções do que aquelas que

constam na cache interna.

11

2º- Envia uma mensagem ao prefetcher que vai buscar um novo conjunto de instruções

colocando-as na cache secundária.

3º- Se o processador pedir a nova sequência, este, como está na cache secundária, é

mais rapidamente encontrado pelo processador. Caso o processador não necessite desse

bloco, a área da cache L2 ocupada com essas instruções é rescrita com novas instruções.

Microprocessador R10000

Fig.12 - Esquema R10000

Sec. Cache

control

MS interface

Instruções da

cache

32 KB

TLB

Adder

query

Instruction decode register mapping

Branch

unity

Data cache

32 KB

Cache

secundária

512-16 M

64 int

regs

Adder calc

ALU1

Int query

ALU2

Fp query

64 fp

regs

+

*

O microprocessador R10K tem uma arquitectura superescalar que procura e descodifica

4 instruções por ciclo. Cada instrução descodificada é anexada a uma das 3 filas

(inteiros, vírgula flutuante e endereços) de espera de instruções. Cada fila é capaz de

realizar uma gestão dinâmica de instruções. As filas determinam a ordem de execução

baseadas na disponibilidade das unidades de execução requeridas. As instruções são

inicialmente “buscadas” e descodificadas por ordem mas podem ser executadas e

completadas “out of order”, permitindo ao processador ter mais de 32 instruções em

vários estados de execução. A impressionante performance de cálculo de inteiros e

floating-points faz do R10000 o processador ideal para aplicações tais como engenharia

de workstations, computação científica, gráficos 3D em workstations, servidores de

bases de dadose sistemas multi-usos. Um elevado throughput é alcançado através do

vasto uso e dedicados data paths e um elevado número de in e off chip caches.

Em resumo:

- arquitectura superescalar;

12

- procura e descodifica 4 instruções por ciclo;

- gestão dinâmica de instruções;

- execução “out-of-order”;

- elevada performance no cálculo de inteiros e floating-points;

- elevado throughput (vasto uso de data paths );

- elevado número de on e off chip caches;

Branch Prediction

Os branches interrompem o fluxo de pipeline. Assim sendo, os esquemas de

branch prediction são necessários para minimizar o número de interrupções. Os

branches ocorrem frequentemente (em média um em cada 6 instruções).

A maioria dos branches predictions utilizam algoritmos que guardam o modo

como se comportou o último salto executado (numa Branch History), sendo em seguida

assumido que o novo salto comportar-se-à do mesmo modo. Se assim for, actualiza as

instruções no processador. Caso contrário, as instruções contidas na pipeline devem ser

abortadas. Muitas arquitecturas implementam uma branch stack a qual guarda os

endereços alternativos de um salto.

Explique o funcionamento da memória cache

A cache serve para medir a diferença entre os registos da memória principal.

A cache é dividida em sets que são controlados por pequenas memórias

associativas.

Os dados são acedidos através da comparação simultânea do endereço lógico ou

key do item que queremos procurar com o endereço de todos os items armazenados.

Os dados e os respectivos endereços lógicos são armazenados juntos.

O acesso a estas memórias é muito rápido devido ao uso de células de

armazenamento muito complexas.

Leitura:

1º- É gerado um endereço físico através do TLB que é apresentado à cache.

2º- O “Set Address” é descodificado e usado para seleccionar o conjunto

correcto na cache.

3º- Na cache o “Address tag” é comparado em simultâneo com o “set address”

das duas unidades seleccionadas no ponto anterior.

4º- Se há um “hit”, então a linha seleccionada e um dos sus bytes é marcado pelo

byte address.

5º- O conteúdo do byte é enviado ao CPU.

6º- Se há um “miss” a cache inicia um “swap” com a memória principal para um

“random” de duas candidatas disponíveis.

7º- Uma vez que a página está presente na cache, o pedido de leitura da memória

está completo.

Escrita:

1º- O endereço de memória é mapeado directamente para um conjunto, cujos

“address tag” são comparados com os “address field” do endereço.

2º- Se há um “hit” os novos dados são escritos na cache e ao mesmo tempo é

implementada uma política de actualização da memória principal.

13

3º- Quando ocorre um “miss” os dados são escritos directamente na memória

principal.

4º- O “write miss” não inicializa a memória principal.

From TLB

Address tag

Data Page Line

0

1

Set

. Address

.

.

9

18

3

Address decoding logic

0

511

Byte address

Address

comparisson

Data

selection

Fig.13

Como funciona um disco rígido, da camada magnética até ao bus.

Um disco rígido é semelhante a um disco de música, pode ser feito de alumínio

ou plástico e é coberto por uma fina camada magnética na sua superfície. Em cada face

do disco existem centenas de “tracks” dispostas de forma concêntrica. A informação é

guardada nos “tracks” da superfície magnética.

Para escrever informação a célula endereçada é colocada por baixo da indução

magnética, um pulso de corrente é então transmitido pela bobine que altera o campo

magnético da condução magnética, esta por sua vez altera o estado de magnetização da

célula que se encontra por baixo.

Para ler uma célula, esta desloca-se pela read/write head.

O campo magnético varia e induz um “electric pulse” na bobine de leitura.

Este pulso é depois enviado ao “sense amplifier” e identifica o estado da célula.

A ligação ao bus é feita através do controlador que adapta o interface natural dos

componentes ao standard imposto pelo bus.

14

Arm

Read/Write

Vista de cima

Fig.14

Vista de baixo

Paralelismo – permite aos CPU’s trabalhar com blocos de memória diferentes

ao mesmo tempo.

Registos de segmentação – servem para facilitar a programação.

Contador do programa – contém a nova posição onde vamos encontar a nova

instrução.

Registos flag – registam excepções: overflow, underflow, zeros, sinal negativo,

etc.

Branch-prediction – necessário para minimizar o número de interrupções no

pipeline.

Instrução Queue – fila com instruções para serem descodificadas.

RAM (Random-Access-Memory)

Uma unidade de memória é chamada RAM se qualquer local pode ser acedido

por uma operação de leitura ou escrita num determinado intervalo de tempo fixo, que é

independente do endereço da sua localização. As unidades M.P (memória principal) são

deste tipo. Isto distingue-as dos dispositivos de acesso e armazenamento tais como os

discos rígidos e as disquetes.

Memórias estáticas (SRAM)

Memórias que consistem em circuitos capazes de reter o seu estado tento tempo

quanto o tempo em que a energia é aplicada. São mais rápidas e mais caras.

Memórias dinâmicas (DRAM)

Não conseguem reter o seu estado indefinidamente. São mais baratas e são a

escolha predominante para a implementação da M.P. As altas densidades alcançáveis

com estes “chips” fazem com que as memórias maiores sejam mais económicas.

ROM (Read-Only-Memory)

Componente de controlo de armazenamento num CPU microprogramado.

Podem também ser usadas para implementar partes da M.P. de um computador que

15

contém programas ou dados fixos. Os dados são escritos na ROM aquando do seu

fabrico. No entanto, algumas ROM permitem ao utilizador carregar a informação,

passando assim a chamar-se PROM (programmable ROM) e fornecendo alguma

flexibilidade.

Por outro lado, temos ainda as EPROM´s (erasable reprogrammable ROM´s)

que permitem armazenar informação que pode ser apagada para que novos dados sejam

lá carregados. Dado que as EPROM’s são capazes de reter informação armazenada

durante muito tempo, podem substituir as ROM’s enquanto o software está a ser

concebido o que torna as actualizações e as alterações mais fáceis. Uma grande

desvantagem é que eles têm de ser fisicamente removidos para a reprogramação e o seu

conteúdo é totalmente apagado pela luz ultravioleta.

Existem ainda os EPROM’s ou E2PROM’s que não necessitam de ser removidos

para serem apagados. Podem ser apagados e reprogramados electricamente tendo

apenas a desvantagem de que são necessárias voltagens diferentes para apagar, escrever

e ler dados.

Memória Virtual e TLB

Na maioria dos modernos sistemas de computadores a memória física principal não é

tão grande como o endereço do espaço necessário por um endereço enviado pelo

processador. Quando um programa não cabe completamente na memória principal, as

partes que não estão a ser executadas são armazenadas em dispositivos de

armazenamento secundário, tais como discos magnéticos. É claro que todas as partes de

um programa que serão eventualmente executadas são antes disso trazidas para a

memória principal. Quando um novo segmento de um programa necessita de ser

colocado na M.P., deve substituir um outro segmento já constante em memória. Nos

computadores modernos, o sistema operativo encarrega-se disso.

As técnicas que automaticamente movem o programa e os blocos de dados para a

memória física (principal), quando assim é requerido, chamam-se técnicas de memória

virtual. Os programas e o processador referenciam uma instrução e o espaço de dados

que são independentes do espaço disponível na M.P. física. Os endereços binários que o

processador envia para instruções ou dados são chamados endereços lógicos ou virtuais.

Estes endereços são traduzidos para endereços físicos através de uma combinação de

componentes de hardware e software. Se um endereço virtual referencia uma parte do

programa ou dados que estão na M.P., então o conteúdo da área apropriada na M.P. é

acedida de imediato. Por outro lado, se o endereço referencia algo que não se encontra

na M.P., o seu conteúdo deve ser transferido para um local da memória para depois ser

utilizado.

Processador

endereço virtual

Data

MMU

endereço físico

Cache

Data

endereço físico

M.P.

DMA transfer

Disk Storage

MMU - Memory Management Unit

16

Fig.15

A unidade de hardware MMU traduz o endereço virtual para endereço físico. Quando os

dados pretendidos se encontram na M.P., esses dados são buscados tal como o

mecanismo da cache o descreve. Se os dados não estão na M.P., a MMU ordena ao

sistema operativo que traga os dados do disco para a M.P. utilizando para isso (o

sistema operativo) o esquema de DMA.

Translation lookaside

Bloco

bufferde

(TLB)

- contém parte do

mapa de memória

Bloco de

endereço

físico

Endereço

lógico

(virtual)

Memory map

.

.

.

Displacement

Endereço

físico

Secundary Memory (M2)

Fig.16

Main Memory (M1)

Tradução de endereços

Um método simples para traduzir endereços virtuais para endereços físicos é assumir

que cada programa e dados são compostos por unidades de comprimento fixo chamadas

páginas, constituindo cada uma um bloco de palavras que ocupam locais contínuos na

memória principal. As páginas variam entre 2K e os 16K de tamanho. Constituem a

unidade básica de informação que é movida entre a M.P. e o disco quando o mecanismo

de tradução assim o requer e é necessário. As páginas não devem ser nem demasiado

pequenas nem demasiado grandes.

A cache é a ponte entre o processador e a M.P e tem como função diminuir a quebra ou

aumento vertiginoso da velocidade e é implementada em hardware. Por seu lado, a

memória virtual permite minimizar as quebras de tamanho e velocidade entre a M.P. e a

M.S. e é usualmente implementada em parte por técnicas de software. Conceptualmente

a M.P. e a cache são similares diferindo basicamente em detalhes de implementação.

O processo de tradução actua do seguinte modo:

Cada endereço virtual gerado pelo processador, quer seja uma instrução de busca ou um

operando da operação de busca/armazenamento, é interpretado como um endereço

virtual de uma página seguido de um “offset” que especifica a localização de um byte

de palavra específicos na página. A informação acerca da localização de cada página na

M.P. é guardada numa tabela de páginas. Esta informação inclui o endereço na M.P.

onde a página está armazenada e o corrente “status” dessa página. Uma área na M.P.

que pode conter uma página é chamada de page “frame”. O endereço inicial da tabela de

17

páginas é guardado numa “page table” base “register”. Através da adição do número da

página virtual com o conteúdo deste registo, o endereço da correspondente entrada na

tabela de páginas é obtido. O conteúdo deste local dá-nos o endereço inicial da página

se ela estiver correntemente na M.P.

Cada entrada na tabela de páginas também inclui alguns bits de controle que descrevem

o “status” da página enquanto está na M.P.

Um bit indica a validade da página ( se se encontra ou não na M.P.). Outro bit indica se

a página foi ou não modificada enquanto esteve na M.P. Tal como na cache, esta

informação serve para determinar se a página deve ser rescrita na M.S. antes de ser

removida da M.P. para dar lugar a outra. Outros bits de controle indicam várias

restrições que podem ser impostas no acesso à página.

A tabela de páginas é usada pela MMU em cada acesso de leitura e escrita, por isso, o

ideal seria que estivesse incorporada dentro do MMU. No entanto isso não é possível

devido ao seu tamanho e visto que o MMU é incorporado no “chip”. Assim sendo, a

tabela de páginas é mantida na M.P. No entanto, uma cópia de uma pequena parte dela

pode ser acomodada no MMU. Esta parte consiste numa tabela de páginas cujas

entradas correspondem às páginas mais recentemente anexadas. Uma pequena cache,

usualmente chamada de “translation lookaside buffer” (TLB), é incorporada no MMU

com este propósito. O modo de operar da TLB é semelhante ao da cache. Em adição à

informação que constitui a entrada na tabela de páginas, a TLB deve também incluir o

endereço virtual dessa entrada.

Um requisito fundamental é que o conteúdo da TLB seja coerente com o conteúdo das

tabelas de páginas em memória. Quando o sistema operativo muda o conteúdo das

tabelas de páginas, deve simultaneamente invalidar a correspondente entrada na TLB.

Um dos bits de controlo da TLB tem esta função. Quando uma entrada é invalidada, a

TLB irá adquirir a nova informação.

A tradução de endereços funciona do seguinte modo:

Dado um endereço virtual, o MMU procura no TLB a página referenciada. Se a entrada

desta página for encontrada na TLB, o endereço físico é obtido da tabela de páginas na

M.P. e a TLB é alterada.

Quando um programa gera o pedido de acesso a uma página que não está na M.P. dá-se

um “page fault”. Toda a página deve ser trazida do disco para a M.P. antes de se

proceder ao seu acesso. Quando é detectado com “page fault”, o MMU pede ao sistema

operativo para intervir criando uma excepção (interrupção). O processamento da tarefa

actual é interrompido e o controlo é transferido para o sistema operativo. O sistema

operativo copia então a página pedida do disco para a M.P. e retoma o controlo à tarefa

interrompida. Devido à demora da transferência da página, o sistema operativo pode

suspender a execução da tarefa em curso e iniciar a execução de outra tarefa cujas

páginas estão na M.P.

É essencial assegurar que a tarefa interrompida possa continuar correctamente quando

retoma a execução.

Se a nova página é trazida do disco quando a memória principal está cheia, deve-se

substituir uma das páginas residentes. Coloca-se aqui o problema da escolha de qual a

página que deverá ser substituída. Existem diversas formas de resolver o problema,

baseando-se algumas delas no conceito do algoritmo LRU de substituição em conjunto

com os bits de controlo.

Uma página modificada tem de ser escrita no disco antes de ser removida da M.P. É

importante notar que o protocolo “write-through” não se adapta à memória virtual. O

tempo de acesso é tão grande que não faz sentido aceder frequentemente ao disco para

escrever pequenas partes de dados.

18

O processo de tradução do MMU requer algum tempo para ser efectuado, sendo a sua

maioria utilizada para acessos à TLB. Podemos reduzir a média de tempo de traduções

através da inclusão de um ou mais registos especiais que retêm o número da página

virtual e o “page frame” físico das mais recentes traduções feitas. A informação nestes

registos pode ser mais rapidamente acedida.

Região do Programa

TLB

Região da stack de

controlo

Endereço pág. virtual

Memória

de

processamento

(utilizador)

endereço

virtual

Tabela de pág.

offset

endereço

físico

Memória do

sistema

Page table

Base register

(SBR)

Memória principal

Fig.17 - Método de tradução de endereços no VAX-11

Descreva brevemente a tradução do endereço lógico para o endereço físico da

memória virtual ( utilizando o exemplo do VAX-11).

Processo:

1) A CPU verifica se a entrada para determinado endereço lógico se encontra no

TLB.

2) Se sim:

- Constitui o endereço físico somando o valor do deslocamento (offset)

com o campo do endereço físico.

3) Se não:

- O endereço lógico é somado ao conteúdo do SBR, obtendo assim o endereço

físico absoluto da entrada que contém a tradução do endereço virtual.

- Todo o bloco é copiado para o TLB no caso de haver necessidade de o

utilizar novamente (bloco=32 entradas).

Explique o funcionamento da memória virtual e o TLB.

A figura mostra os principais componentes do sistema de memória virtual e as suas

interconecções lógicas. O endereço físico atribuído a cada bloco de informação está

guardado num conjunto de tabelas chamado mapa de memória (memory map). Este

mapa é usado para traduzir blocos de endereços lógicos em endereços físicos.

19

O endereço lógico inclui o deslocamento (displacement) que é, tipicamente, o

endereçamento efectivo computado de acordo com o modo de endereçamento definido

pelo programa, para que o item da memória seja acedido.

Para aumentar a velocidade do processo de tradução de endereços, uma parte do mapa

de memória é colocado numa memória de alta velocidade localizada no CPU, o TLB. O

TLB é um tipo especial de cache, cujo input é um endereço virtual e o output é o

endereço físico correspondente. Se o endereço lógico corrente não está atribuído ao

TLB, a parte do mapa de memória que contém o endereço lógico corrente é transferido

da memória principal para o TLB. O conteúdo do TLB varia dinamicamente durante a

execução do programa.

Quais são as razões para introduzir a hierarquia de memória (cache e virtual)?

Razões para utilizar a memória virtual:

- Libertar os programadores da necessidade de realizar opções de alocação de

espaço de armazenamento e permitir uma partilha eficiente do espaço de

memória por entre diferentes utilizadores.

- Tornar os programas independentes da configuração e capacidade dos

sistemas de memória usados durante a sua execução.

- Alcançar altas taxas de acesso a baixo custo por bit e que isto seja possível

com uma hierarquia de memória.

- O grande objectivo numa hierarquia de memória é alcançar uma

performance próxima da unidade de U1 mais rápida e o custo por bit

próximo ao da unidade Un mais barata.

- O objectivo que se pretende ao adicionar memória cache a um computador é

fazer com que o tempo médio de acesso à memória pelo processador seja o

mais próximo possível do da cache. Para isso a cache deve satisfazer uma

alta percentagem de todas as referências à memória.

Política de troca de páginas.

O principal objectivo na escolha de uma política de substituição é minimizar o número

de vezes que um bloco referenciado não está na M.P., uma condição chamada “memory

fault”.

FiFo (First in First out) – selecciona por substituição o bloco menos recente carregado

na memória, ou seja, o que está na fila à mais tempo (o primeiro a ter entrado).

Vantagem: fácil de implementar.

Desvantagem: substitui blocos que são frequentemente utilizados.

LRU (Last Recently Used) – selecciona por substituição o bloco que foi menos

recentemente utilizado pelo processador.

Vantagem: não substitui blocos frequentemente utilizados.

Desvantagem: é mais difícil de implementar.

Alguns computadores como o VAX-11 utilizam uma política de troca de páginas

“Random”. A página a ser substituída é seleccionada por um processo rápido que se

aproxima verdadeiramente à selecção aleatória, não utilizando para isto, nenhum dado

referenciado na linha da cache.

Existem outras políticas de optimização que variam consoante o propósito requerido e

as características do programa e sistema.

20

Cache:

Uma forma de reduzir o tempo de acesso à memória é usando a memória cache. Ela é

uma memória pequena e rápida que é inserida entre a memória principal e o

processador.

A cache é a ponte entre o processador e a M.P. e tem como função diminuir a quebra ou

o aumento vertiginoso de velocidade. A cache é implementada em “hardware”. A cache

comporta os segmentos activos actualmente do programa. A eficiência da cache baseiase na propriedade de referência de localização:

- Temporal: as instruções mais recentemente executadas são provavelmente

executadas novamente em breve.

- Espacial: as instruções nas proximidades das instruções mais recentemente

executadas serão provavelmente executads em breve.

Quando um item é primeiramente requisitado, ele será trazido até à cache onde

permanecerá na esperança de ser utilizado em breve. Nesta transacção será trazido, não

só o item, mas também todo o bloco no qual se insere, assim como os seus endereços.

Quando a cache está cheia e uma instrução é requisitada, esta não aparece na cache, o

controlo da cache deve decidir qual o bloco a ser removido para criar espaço para o

novo bloco.

Como opera a cache?

1- O CPU requisita determinados itens utilizando endereços.

2- O circuito de controlo da cache determina se o pedido do CPU se

encontra ou não na cache. Utilizam-se as funções de mapeamento.

3- Se sim:

3.1- A operação de leitura ou escrita é efectuada no local aproximado da

cache. Neste caso diz-se que ocorreu um acerto (hit) de leitura ou escrita. Na

operação de leitura a M.P. não é envolvida. Na operação de escrita o sistema

pode proceder de 2 formas:

- Técnica “write-trhough” a localização na cache e na memória principal

são actualizadas simultaneamente. O VAX-11 utiliza esta técnica.

- Técnica “write-back” actualiza-se apenas a localização na cache e para

indicar que houve uma actualização utiliza-se uma mensagem chamada

“dirty” ou “modified bit”. A memória principal é actualizada quando o bloco

associado à palavra marcada for removido da cache para dar lugar a um novo

bloco.

Ambas as técnicas podem originar operações desnecessárias.

4- Se não:

4.1- Se a operação é de leitura e não se encontra na cache, ocorre um “read

miss”. O bloco que contém a palavra requerida é copiado da memória

principal para a cache. Pode ser necessário usar uma das políticas de troca de

páginas (“O VAX-11 é Random”). Após este carregamento a palavra em

questão é levada até ao CPU. Alternativamente, esta palavra pode ser

enviada para o CPU assim que for lida a M.P. Este método chama-se “loadthrough”.

21

4.2- Se a operação é de escrita, ocorre um “write miss”. Se estiver a ser

usado o “write through”, a informação é escrita directamente na memória

principal (o que acontece com o VAX-11). Se estiver a ser usado o “write

back”, o bloco contendo a palavra é trazido à cache, sendo depois a palavra

desejada rescrita com a nova informação.

Funções de mapeamento da cache:

Direct-Mapped Cache: Um bloco de memória só pode ser colocado num

bloco de cache específico. Para achar o bloco: bloco cache = bloco M.P. mod

m+1 (total de blocos de cache).

Endereço:

5

7

4

tag

block

word

tag – Bits associados à localização na cache.

block – Posição na cache na qual deve ser colocado.

word – selecciona uma das palavras do bloco.

1- Comparam-se os 5 bits mais significativos da palavra com a “tag”.

2- Se coincidir, então a palavra encontra-se nesse bloco.

3- Senão, o bloco deve ser lido da M.P. e carregado na cache.

Associative-Mapped Cache: Um bloco da M.P. pode ser colocado em

qualquer bloco da cache.

Endereço:

12

tag

4

word

1- Comparam-se os 12 bits mais significativos da palavra com a “tag”.

2- Se coincidir, então a palavra encontra-se nesse bloco.

3- Senão, o bloco deve ser lido da M.P. e carregado na cache.

Set Associative-Mapped Cache: Combinação das duas técnicas anteriores. Os

blocos da cache são agrupados em conjuntos (“sets”) e o mapeamento permite a

um bloco da memória principal residir em qualquer bloco de um conjunto

especificado.

Endereço:

5

7

7

tag

set

word

1- Compara-se o campo “set” de modo a determinar o “set” que contém o bloco

desejado.

2- Comparam-se os 6 bits mais significativos da palavra com a “tag”. A “tag”

deve ser comparada associativamente com o “tag field” do endereço, isto é,

com o “set” determinado.

22

3- Se coincidir, então a palavra encontra-se nesse bloco.

4- Senão, um novo bloco deve ser trazido da memória principal.

Cache Set-Associative no VAX-11:

Leitura:

1- É gerado um endereço físico através do TLB que é apresentado à cache.

2- O “set address” é descodificado e usado directamente para seleccionar o

conjunto correcto na cache.

3- A “tag” é comparada em simultâneo com as linhas seleccionadas

anteriormente.

4- Se há um “hit” então a linha é seleccionada e um dos seus “bytes” é marcado

pelo ”byte address”. O conteúdo do byte seleccionado é enviado à CPU.

5- Se há um “miss”, a cache inicia um “swap” com a memória principal para

trazer os dados desejados para a cache. A linha a ser substituída é

seleccionada aleatoriamente fazendo o “Random” de 2 linhas candidatas

disponíveis.

6- Uma vez que a página esteja presente na cache, o pedido de leitura da

memória está completo.

Escrita:

1- O endereço de memória é mapeado directamente para um conjunto cujos

“tags” são comparados associativamente com o “tag” do endereço.

2- Se há um “hit” os novos dados são escritos directamente na cache, ao mesmo

tempo que na memória principal.

3- Quando ocorre um “miss” os dados são escritos directamente na memória

principal.

From TLB

data page line

set address

0

Address decoding logic

Address tag

9

a

18

3

c

511

0

1

7

b

Address

comparisso

n

Data

selection

23

a) set address b) cache address tag c) byte address

Fig.18 - Organização da cache VAX-11

Como vê um utilizador a cache?

Uma hierarquia de memória é transparente quer para o programador de aplicação

quer para o programador de sistemas.

Alguns computadores, como o VAX-11, têm uma cache que utiliza política de

troca de páginas, “Random”. A página a ser substituída é seleccionada por um processo

rápido que se aproxima verdadeiramente à selecção “Random”, não utilizando, para

isto, nenhum dado referenciado na linha da cache.

Quais são as vantagens e as desvantagens das técnicas “write-through” e

“write-back”?

Write-back actualiza-se apenas a localização na cache e, para indicar que

houve uma actualização, utiliza-se uma “flag” chamada “dirty” ou “modified bit”.

Vantagens – A memória principal é actualizada quando o bloco associado à

palavra marcada for removido da cache para dar lugar a um novo bloco.

Desvantagens – a cache e memória principal podem estar inconsistentes, isto é,

podem ler dados, associados diferentes com o mesmo endereço físico. Isto leva a um

problema aquando da existência de vários processadores com caches independentes e

com uma memória principal comum. Esta técnica complica igualmente a recuperação de

falhas do sistema ou outras condições excepcionais.

Write-trough Transfere os dados para a cache e para a memória principal

durante todos os ciclos de escrita para a memória.

Vantagens: É facilmente implementada e garante que a memória principal nunca

contém informações obsoletas. É especialmente útil quando a memória principal é

partilhada por múltiplos processadores.

Desvantagens: Aumenta o número de escritas para a memória principal. Como o

tempo requerido para cada operação de escrita na memória principal é maior que o

requerido para a cache, a performance do processador pode ser afectada.

Qual o problema da utilização da cache num sistema multiprocessador

“shared memory”? Quais as soluções?

O problema surge quando vários processadores com caches independentes

partilham a mesma memória principal. A utilização de uma estratégia “write-back”

levaria a uma possível inconsistência de dados da dados da cache e da memória

principal.

Uma solução seria a utilização de uma estratégia “write-trough” que elimina a

inconsistência dos dados.

Porque tem a cache uma memória associativa?

Um endereço A que é apresentado à cache pelo processador pode ser comparado

com todos os endereços armazenados na cache para determinar se A se encontra ou não

nela. O processo de comparar A com todos os endereços é bastante lento. Criou-se

assim um compromisso entre a velocidade e o custo, que foi implementar o

24

armazenamento dos endereços como uma única memória associativa, a qual permite que

o endereço A seja comparado simultaneamente com todos os endereços do conjunto

associativo da cache. Para permitir a comparação em simultâneo dos endereços “tag”

associados a determinados “set address”.

Dispositivos de I/O:

Address lines

Data lines

Control lines

bus

Address

decoder

Circuitos de

controlo

Data and status

register

I/O interface

Input device

Fig.19 - Interface I/O para um dispositivo de entrada

Deve haver uma sincronização entre o processador e o dispositivo de entrada ou

saída. Para isso, o processador testa repetidamente a “flag de status” do dispositivo, no

caso de usar o método do “Program-Controlled” I/º Outros 2 mecanismos são usados

correntemente para implementar as operações de I/O: Interrupções e DMA (direc

memory access).

Com as interrupções, a sincronização é implementada através do envio pelo

dispositivo de I/O, de um sinal especial de interrupção para o bus assim que o

dispositivo está pronto para a operação de transferência de dados.

Nos DMA (técnica usada p/dispositivos de I/O de alta velocidade), o interface

transfere a informação directamente da e para a memória, sem um envovimento

continuo do processador.

Interrupções:

Em muitas situações, outras tarefas podem ser executadas enquanto o

processador espera que o dispositivo de I/O fique pronto para operar. Para fazer isto,

podemos arranjar um modo de um dispositivo alertar o processador quando está pronto.

Ele faz isso através do envio de um sinal de hardware chamado: interrupção do

processador. Pelo menos uma das linhas de controlo do bus (interrupt-request-line) é

dedicada a esta função. O processador pode pedir a um dispositivo de interface de I/O

para activar esta linha, assim que o dispositivo estiver pronto para a transferência de

dados. Assim sendo, visto que o processador não tem de estar constantemente a testar se

o dispositivo está pronto, fica livre para executar outras funções. Note-se que o

processador também deve informar o seu dispositivo que foi reconhecido, para que ele

possa remover o sinal de “interrupt-request”. O chamado sinal de “interruptacknowledge” serve este propósito.

25

Uma interrupção é mais do que um simples mecanismo para coordenação das

transferências de I/O. Em geral, as interrupções permitem transferir o controlo de um

programa para outro que será iniciado por um evento exterior ao computador.

Os interruptores são também usados em mútuas aplicações de controlo, nas

quais o processamento de certas rotinas deve ser coincidente, em termos de tempo, com

os acontecimentos exteriores. Este tipo de aplicações chamam-se: Aplicações com

processamento em tempo real.

Sequência de eventos no manuseamento de um pedido de interrupção de um

dispositivo:

1- O dispositivo cria um pedido de interrupção.

2- O processador interrompe o programa que estava a ser executado.

3- As interrupções são “incapacitadas” (desactivadas).

4- O dispositivo é informado de que o seu pedido foi reconhecido e, em

resposta, desactiva o sinal de pedido de interrupção.

5- A acção pedida é realizada pela rotina de serviço de interrupções.

6- A execução do programa interrompido é retomada, com as interrupções aptas

e activadas.

7- Muitos eventos podem causar interrupções. Não são apenas os pedidos dos

dispositivos que causam as interrupções. Todos esses eventos são chamados

de excepções. Assim sendo as interrupções dos I/O são uma das possíveis

excepções.

Outros tipos de excepções:

Recuperação de erros – se um erro ocorre, o controlo detecta-o e informa o

processador através de um interrupção. O próprio processador pode proceder a

uma interrupção se detectar algum erro.

“Debugging” – os “debbugers” incluídos no “software” de programação

utilizam excepções para fornecerem 2 importantes capacidades: o “tracemode” e

os “breakpoints”.

DMA:

Para transferir grandes blocos de informação a uma alta velocidade podemos

utilizar o DMA. O DMA é uma unidade de controlo especial que permite a transferência

de um bloco de informação directamente desde um dado dispositivo externo para a

memória principal sem a intervenção contínua do processador.

As transferências do DMA são efectuadas por um circuito de controlo associado

aos dispositivos de I/O, o controlador de DMA.

O DMA efectua as funções que, normalmente, seriam efectuadas pelo

processador no momento de aceder à memória. Para cada byte ou palavra transferida ele

deve providenciar o endereço na memória e todos os sinais de controlo da transferência.

Visto que ele tem de transferir blocos de dados, o controlador DMA deve incrementar

os endereços de memória apropriadamente para que os sucessivos bytes ou palavras

sejam colocados nos locais devidos.

Apesar do DMA transferir dados sem a intervenção do processador, a sua

operação deve estar sob o controlo de um programa executado pelo processador. Para

iniciar a transferência de blocos o processador envia as seguintes informações para o

controlador: o endereço inicial, o número de palavras no bloco, e a direcção da

transferência. Ao receber esta informação, o controlador DMA procede à transferência

26

requerida. Após o bloco ser totalmente transferido, o controlador informa o processador

através de um sinal de interrupção.

As operações de I/O são sempre realizadas pelo sistema operativo do

computador em resposta a um requisito de uma aplicação.

Ciclo de instruções

Ciclo do

CPU

Fetch

instruct

Decode

instruct

Fetch

operand

Execute

instruction

Store

result

interrup

breakpoint

DMA

Fig.20 – DMA e interrupções: os seus breakpoints durante um ciclo de instrução

Explique o funcionamento do DMA.

1234-

O CPU inicia o controlador DMA e o controlador disco

O controlador de discos envia um sinal de DMA request.

O DMA envia à CPU um sinal de “hold request”.

A CPU envia ao DMA um sinal de “hold acknowledge” e bloqueia os seus

“transceivers”.

5- O DMA envia ao controlador de discos um sinal de DMA “acknowledge”.

Envia ainda os sinais de “memoryRead” à memória (MRD) e o sinal de

IOWR (I/O write) ao controlador de discos.

Endereços

1)

Bus de dados

d

e

X

d

e

d

e

d

e

X

Controlador

DMA

CPU

3)

M.P.

Controlador

de discos

2)

4)

5)

MRD

d-dados

e-endereço

IOWR

27

Fig.21

Descreva brevemente o funcionamento de um controlador de interrupções,

se possível da Intel.

1- O “Data Ready” é usado pelo dispositivo de I/O para colocar uma palavra

dentro do “buffer” na porta ª

2- O 8255 gera automaticamente um sinal, numa outra linha de C, que pode ser

enviada ao dispositivo de I/O como o sinal “data acknowledge”.

3- Uma terceira linha de C gera um sinal de interrupção “interrupt request” que é

enviado ao CPU para indicar a presença de dados na porta .

4- Num sistema como o da Intel é utilizada a técnica “vectoring” que permite ao

dispositivo de I/O enviar conjuntamente com o pedido de interrupção o envio da rotina

que irá prestar serviço a essa interrupção:

- A CPU deve ter conhecimento da origem da interrupção e do endereço da

rotina.

- O contador do programa e outras informações sobre o estado do CPU são

dados como uma subrotina de chamamento.

- O contador do programa é carregado com o endereço do programa de serviço

de interrupção. A execução da rotina de interrupção continua até ser encontrada

uma instrução de retorno, que transfere o controlo de volta ao programa

interrompido.

Data bus

8

A

8

data

data ready

C

data acknowledge

I/O device

A0

A1

read

write

B

interrupt request

Fig.22- Funcionamento de um controlador de interrupções (Intel)

Explique o funcionamento de um terminal.

Video Display

unity

Microcomputador

local

I/O interface

circuit

Modem

Teclado

Vários dispositivos de I/O, como teclados, ecrãs e impressoras, formam o

interface humano do terminal. Estes estão conectados através de um interface

28

apropriado com um micro-computador que controla o “software” (este controlo

determina a inteligência do terminal). Interfaces especializados para a comunicação

intersistema fornecem a ligação entre o terminal e o computador remoto.

Particularmente útil para este fim, é o controlador de comunicação de dados UART, um

dispositivo do ULSI que pode ser programado para acomodar uma variedade de

diferentes protocolos de transmissão de dados e velocidade de operação.

Componentes necessários para realizar uma placa de gestão do teclado e monitor:

Teclado é composto por uma matriz com os códigos ascii, PPI (para gestão

do teclado).

Monitor

deflecções

canhão

deflecções

aceleração

electrão

+

V

-

+

Fig.23

Interleaving Uma das formas de reduzir o tempo de acesso à memória. Ela divide o

sistema em vários módulos de memória e ordena o endereçamento em diferentes

módulos. Se os pedidos de acesso à memória tendem a envolver endereços consecutivos

então os acessos irão estar em diferentes módulos. Visto que o acesso paralelo a estes

módulos é possível, a taxa média de busca de palavras da memória principal pode ser

aumentada.

29