Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

METODOLOGIA DE PROJETO PARA CONVERSOR CC-CA ZVT PWM

Tiago Dequigiovani∗, Carlos Marcelo de Oliveira Stein∗

∗

Universidade Tecnológica Federal do Paraná - UTFPR

Via do Conhecimento, km 1, 85503-390 - Pato Branco, PR, Brasil

Emails: [email protected], [email protected]

Abstract— This paper presents a design methodology for a DC-AC converter using a ZVT cell. The used

auxiliary circuit provides soft-switching in both switches, main and auxiliary, and reduces the reverse recovery

losses in main diode. The project is based on six proposed restrictions that ensure soft-switching in switches in

keeping the losses at auxiliary circuit in low levels. Experimental results are presented with the application of

design methodology in a prototype 1 kW and 40 kHz. To evaluate the performance of this converter are also

implemented the auxiliary circuit, conventional ZVT and the Undeland snubber. Results show better efficiency

of proposed converter compared to other structures analyzed.

Keywords—

Active snubber cells, DC-AC converter, soft-switching, zero voltage transition.

Resumo— Este artigo apresenta uma metodologia de projeto para um conversor CC-CA utilizando uma

célula ZVT. O circuito auxiliar empregado proporciona comutação suave em ambos os interruptores, principal

e auxiliar, além de reduzir as perdas sob recuperação reversa no diodo principal. O projeto é baseado em seis

restrições propostas que asseguram a comutação suave nos interruptores mantendo as perdas no circuito auxiliar

em nı́veis reduzidos. São apresentados resultados experimentais com a aplicação da metodologia de projeto em

um protótipo de 1 kW e 40 kHz. Para avaliar o desempenho deste conversor são implementados também os

circuitos auxiliares ZVT convencional e o snubber de Undeland. Resultados mostram melhor rendimento do

conversor proposto em relação às outras estruturas analisadas.

Palavras-chave—

1

Snubber ativo, Conversor CC-CA, comutação suave, transição em zero de tensão.

ave (ZVS) para o interruptor principal e também

auxı́lio à comutação para a chave auxiliar (pseudoZVS), dessa forma minimizando o problema do

bloqueio dissipativo na chave auxiliar existente

na topologia ZVT convencional. Essa célula ZVT

inicialmente aplicada à conversores CC-CC é empregada neste trabalho em um conversor CC-CA

ponte completa.

Neste artigo é apresentada uma metodologia

para o projeto dos elementos do circuito auxiliar,

para atender as restrições de funcionamento e reduzir as perdas na comutação dos semicondutores. Para a validação do projeto um conversor

é implementado e analisadas as formas de onda

e a curva de rendimento. O desempenho deste

conversor é comparado com a implementação do

conversor ZVT convencional e outro dissipativo,

utilizando o snubber de Undeland.

Introdução

Diante da crescente necessidade pela melhoria da

eficiência no processamento de energia elétrica, os

conversores são projetados para operar com alta

frequência de chaveamento dos interruptores, isso

apresenta como vantagem o aumento na densidade

de potência do circuito, redução de volume, peso

e possivelmente de custo, além da simplicidade no

controle e rápida resposta dinâmica.

No entanto, com a elevação da frequência

de chaveamento, também aumentam as perdas

por comutação, as derivadas de tensão e corrente e a geração de interferência eletromagnética

(EMI). Esses problemas associados à elevação da

frequência podem ser minimizados com a utilização de técnicas de auxı́lio à comutação, proporcionando elevado rendimento do conversor e, adicionalmente, redução da di/dt e dv/dt nos semicondutores.

O circuito para auxı́lio à comutação empregado neste trabalho faz parte da famı́lia ZVT, proposto por Hua et al. (1992), no qual não contém

elementos em série com o circuito de potência do

conversor. A célula ZVT é ativada somente durante os intervalos de transição dos interruptores,

assim o conversor opera com comutação suave enquanto mantém as vantagens do conversor PWM.

Este circuito proposto por Hua et al. (1992), denominado neste trabalho como ZVT convencional,

realiza comutação suave ao interruptor principal,

porém o bloqueio da chave auxiliar é dissipativo.

Em Bodur and Faruk Bakan (2002) é proposta uma célula ZVT que realiza comutação su-

2

Etapas de Funcionamento

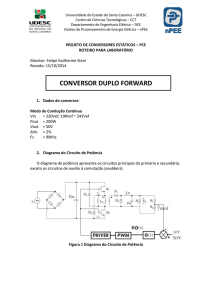

O circuito ZVT aplicado a um pólo PWM bidirecional é mostrado na Figura 1. A descrição das

etapas de operação são apresentadas considerando

o conversor operando no semiciclo positivo (corrente entrando no pólo PWM) e no instante de

pico da corrente de carga nominal (Iop ).

A Figura 2 mostra as principais formas de

onda teóricas e na Figura 3 são destacados os elementos ativos durante cada etapa de operação.

O funcionamento descrito é similar aquele apresentado em (Zhu and Ding, 1999; Bodur and Faruk Bakan, 2002; Russi et al., 2005), ambos para

um conversor boost.

523

Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

+E

Cb2

S3

D3

Sx1

Estágio 2 (t1 < t ≤ t2 ): A corrente em Lr2

continua aumentando devido à ressonância com o

capacitor Cr . Esta etapa termina em t2 onde a

corrente no indutor assume o seu valor máximo e

a tensão em Cr é igual a zero, isso ocorre em 1/4

do perı́odo de ressonância. O tempo de duração

do estágio (∆t2 ) e a corrente máxima no indutor

(ILr2(max) ) são definidas pelas expressões 2 e 3.

D22

+

Lr2

Iop

D12

Lr1

Cb1

S4

+

D11

Sx2

+

D4

Cr

0V

D21

Figura 1: Célula ZVT aplicada ao pólo PWM

Comando S4

t

iD3

Iop

t

Iop

(Iop-iCr)

iLr2

iD22

t

iS4

Iop

t

vCr

E

vCb2

(3)

Estágio 5 (t4 < t ≤ t5 ): Dependendo do valor projetado para o capacitor Cb2 , apenas uma

parcela da energia armazenada em Lr2 é necessária para carregar Cb2 até a tensão E, desta forma

o restante da energia é transferida para a entrada

através da condução do diodo D22 . Possuindo o

indutor, no instante t4 , corrente maior do que Iop ,

o diodo D4 torna a conduzir. Esta etapa termina

quando a corrente no indutor é igual a Iop e o

diodo D4 é bloqueado.

Estágio 6 (t5 < t ≤ t6 ): Durante esta etapa

continua a devolução da energia armazenada em

Lr2 para a entrada, através da chave principal.

O estágio termina quando a corrente no indutor

chega a zero.

Estágio 7 (t6 < t ≤ t7 ): Durante esta etapa o

interruptor S4 conduz a corrente de saı́da, o tempo

de duração é definido pelo PWM, o bloqueio de S4

ocorre no instante t7 .

Estágio 8 (t7 < t ≤ t8 ): Com o bloqueio de

S4 , é iniciada a descarga do capacitor Cb2 através

do diodo D22 , sendo parte desta energia regenerada para a entrada e o restante para a carga do

capacitor Cr . A tensão sobre a chave S4 cresce

linearmente devido à presença dos capacitores Cr

t

vSx2

E

t1 t2 t3 t4 t5

p

ILr2(max) = Iop + E/ Lr2 /Cr

t

E

t0

(2)

Estágio 3 (t2 < t ≤ t3 ): Durante esta etapa

o diodo D4 conduz a diferença entre a corrente

máxima em Lr2 e a corrente de saı́da, garantindo

a condição ZVS para o interruptor S4 . Este intervalo deve ser tão pequeno quanto possı́vel para

minimizar as perdas de condução no circuito auxiliar, no entanto, deve durar o tempo suficiente

para estabelecer a tensão de comando para o interruptor S4 .

Estágio 4 (t3 < t ≤ t4 ): Em t3 , a chave auxiliar Sx2 é bloqueada sob pseudo-ZVS devido à

presença do capacitor snubber Cb2 . O interruptor S4 assume a corrente de saı́da e a corrente

em Lr2 começa a descarregar através de D12 para

Cb2 , transferindo a energia armazenada no indutor para o capacitor. Esta etapa termina em t4

quando a tensão em Cb2 atinge +E, o tempo de

duração é definido pela Equação 4.

!

√

p

Cb

E

2

√

Lr2 · Cb2 (4)

∆t4 = sen−1

ILr2(max) Lr2

t

Comando Sx2

p

∆t2 = (π/2) Lr2 · Cr

t6

t7 t8

t

Figura 2: Formas de onda teóricas

Estágio 1 (t0 ≤ t ≤ t1 ): Anterior à primeira

etapa (t < t0 ), o diodo D3 conduz a corrente de

saı́da e ambas as chaves estão no estado de bloqueio. Em t0 a chave Sx2 é colocada em condução

sob pseudo-ZCS, devido à limitação da di/dt pelo

indutor Lr2 . As perdas de recuperação reversa

no diodo principal também são reduzidas devido

a presença do indutor. Esta etapa termina em t1 ,

quando a corrente em Lr2 é igual a Iop e o diodo D3 para de conduzir. O tempo de duração do

estágio 1 (∆t1 ) é dado por

∆t1 = (Lr2 /E)Iop

(1)

onde E é a tensão CC de entrada.

524

Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

+E

+E

S3

D3

Iop

S4

0

D4

+

Cb2

+

D22

Lr2

D12

Cr

+E

S3

Iop

S4

Sx2

0

[t0 – t1]

+E

D3

D4

+

Cb2

+

D22

Lr2

D12

D3

Iop

S4

0

D4

+

[t4 – t5]

Cb2

+

D22

Lr2

D12

Cr

S4

0

[t1 – t2]

+

D4

Cb2

+

D22

Lr2

D12

D3

Iop

S4

0

D4

+

Cb2

+

D22

Lr2

D12

S4

0

D4

+

Cb2

+

D22

Lr2

D12

Cr

Sx2

[t3 – t4]

+E

S3

D3

Iop

S4

0

[t5 – t6]

D3

Iop

[t2 – t3]

Sx2

Cr

S3

Sx2

Cr

+E

S3

Sx2

D3

Iop

Sx2

Cr

+E

S3

+E

S3

D4

+

Cb2

+

D22

Lr2

D12

Cr

S3

Iop

S4

Sx2

0

[t6 – t7]

D3

D4

+

Cb2

+

D22

Lr2

D12

Cr

Sx2

[t7 – t8]

Figura 3: Circuitos equivalentes aos estágios de operação

e Cb2 em paralelo, proporcionando uma comutação pseudo-ZVS. O término desta etapa ocorre no

instante t8 com a carga/descarga dos capacitores

completa, e o diodo D3 entra em condução.

∆t8 = (Cr + Cb2 )E/Iop

3.2

A amplitude máxima da corrente no indutor Lr

deve ser maior do que a corrente de saı́da, de forma

que o diodo antiparalelo à chave principal entre

em condução antes da transição de entrada do interruptor. Porém, este valor de corrente deve ser

limitado com o propósito de reduzir as perdas por

condução, e a capacidade de corrente necessária

do interruptor auxiliar. Assim

(5)

Estágio 9 (t8 < t ≤ t9 ): O diodo principal

D3 conduz a corrente de saı́da, a modulação PWM

define o tempo de duração desta etapa. O instante

de término deste estágio equivale ao inı́cio de um

novo ciclo, onde t9 = t0 .

3

ILr(max) = k2 · Iop

3.3

Restrição 3: Comando da chave auxiliar

Para que ocorra a comutação em zero de tensão

no interruptor principal, a chave auxiliar deve ser

mantida em condução até que seja estabelecido

o sinal de comando no mesmo. Este tempo de

condução (tSx ), consiste na soma da duração dos

estágios 1, 2 e 3, portanto

Restrição 1: Limitação da di/dt no diodo

tSx = ∆t1 + ∆t2 + ∆t3

Tem como objetivo reduzir as perdas de recuperação reversa no diodo antiparalelo ao interruptor

principal (D3 ou D4 ). Para que isso ocorra, o indutor Lr é dimensionado de forma que a derivada

de corrente (di/dt) no bloqueio seja limitada.

O intervalo ∆t1 (Equação 1) é o tempo para o

bloqueio do diodo, e deve ser maior que o tempo

de recuperação reversa (trr ) do mesmo. Assim,

o indutor ressonante é definido pela Equação 6,

onde k1 deve ser maior do que 1.

Lr = k1 · trr · E/Iop

(7)

onde a constante k2 deve ser maior do que 1.

A corrente ILr(max) é definida pela Equação

3, substituindo nessa a restrição da Equação 7 e

isolando o indutor auxiliar chega-se a

Lr = E 2 Cr / Io2p (k2 − 1)2

(8)

Restrições para o Projeto

Para obter sucesso no emprego da técnica de comutação suave apresentada é necessário considerar as não-idealidades dos dispositivos semicondutores utilizados e determinadas condições para o

correto funcionamento do circuito auxiliar.

O conversor é composto por duas células ZVT,

uma para cada sentido da corrente de saı́da e com

funcionamento análogo. Portanto os indutores

Lr1 e Lr2 têm o mesmo valor e serão definidos

como Lr , da mesma forma que Cb1 = Cb2 = Cb .

3.1

Restrição 2: Corrente máxima no indutor

(9)

A duração do primeiro e segundo estágios são

representados pelas Equações 1 e 2, respectivamente. Substituindo essas expressões na Equação

9 obtêm-se

πp

Lr

Lr Cr + ∆t3

(10)

tSx =

Iop +

E

2

onde o valor de ∆t3 deve ser definido com base no

atraso do circuito de acionamento e o tempo necessário para o processo de entrada em condução

do interruptor principal.

(6)

525

Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

3.4

Restrição 4: Limitação na razão cı́clica

3.6

Para reduzir as perdas na transição de bloqueio,

o tempo de subida da tensão sobre o dispositivo

deve ser maior que o tempo de descida (fall time)

da corrente. Conforme as etapas de operação, o

bloqueio do interruptor principal ocorre durante o

estágio 8, e o bloqueio da chave auxiliar ocorre no

estágio 4. Assim, podem ser escritas as restrições

Em inversores práticos a máxima razão cı́clica é

limitada devido ao tempo que o dispositivo semicondutor necessita para trocar entre os estados de

condução e bloqueio. Nos inversores com comutação suave existe também o tempo necessário para

o circuito auxiliar fornecer as condições nulas de

tensão e/ou corrente nos interruptores. Para o inversor em análise, o tempo de operação do circuito

auxiliar (tzvt ) é definido como

tzvt = tSx + ∆t8

Restrição 6: Intervalos para bloqueio

(11)

4

(12)

3.5

A taxa de variação da tensão sobre o semicondutor deve ser reduzida devido à limitações construtivas do dispositivo, limitações do circuito ou

para redução de EMI. Para que não ocorra uma

variação brusca de tensão no instante de boqueio

do interruptor principal, a tensão sobre o capacitor Cb deve alcançar o valor E durante o estágio

4. Dessa forma a tensão sobre o interruptor irá

crescer a partir de zero, reduzindo a dv/dt e consequentemente as perdas na comutação.

A energia necessária para o capacitor Cb atingir a tensão E é dada pela Equação 14.

WCb

1

Lr · IL2 r(max)

2

2

p

Lr I

+

E

C

/L

o

r

r

p

E2

Tensão de Entrada (E)

300 V

Tensão de pico na Saı́da (Vop )

180 V

Frequência de Saı́da (fo )

60 Hz

Potência de Saı́da (Po )

1000 W

Resistência de Carga (Ro )

16,2 Ω

Frequência de Chaveamento (fs )

40 kHz

Tabela 2: Caracterı́sticas dos semicondutores

Chave

Código

tf all , trr

Coes

S1 a S4

Sx1 , Sx2

IRGP50B60PD1

20 ns, 120 ns

322 pF

IRG4PC40UD

130 ns, 120 ns

140 pF

(14)

O capacitor Cr possui uma limitação mı́nima

correspondente à soma da capacitância intrı́nseca

(Coes ) dos interruptores principais do braço inversor. Com o intuito de reduzir as perdas por

condução no circuito auxiliar, o valor de Cr deve

ser projetado para o valor mı́nimo, ou seja, Cr =

2Coes . Essa definição não compromete a redução

das perdas no bloqueio dos interruptores, que é

garantida pelo capacitor Cb .

Para o indutor auxiliar Lr são obtidos 3 valores, em função do capacitor ressonante Cr , que

limitam a sua região de projeto. Da restrição 1,

definida pela Equação 6 determina-se Lra ; através da restrição 2 (Equação 8) é obtido Lrb ; outra

(15)

Igualando-se as expressões 14 e 15 define-se

um valor máximo do capacitor para a restrição

ser atendida, conforme Equação 16.

Cb ≤

Metodologia de Projeto

principais caracterı́sticas dos interruptores discretos utilizados.

A carga deste capacitor ocorre através da ressonância com o indutor Lr , no qual a máxima

energia armazenada é definida pela Equação 15.

WLr(max) =

(18)

Tabela 1: Especificações do Protótipo

(13)

Restrição 5: Limitação da dv/dt

1

= Cb E 2

2

∆t4 = k4 · tf l2

Este procedimento de projeto consiste em determinar os valores para Cr , Lr e Cb a fim de atender

às seis restrições apresentadas. A Tabela 1 contém

as especificações do conversor consideradas para o

projeto e implementação. A Tabela 2 mostra as

onde k3 é uma constante menor do que 1 e Ts é

o perı́odo de chaveamento. Substituindo a Equação 11 em 12 e admitindo que tSx >> ∆t8 , esta

restrição pode ser escrita como

tSx = k3 Ts

(17)

onde:

k4 - constante maior do que 1;

tf l1 - tempo de descida do interruptor principal;

tf l2 - tempo de descida do interruptor auxiliar.

Uma vez que o máximo intervalo de condução

do interruptor principal (ton(max) ) limita o ı́ndice

de modulação do conversor, o projeto deve assegurar que o tempo relacionado ao circuito auxiliar

seja limitado. Assim

tzvt = k3 Ts

∆t8 = k4 · tf l1

(16)

526

Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

limitação para o indutor é obtida através da combinação das restrições 3 e 4, no qual igualando-se

as Equações 10 e 13 obtêm-se Lrc .

√ !2

πE Cr

Eπ 2 Cr

Lrc =

+ k3 Ts − ∆t3 −

16Iop

4Iop

(19)

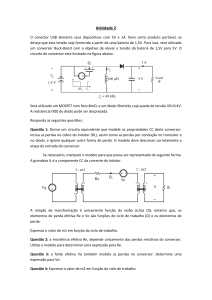

As constantes presentes nessas equações (k1 , k2 e

k3 ), devem ser projetadas para atender as restrições 1 a 4 e à partir disso determina-se o valor do

indutor correspondente. O valor das constantes

k2 e k3 é obtido através da análise do gráfico da

Figura 4, onde observa-se a influência do indutor

Lr nas principais grandezas envolvidas nas restrições: ILr(max) através de k2 , e tSx através de k3 .

s

E

Iop

1,4

Lra (R1)

0,15

Lrc (R3,R4)

k3

0,1

1,198

k3 - Adimensional

k2 - Adimensional

k2

arredondamento no valor correspondente do indutor. Assim, o indutor Lr = 12 µH em conjunto

com Cr = 644 pF atende às restrições 1 a 4, uma

vez que o valor correspondente de k1 = 3, 7 está

acima do mı́nimo definido, e k3 = 0, 031 equivale

à tSx de 3,1% do perı́odo de chaveamento, muito

inferior ao máximo definido anteriormente.

Com os valores de Lr e Cr projetados, são

obtidas as limitações para Cb de forma a atender

as restrições 5 e 6. Da restrição 5 definida pela

Equação 16 determina-se o valor de Cba ; para satisfazer a restrição 6, relativo ao bloqueio do interruptor principal, é obtido Cbb substituindo a

Equação 5 na Equação 17; e para o bloqueio da

chave auxiliar, também da restrição 6, determinase Cbc substituindo a Equação 4 na Equação 18.

O gráfico apresentado na Figura 5 mostra o comportamento dos tempos relativo aos estágios para

o bloqueio dos interruptores em função do capacitor Cb . O valor de Cba é calculado diretamente

7

6,4

0,05

Δt8 /tfall(S)

1

12

40

54,2

ConstanteSk4

0,031

70

Δt4 /tfall(Sx)

Cbb

Cbc

3

Cba

Indutor Lr [µH]

2,1

Figura 4: Gráfico para projeto de Lr

1

O gráfico mostra que a região de projeto do indutor está delimitada entre os valores de Lra (mı́nimo) e Lrc (máximo). O valor de Lra restringe a

constante k1 ≥ 3 (Bodur and Faruk Bakan, 2002),

o que corresponde à di/dt no diodo em aproximadamente 30 A/µs, obtendo Lra = 9,72 µH.

O limite superior de Lrc = 54,2 µH foi calculado para que o tempo máximo de condução

da chave auxiliar seja de 10% do Ts (Zhu and

Ding, 1999) e o ∆t3 igual a 200 ns, adotado com

base experimental devido às não-idealidades do interruptor e atrasos no circuito de acionamento.

Dentro da região de projeto deve-se definir

o valor da constante k2 , a qual é proporcional à

corrente máxima no indutor auxiliar. Essa constante é utilizada para assegurar que a amplitude

de ILr(max) tenha valor suficiente para garantir o

bloqueio do diodo principal e a entrada em condução do diodo antiparalelo, portanto deve ser maior

do que 1. Observa-se no gráfico que, com o incremento do indutor ocorre uma pequena diminuição

no valor da corrente máxima, porém o tempo de

condução da chave auxiliar aumenta proporcionalmente. Assim, para menores perdas em condução,

o valor mais adequado é próximo de Lra .

O valor projetado é igual a Lrb , adotando k2

para obter ILr(max) aproximadamente 20% acima

da corrente de saı́da, utilizou-se k2 = 1, 198 para

0

0,91

11

23,61

30

CapacitorSCbS[nF]

Figura 5: Gráfico para projeto de Cb

e equivale ao limite superior de projeto do capacitor. Para este valor toda a energia armazenada

no indutor é transferida para o capacitor alcançar

a tensão de entrada. Os valores Cbb e Cbc dependem da definição da constante k4 , no qual, para

reduzir as perdas no bloqueio dos semicondutores

recomenda-se um valor de 2 a 4 (da Silva Martins, 2008). Utilizou-se k4 = 2, 1 para arredondamento do capacitor correspondente.

Após determinar os valores, observa-se no gráfico que a região de projeto para Cb está entre os

valores de Cbc e Cba .

Com o intuito de reduzir a quantidade de

energia presente no circuito auxiliar e consequentemente as perdas por condução, o valor mais adequado para projeto é próximo do limite inferior,

portanto Cb = 11 nF.

Nas seções a seguir são apresentados os resultados experimentais para validação da metodologia de projeto, e a comparação de desempenho

com a implementação de um conversor com os circuitos auxiliares ZVT convencional e snubber de

Undeland.

527

Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

5

Resultados Experimentais

a tensão E, sendo o restante regenerado para a

entrada.

A Figura 8 mostra as comutações de entrada e

bloqueio no interruptor principal. Verifica-se que

o sinal de comando é aplicado ao interruptor após

a tensão sobre o mesmo ser nula, caracterizando

a entrada em condução sob ZVS. Também podese observar que o circuito auxiliar é ativo em um

pequeno intervalo em relação ao perı́odo de chaveamento.

O conversor CC-CA ponte completa, monofásico

e saı́da senoidal é mostrado na Figura 6, onde o

S1

vo

desconectar

para snubber

Ro

+

E

-

Cf

S2

A

D

S3

Dr1

io

Cb2

D22

Lr2

D12

Sx1

Lf

B

Lr1

S4

Cb1

C

Dr2

D11

S3

Sx2

D21

VS3

Figura 6: Conversor CC-CA ZVT PWM

braço inversor (S1 e S2 ) comuta em baixa frequência e S3 e S4 na frequência de chaveamento. As

especificações dos componentes do circuito auxiliar são mostrados na Tabela 3.

iLr1

iS3

S3 - 10 V/div; VS3 - 100 V/div; iLr1, iS3 - 10 A/div; Tempo: 2 µs/div

Tabela 3: Componentes ZVT

Figura 8: Comutações da chave principal - ZVT

Descrição

Especificação

Dr1 , Dr2 , D11 , D12

15ETH06

D21 , D22

O detalhe da transição de bloqueio é mostrado na Figura 9. Pode-se verificar a comutação

pseudo-ZVS através da limitação da dv/dt, dessa

forma reduz-se a sobreposição da tensão com a

corrente e consequentemente a potência dissipada

no semicondutor.

MUR460

Lr1 , Lr2

12 µH (EE 20/10/5-18 espiras)

Cb1 , Cb2

11 nF (2 x 22 nF em série)

Cr

644 pF (2Coes )

Através das formas de onda mostradas na Figura 7 pode-se verificar o funcionamento do circuito auxiliar. Ao comando para Sx2 a corrente

no indutor cresce com taxa de aproximadamente

25 A/µs e, após a ressonância com Cr a tensão

sobre o interruptor principal é nula, alcançando a

condição de ZVS. Verifica-se também a coerência

das grandezas com os parâmetros de projeto, onde

o valor teórico para a corrente máxima no indutor é 13,3 A e para o tempo da chave auxiliar em

condução é de 780 ns. Após o bloqueio de Sx2 , a

S3

iS3

VS3

S3 - 10 V/div; iS3 - 10 A/div; VS3 - 100 V/div; tempo: 400 ns/div

Figura 9: Bloqueio da chave principal - ZVT

As formas de onda na chave auxiliar são mostradas na Figura 10. Conforme análise teórica a

entrada em condução ocorre sob pseudo-ZCS e o

bloqueio sob pseudo-ZVS. Observa-se que o tempo

Sx2

iLr2

VS4

VCb2

Sx2

Sx2 - 10 V/div; iLr2 - 5 A/div; VS4, VCb2 - 100 V/div; Tempo: 400 ns/div

VSx2

Figura 7: Formas de onda no circuito ZVT

iSx2

energia armazenada no indutor passa a ser transferida para o capacitor snubber Cb2 . Conforme o

projeto do capacitor Cb , com o objetivo de redução nas perdas por condução, somente parte da

energia é necessária para carregar o mesmo até

Sx2 - 10 V/div; VSx2 - 100 V/div; iSx2 - 5 A/div; Tempo: 400 ns/div

Figura 10: Entrada e bloqueio chave auxiliar - ZVT

528

Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

de subida da tensão VSx2 é maior do que 273 ns

(k4 · tf l2 ), garantindo a redução das perdas.

Para a comparação de desempenho do circuito

proposto, o conversor CC-CA foi implementado

utilizando outros circuitos auxiliares à comutação,

mostrados na Figura 11. A implementação é feita

substituindo-se os circuitos auxiliares nos terminais A, B, C e D no conversor da Figura 6.

ZVT Convencional

A,D

Snubber de Undeland

A

Sx1

Ls

D

RS

Lr

B

Verifica-se que a condição ZVS na entrada é

alcançada pois o sinal de comando é aplicado somente após a tensão ser nula. O bloqueio do interruptor também é auxiliado através da limitação

da dv/dt pelo capacitor Cr .

As condições de comutação no interruptor auxiliar são mostradas na Figura 13. A entrada em

condução é sob pseudo-ZCS proporcionado pelo

indutor Lr , no entanto o bloqueio ocorre sem qualquer auxı́lio à comutação ou seja, sob forma dissipativa.

DS1

B

Sx2

CS

Cr

C

C

DS2

Sx1

COV

VSx1

Figura 11: Circuitos auxiliares implementados

iSx1

Sx1 - 10 V/div; VSx1 - 100 V/div; iSx1 - 10 A/div; Tempo: 400 ns/div

O projeto dos elementos auxilares da célula

ZVT convencional, Lr e Cr , é elaborado com o

objetivo de otimizar as condições de comutação

da chave principal, para estabelecer uma comparação equivalente com o ZVT proposto. Devido

este circuito utilizar o capacitor Cr para ambas

as funções, de elemento ressonante na entrada e

snubber no bloqueio, seu valor não pode ser muito

elevado pois aumenta a corrente máxima no circuito auxiliar e também não pode ser muito pequeno por comprometer a redução das perdas no

interruptor principal. A Tabela 4 contém os parâmetros de projeto e os componentes utilizados na

implementação.

Figura 13: Transições da chave auxiliar

O outro circuito auxiliar implementado, snubber de Undeland, tem a proposta de limitar a derivada de corrente na entrada do interruptor e durante o bloqueio controlar a dv/dt, além de grampear a tensão máxima sobre o semicondutor em

um nı́vel seguro. Para o projeto dos elementos

desse snubber foi utilizada a metodologia apresentada em Blaabjerg (1991), os valores obtidos para

os componentes são mostrados na Tabela 5.

Tabela 5: Componentes snubber de Undeland

Tabela 4: Projeto ZVT Convencional

Descrição

Especificação

Ls

Lr

20 µH (EE 25/10/6-26 espiras)

Cs

Cr

3,3 nF + 644 pF

Descrição

ILr(max)

tSx

Cov

Especificação

10 µH (EE 30/15/7-12 espiras)

10 nF

(470 nF + 33 nF)

Rs

1,38Iop

Ds1 , Ds2

4,7% de Ts

100 Ω - 35 W

MUR460

A corrente e tensão no interruptor principal

são mostradas na Figura 14.

A Figura 12 mostra as transições da chave

principal durante um perı́odo de comutação.

S3

VS3

iS3

iLr1

VS3

iS3

S3 - 10 V/div; VS3 - 100 V/div; iLr1, iS3 - 10 A/div; Tempo: 2 µs/div

iS3 - 5 A/div; VS3 - 100 V/div; Tempo: 4 µs/div

Figura 12: Transições da chave principal

Figura 14: Chave principal - snubber de Undeland

529

Anais do XX Congresso Brasileiro de Automática

Belo Horizonte, MG, 20 a 24 de Setembro de 2014

Nota-se que a corrente ressonante devido aos

elementos auxiliares circula através do interruptor, ocasionando um esforço adicional de corrente.

A comutação no instante de bloqueio tem limitação da dv/dt, porém também ocorre sobretensão

no interruptor.

Com o intuito de avaliar o desempenho dos

circuitos analisados, foram efetuadas medições de

potência de entrada e saı́da com um analisador

digital de energia, modelo Yokogawa WT1800.

A Figura 15 mostra a curva de rendimento

para cada estrutura implementada, obtida através

da variação da resistência de carga.

Com o conversor ZVT foi obtido rendimento

de 97% com potência nominal, valor este 1% maior

do que o obtido com o ZVT convencional e 2%

maior em relação ao snubber de Undeland. Em

toda a faixa de carga o conversor ZVT teve rendimento superior, com ênfase na operação com

pouca carga onde o valor foi de 3% acima do convencional.

Foi verificado através desta análise experimental que a metodologia de projeto é eficaz no

objetivo de atender às restrições propostas e contribuir para o aumento no rendimento do conversor.

Agradecimentos

98,0

Os autores agradecem à Universidade Tecnológica

Federal do Paraná, FUNTEF, CNPq, CAPES,

Fundação Araucária, SETI e FINEP pela estrutura e apoio financeiro.

ZVT

97,0

Rendimento [%]

96,0

ZVT convencional

95,0

snubber de Undeland

94,0

93,0

Referências

92,0

91,0

200

300

400

500

600

700

800

900

Blaabjerg, F. (1991). Snubbers in pwm-vsiinverter, Power Electronics Specialists Conference, 1991. PESC ’91 Record., 22nd Annual IEEE, pp. 104–111.

1000

Potência de Saída [W]

Figura 15: Comparativo de rendimento

Bodur, F. and Faruk Bakan, A. (2002). A new

zvt-pwm dc-dc converter, Power Electronics,

IEEE Transactions on 17(1): 40–47.

Observa-se que o conversor ZVT, cuja metodologia de projeto foi aplicada, apresentou rendimento superior às demais estruturas em toda a

faixa de carga. Esta topologia tem a vantagem,

em relação ao convencional, de operar com menor valor de corrente no circuito auxiliar e prover

auxı́lio à comutação em ambos os interruptores,

principais e auxiliares.

A impedância do circuito ressonante no ZVT

convencional é aproximadamente duas vezes menor do que no ZVT, quando a potência de saı́da é

baixa a corrente no circuito auxiliar se torna significativa, o que explica o menor rendimento do

ZVT convencional para estas potências.

A solução dissipativa, através do snubber de

Undeland, fornece auxı́lio à comutação na entrada

e bloqueio dos interruptores, porém o fato de não

regenerar a energia utilizada compromete o rendimento global do conversor.

6

da Silva Martins, M. L. (2008). Inversores ZCZVT

com Acoplamento Magnético: Sı́ntese e Análise, PhD thesis, Pós-Graduação em Engenharia Elétrica - Universidade Federal de

Santa Maria, Santa Maria - RS.

Hua, G., Leu, C. S. and Lee, F. C. (1992). Novel zero-voltage-transition pwm converters,

IEEE Power Electronics Specialists Conference, Vol. 1, pp. 55–61.

Russi, J., Martins, M. L., Gründling, H. A., Pinheiro, H., Pinheiro, J. R. and Hey, H. L.

(2005). An improved design for zvt dc-dc

pwm converters with snubber assisted auxiliary switch, Revista Controle & Automação

16(1): 25–33.

Zhu, J. Y. and Ding, D. (1999). Zero-voltage- and

zero-current-switched pwm dc-dc converters

using active snubber, Industry Applications,

IEEE Transactions on 35(6): 1406–1412.

Conclusões

Este artigo abordou uma metodologia de projeto

para um conversor CC-CA ZVT PWM, desenvolvida com base nas equações referente às etapas

de operação e restrições para o correto funcionamento do circuito auxiliar. Um exemplo de projeto foi aplicado a um protótipo para análise das

formas de onda e curvas de rendimento, sendo este

comparado ao conversor com a célula ZVT convencional e com o snubber de Undeland.

530