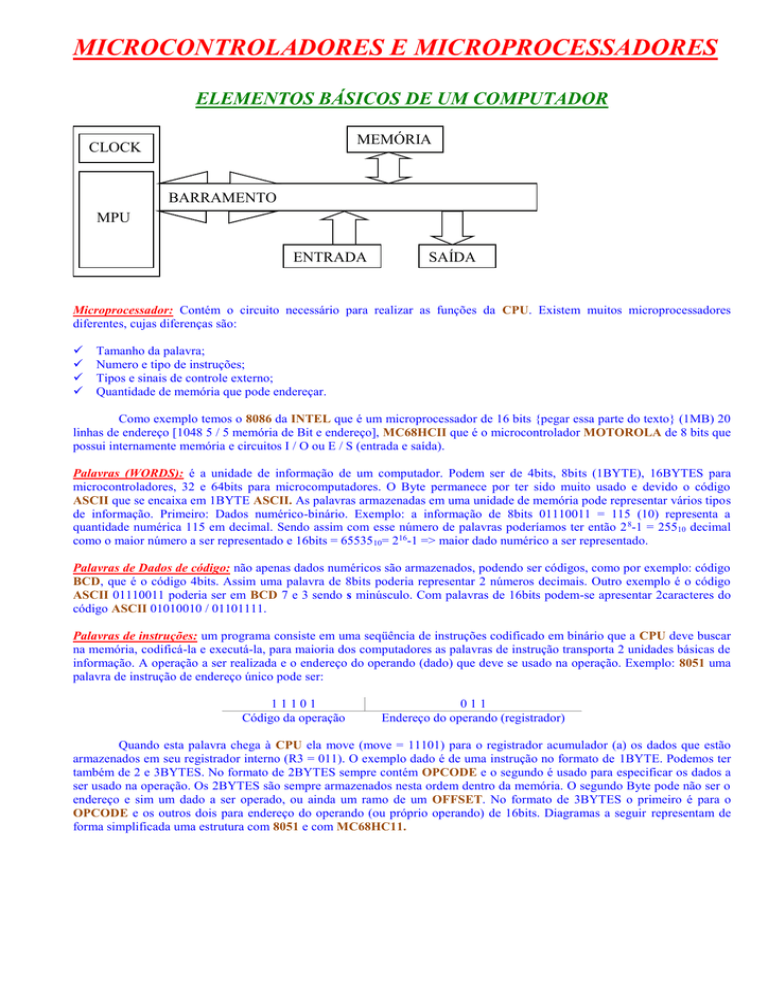

MICROCONTROLADORES E MICROPROCESSADORES

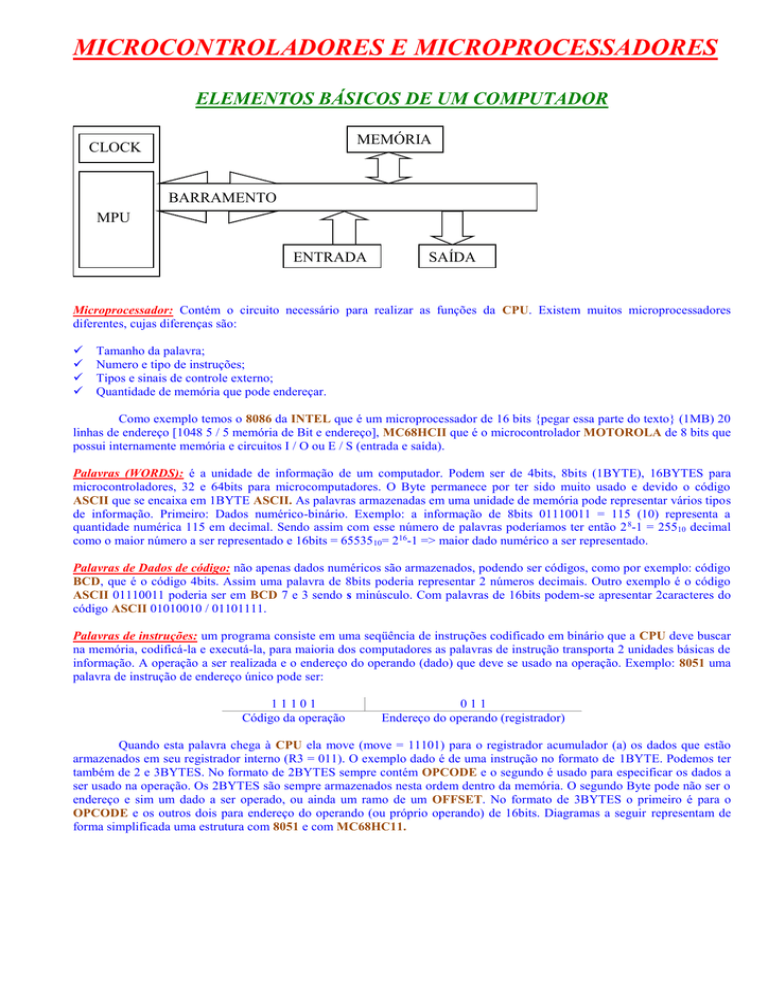

ELEMENTOS BÁSICOS DE UM COMPUTADOR

MEMÓRIA

CLOCK

BARRAMENTO

MPU

ENTRADA

SAÍDA

Microprocessador: Contém o circuito necessário para realizar as funções da CPU. Existem muitos microprocessadores

diferentes, cujas diferenças são:

Tamanho da palavra;

Numero e tipo de instruções;

Tipos e sinais de controle externo;

Quantidade de memória que pode endereçar.

Como exemplo temos o 8086 da INTEL que é um microprocessador de 16 bits {pegar essa parte do texto} (1MB) 20

linhas de endereço [1048 5 / 5 memória de Bit e endereço], MC68HCII que é o microcontrolador MOTOROLA de 8 bits que

possui internamente memória e circuitos I / O ou E / S (entrada e saída).

Palavras (WORDS): é a unidade de informação de um computador. Podem ser de 4bits, 8bits (1BYTE), 16BYTES para

microcontroladores, 32 e 64bits para microcomputadores. O Byte permanece por ter sido muito usado e devido o código

ASCII que se encaixa em 1BYTE ASCII. As palavras armazenadas em uma unidade de memória pode representar vários tipos

de informação. Primeiro: Dados numérico-binário. Exemplo: a informação de 8bits 01110011 = 115 (10) representa a

quantidade numérica 115 em decimal. Sendo assim com esse número de palavras poderíamos ter então 2 8-1 = 25510 decimal

como o maior número a ser representado e 16bits = 6553510= 216-1 => maior dado numérico a ser representado.

Palavras de Dados de código: não apenas dados numéricos são armazenados, podendo ser códigos, como por exemplo: código

BCD, que é o código 4bits. Assim uma palavra de 8bits poderia representar 2 números decimais. Outro exemplo é o código

ASCII 01110011 poderia ser em BCD 7 e 3 sendo s minúsculo. Com palavras de 16bits podem-se apresentar 2caracteres do

código ASCII 01010010 / 01101111.

Palavras de instruções: um programa consiste em uma seqüência de instruções codificado em binário que a CPU deve buscar

na memória, codificá-la e executá-la, para maioria dos computadores as palavras de instrução transporta 2 unidades básicas de

informação. A operação a ser realizada e o endereço do operando (dado) que deve se usado na operação. Exemplo: 8051 uma

palavra de instrução de endereço único pode ser:

11101

Código da operação

011

Endereço do operando (registrador)

Quando esta palavra chega à CPU ela move (move = 11101) para o registrador acumulador (a) os dados que estão

armazenados em seu registrador interno (R3 = 011). O exemplo dado é de uma instrução no formato de 1BYTE. Podemos ter

também de 2 e 3BYTES. No formato de 2BYTES sempre contém OPCODE e o segundo é usado para especificar os dados a

ser usado na operação. Os 2BYTES são sempre armazenados nesta ordem dentro da memória. O segundo Byte pode não ser o

endereço e sim um dado a ser operado, ou ainda um ramo de um OFFSET. No formato de 3BYTES o primeiro é para o

OPCODE e os outros dois para endereço do operando (ou próprio operando) de 16bits. Diagramas a seguir representam de

forma simplificada uma estrutura com 8051 e com MC68HC11.

12/02/07

8086

Em 1978 a Intel lança a CPU 8086 de 16 bits (tamanho de palavra) que revolucionou o mercado de PC. A

preocupação era manter a compatibilidade com a CPU 8085 de 8 bits. Sendo assim as instruções do 8086 formava um

conjunto das instruções do 8085 assim como os registradores 8086 foram compatíveis com os do 8085.

Dentre as inovações do 8086 destacam-se:

a)

Era dividida em duas unidades independentes:

i.

EU (unidade de execução)

ii.

BIU (unidade de interface com o barramento)

b) O 8086 foi projetado para trabalhar em módulo mínimo (uma só CPU) ou módulo máximo (sistema

multiprocessado).

c) No módulo múltiplo processado cada 8086 tem sua própria memória local que compartilha com os outros uma

memória comum.

d) Podia endereçar 1megabit de memória (220 endereços de memória)

e) Deve-se usar junto com 8086 o 8284 (gerador de clock) e o 8288 (controlador de barramento).

CICLOS DE BARRAMENTO (8086)

- Barramento: conjunto de condutores por onde trafegam sinais elétricos que fazem a comunicação entre o processador e outro

circuito qualquer (por exemplo, memória).

- Ciclo do Barramento: é a seqüência com que são gerados os sinais necessários para CPU acessar outros circuitos (memória

ou periféricos). O clock é que faz o sincronismo desses sinais.

Podemos ter um ciclo de barramento para leitura ou para escrita. O ciclo mais curto demora quatro períodos de clock

(T1, T2, T3 e T4), no mínimo. Por exemplo, numa leitura durante T1, o 8086 envia ao barramento os 20bits de endereço (A0...

A19 – 2 a 16, 35 a 39).

Os endereços no barramento são considerados validos quando ALE (25) está em nível alto, porém, para garantir a

estabilização das linhas de endereço estas só são utilizadas quando ALE faz uma transição de descida (↓).

Durante T2 os endereços são removidos e o barramento de dados (D0... D15 - 2 a 16 e 39) vai pra alta impedância

(não há no barramento um nível lógico definido), preparando-se para a leitura. O sinal de *RD (32) é ativo em T2. Ao final de

T3 a CPU Le os dados presentes no barramento. Se nesse período (T3) a memória ou o periférico não for capaz de entregar o

dado no barramento na velocidade da CPU, essa deve ser avisada através do pino READY (22) em nível baixo. Dessa forma a

CPU irá repetir T3. Quando o dispositivo termina a transferência ele retorna a linha READY em nível alto e a CPU Le o dado,

realiza o período T4 e encerra o ciclo de leitura.

Nesse ciclo existe também a ação das linhas M/*IO, irá indicar se a leitura é feita na memória ou em um dispositivo

de entrada e saída. Os transceivers são ativos em T1 ou T2 de acordo com os pinos DT/*R e *DEN (26).

PINAGEM (8086)

- AD0 à AD15 (2-16 e 39): Nessas dezesseis linhas são multiplexados endereços de dados. Em um ciclo de barramento durante

T1 por elas aparecem os dezesseis bits menos significativos de endereços e durante os outros períodos circulam por elas os

dados.

- AD16 – S3 (38): Durante T1 ela recebe a linha dezesseis de endereço e durante os outros períodos é usado junto com A17 /

S4 (37) para fornecer informação de estado.

- AD17 / S4 (37): Durante T1 ela recebe a linha dezessete de endereço e durante os outros períodos é usado com A16 / S3 (38)

para fornecer informação de estado.

- A18 / S5 (36): Durante T1 ela recebe a linha dezoito de endereço e durante os outros períodos mostra o estado da FLAG de

habilitação de interrupção (IF).

- A19 / S6 (35): Durante T1 ela recebe a linha dezenove de endereço e durante os outros períodos ela estará em nível baixo

quando é executada uma instrução de I / O

- *BHE / S7 (34): Durante T1 ela serve como BHE (Bus High Enable) e durante os demais períodos ela mantém o mesmo

nível T1.

- *RD (32): Durante a operação de leitura é mantido em nível baixo.

- Ready (22): Recebe do dispositivo que ainda não disponibilizou o Barramento. Por essa linha um dispositivo externo “avisa”

a CPU que ainda não está pronto para realizar uma transferência de dados solicitado.

- *Teste (23): é usada somente com a instrução Write. Quando executada (habilitada) a CPU faz uma pausa. Essa linha é

acionada pelo 8087. (co-processador matemático)

- INTR (18): É por essa linha que se pede uma interrupção à CPU. Ao final de cada instrução executada a CPU verifica essa

linha e se ela estiver em nível alto e também a Flag de interrupção IF estiver em nível alto, o 8086 executa o reconhecimento

de interrupção e transfere todo controle para a sub-rotina apropriada. (INTR e IF tem de estar em nível alto ao mesmo tempo.

O Sistema Operacional que faz a verificação).

- NMI (17): (Interrupção não mascaravel – Interrupção fundamental para seqüência de operação) tem a mesma função de

INTR, porém é uma interrupção não mascarada, ou seja, é sempre aceita. Enquanto INTR é habilitada por nível, NMI é

habilitada por borda (↓).

- Reset (21): Inicializa a CPU quando em nível baixo.

Observação: Linhas não afetadas pelo método mínimo ou pelo modo máximo.

- *DEN (26): Por essa linha sabe-se que haverá tráfego de informações pelo barramento de dados. É ela que controla os

transceivers (74LS245)

- DT / *R (27): Igual a um significa que serão colocados dados no barramento pela CPU. Igual a zero significa que serão

retirados dados do barramento pela CPU. Junto com DEN essa linha controla os transceivers indicando apenas a direção do

fluxo de dados.

- M / *IO (28): Igual a um significa que a CPU estará “conversando” com o dispositivo de memória. Igual a zero significa que

estará trocando informações com IO.

- ALE (25): (Habilitação dos latch de endereços) Address Latch Enable. É o sinal responsável pela demultiplexação das

linhas de dados e endereço. Se igual a um significa que no barramento existe um endereço válido. Se ALE igual a zero

significa que existe um dado ou uma informação de estado válidos. Na verdade o ALE é responsável pela habilitação do Latch

Tipo D 7465373.

- INTA (24): Essa linha é mantida em nível baixo enquanto a CPU faz o reconhecimento de uma interrupção (controlador de

interrupções).

- HOLD (31): Por esta linha pede-se à CPU um estado de Hold (controle do barramento / ceder para outro dispositivo o

barramento).

- HLDA (30): Por essa linha a CPU avisa que ela aceitou o estado de HOLD.

- *WR (29): É a linha através da qual se executa uma operação de escrita na memória ou dispositivo de IO. Ela deve

permanecer em nível baixo, porém o dispositivo só captura a informação na borda de subida dessa linha.

Observação: Linhas afetadas pelo modo mínimo.

- *S2, *S1, *S0 (27, 28, 26): Válidas durante T1 essas linhas servem para controlar um controlador de barramento (8288)

quando o 8086 opera em modo máximo. A lógica dessas linhas é a seguinte:

S2

0

0

0

0

1

1

1

1

S1

0

0

1

1

0

0

1

1

S0

0

1

0

1

0

1

0

1

Interrupção

Leitura de I/O

Escrita de I/O

HALT

FETCH de instrução

Leitura de memória

Escrita na memória

Inativo

Observação:

1) Em HALT as linha de endereço e dados da CPU vão para um estado indefinido e não ocorre ciclos de barramentos na

CPU. O estado de halt só é terminado com Reset ou uma interrupção. A CPU estando em HALT a lógica de HOLD

ainda funciona permitindo que outros dispositivos consultem a memória.

2) - FETCH: significa executar um ciclo de busca que é realizada pela BIU.

- QS0, QS1 (25,24): Indicam o estado da fila de instruções do 8086. A BIU possui uma fila de 6 Bytes para códigos que ela

busca na memória e procura manter sempre cheia para a EU executar. A lógica dessas duas linhas é a seguinte:

QS0

0

0

1

1

QS1

0

1

0

1

Nenhuma

1.º Byte da Fila em execução

Fila ficando vazia

Byte seguinte de uma instrução está sendo retirado da fila.

- *RQ / *GT1 (30): menor prioridade, idêntico ao anterior.

- *LOCK (29): um nível baixo nessa saída evita que a CPU perca o controle do barramento enquanto está executando uma

instrução. Quando 8086 executa instrução LOCK o pino 29 é colocado em nível baixo durante a execução da instrução

seguinte.

Observação: Linhas Afetadas pelo módulo máximo.

- MN / *MX (33): Responsável por colocar 8086 em modo mínimo ou em modo máximo.

- CLK (19): Entrada do sinal de clock para o sincronismo de toda lógica. Geralmente esse sinal é fornecido pelo 8284.

- VCC (40): 5 v + ou – 10% (dc). O consumo típico do 8086 é da ordem de 360mA.

- GND (20,1): Referência.

BARRAMENTO DE ENDEREÇOS E DADOS

Como usar a Memória com o 8086

Os 1Mega endereços diferentes são divididos em dois bancos de 512K cada um (par/ímpar). O banco par é conectado

nas oito linhas menos significativas do barramento de dados enquanto que o banco ímpar é conectado nas oito mais

significativas. O acesso a uma palavra de 16 bits é feito somente pelo endereço de seus oito bits menos significativos. Quando

se deseja armazenar uma palavra de 16bits deve-se usar 8bits do banco par e 8bits do banco ímpar, sempre na seqüência.

Quando os oito bits menos significativos estão no banco par e os oito mais significativos no ímpar, é endereçado o

menos significativo, habilitando-se o banco par (A0 = 0) e no mesmo ciclo de barramento habilita-se o banco impar fazendo

BHE = 0. Se os oito bits menos significativos estiver no banco ímpar e os 8 mais significativos no banco par, o endereço deve

ser dado para os oito bits de o banco impar e somente no próximo ciclo de barramento é que se pode habilitar o campo par.

Para palavras de oito bits, habilita-se apenas um dos bancos onde se encontra a informação. Como exemplos dessas

buscas podemos ter as seguintes instruções:

MOV AL, 00002 h

MOV AH, 0003h

MOV AX, 0004h

MOV AX, 00007h

Como separar o Barramento de Endereços.

Dados de endereços são multiplexados, ou seja, dividem as mesmas linhas do barramento. A forma mais usual de se

separar os endereços é utilizar latches (74LS373). Controlados pelo sinal ALE. O 74373 possui um sinal de controle *OE para

colocar o dispositivo em alta impedância e o sinal C para determinar a operação do Latche. A operação do 373 obedece a

seguinte tabela verdade:

*OE

L

L

L

X

D

X

L

H

X

C

L

H

H

X

Q

Q0

L

H

Z

A figura a seguir mostra um exemplo de demultiplexação do barramento de endereços. É importante lembrar que o

endereço é capturado na borda de descida do sinal ALE de forma que esse endereço esteja estável nas linhas.

Como usar o Barramento de Dados

O esquema anterior mostra o barramento de endereços demultiplexado através do 74LS373 e o barramento de dados

apenas multiplexado. Esse tipo de esquema pode ser usado em pequenos projetos apenas garantindo-se que as memórias ou os

dispositivos e I/O que estejam conectados a esse barramento, não interfiram com os endereços no período T1. Para se garantir

isso, esses dispositivos devem possuir a opção 3 Estados que pode ser controlado pela linha *RD da CPU.

Para projetos maiores surge um problema: a capacidade de carga do 8086 (2mA / 100pf). Com essa capacidade

restringe-se a quantidade de dispositivos a serem conectados ao sistema. Para se resolver esse problema usa-se circuitos

especiais que “potencializam” o barramento. Esses dispositivos são chamados transceivers e o CI utilizado é o 74LS245.

O 8086 possui duas linhas que controlam esses Cis: a linha *DEM (Data Enable) que avisa que haverá tráfego pelo

barramento de dados e a linha DT/*R (Data TX or RX) que indica a direção que esses dados terão no barramento. (entrando ou

saindo da CPU).

No 74LS245 a habilitação é feita através da linha *OE e a direção é feita através da linha DIR. o esquema a seguir

mostra esta situação:

Modo Mínimo

Nesse modo MN/*MX é conectado em +Vcc e o sistema opera com uma única CPU. Endereça 1MB de memória e

64KB de dispositivos de I/O. para controle de barramento são usados os sinais: DT/*R, *DEN, ALE, MI*IO, *RD, *WR,

*INTA que são fornecidos pela própria CPU. Um esquema desse projeto é mostrado abaixo:

Modo Máximo

Com MN/*MX = 0 (em Baixo) utiliza-se sistemas multiprocessados. Neste modo um controlador de barramento

recebe sinais de estado do 8086 gerando sinais de controle do barramento. Nesse modo aparece agora os pinos QS0 E QS__

que permitem que outros processadores acompanhem a execução da CPU, os pinos *RQ/*GT0 E *RQ/*GT1 permitem que

diversas CPUs compartilhem o mesmo barramento e os pinos *S0, *S1, *S2 que ditam o estado do barramento ao 8288 pela

CPU. O esquema desse projeto é mostrado abaixo.

UNIDADE DE EXECUÇÃO (EU) E UNIDADE DE INTERFACE COM O

BARRAMENTO (BIU)

O 8086 tem duas unidades independentes: a EU e a BIU. A EU é responsável pela execução das instruções e quando

ela executa uma instrução ela retira um código do Topo de uma fila de códigos de 6 Bytes. Se essa fila está vazia a BI executa

um ciclo de busca de instruções tentando manter cheia essa fila de códigos. Raras vezes essa fila está vazia e, portanto quase

nunca a EU precisará aguardar ciclos de busca realizados pela BIU. Se a memória ou um dispositivo de I/O precisam ser

acessados pela EU durante a execução de uma instrução, ela informa a BIU sobre essa necessidade e essa por sua vez realiza

ciclos de barramentos para atender a solicitação da EU. É importante observar que se a BIU está executando um ciclo de

barramento e a EU fizer uma solicitação, essa terá que aguardar aquela terminar o seu ciclo.

A EU é composta por registradores de dados, registradores de endereços, ULA e unidade de controle. A BIU é

composta pelos registradores de segmentos, pela fila de códigos (6bytes), pelos blocos que realizam a lógica de endereçamento

de memória.

Os registradores do 8086 mantiveram certa compatibilidade com os do 8085. O 8086 possui: quatro registradores de

finalidade geral (AX, BX, CX, DX), dois registradores apontadores de segmento (SP, BP), quatro registradores de segmento

(CS, DS, SS, ES), dois registradores de Indexação (SI, DI), um ponteiro de instrução (IP) e um registrador de estados

(FLAGS), todos de 16 bits.

Os Quatro Registradores de Finalidade Feral (AX, BX, CX, DX):

Como o próprio nome diz são de finalidade geral que podem ser acessados como registradores de 16 bits ou de 8 bits.

Cada um deles é dividido em parte alta e parte baixa com 8 bits cada um. Por exemplo, o AX é dividido em AH e AL. todos

esses registradores podem ser usados como operandos em operações lógicas e aritméticas, porém eles tem algumas funções

especiais.

AX: Acumulador primário. Todas as operações de I/O são realizadas utilizando este registrador. Algumas operações

com strings e instruções aritméticas usam este registradores. Valores que retornam de sub-rotinas são guardados nesse

registrador.

BX: Registrador Base. Utilizado no cálculo de endereço de memória juntamente com o registrador de segmento DS.

CX: Contador. Usado como contador em operações com loops.

DX: endereçador de I/O e Registrador de Dados. Fornece o endereço em operações de I/O. usado em operações

aritméticas com o resultado a 32 bits. Também utilizado para guardar valores retornados de sub-rotina.

Para acessar esses registradores a 16 bits utiliza-se o termo ___X e a 8 bits ___H ou ___L. Por exemplo: MOV AX, 4756h;

significa carregar o acumulador (16 bits) com a informação que se encontra no endereço de memória 4756h. ADD AH, #03h,

significa adicionar a parte alta do acumulador AH (8bits) a quantidade 03.

Os Dois Registradores Apontadores de Segmento (SP, BP)

São os dados para acessar dados do segmento da pilha ou como operandos em operações lógicas e aritméticas de

16bits.

SP: Ponteiro de Pilha. Armazena o Offset do endereço do topo da pilha controlando os endereços de retorno de subrotinas. Todas referencias a esse registrador usam o registrador de segmento ss.

BP: Ponteiro da Base. Permite acessar dados na pilha. A pilha é importante quando se utiliza sub-rotinas. Quando se

executa uma sub-rotina em um programa é preciso marcar qual instrução do programa deve ser executada após o término da

sub-rotina. Isso é feito armazenando-se na pilha o endereço de retorno. O registrador SP é usado para subtrair um numero de

bytes gastos para representar endereço de retorno de forma que seja atualizada a posição do topo da pilha. Quando o

processador encontra uma instrução de retorno de sub-rotina o programa é desviado para o endereço presente no topo da pilha

e SP é incrementando automaticamente voltando ao seu valor original.

Os Quatro Registradores de Segmento (CS, DS, SS, ES)

A memória no 8086 é particionada em segmentos de tamanho 64K endereços assim todo acesso à memória é feito

através de segmentos de 64k endereços. Isso é feito para facilitar o acesso e o gerenciamento de grandes memórias por uma

CPU (para a época 1Mega era grande). Os registradores de segmento funcionam como selecionadores dessas faixas de

endereçamento. Cada um deles especifica uma faixa de 64k endereços consecutivos. O endereço de início, chamado de

endereço base, de uma faixa é dado pelo conteúdo de seu registrador de segmento deslocado de quatro bits à esquerda. O

acesso a endereços dentro da faixa é feito através de um deslocamento OFFSET a partir do endereço base. Sendo assim todo

endereço no 8086 é calculado a partir de quatro bytes: dois que especificam o seletor e dois que especificam o Offset. Isso

pode ser representado no seguinte diagrama:

CS: Segmento de Código. Todo acesso à código do programa usa esse registrador como seletor e o IP como Offset.

DS: Segmento de Dados. Todo acesso a dados usam esse registrador como referencia, exceto nos casos:

¤ Acessos à pilha usa-se o SS;

¤ Operações com Strings que usam o DI no cálculo do endereço usam o ES;

¤ Acesso a dados que usam o BP são calculados a partir do SS.

SS: Todos os acessos a dados que usam SP ou BP são calculados utilizando o SS como preferência.

ES: Segmento Extra. Operações com Strings que usam DI para calcular endereço são feitas usando esse registrador

como seletor do segmento ou da faixa de endereço.

Os Dois Registradores de Indexação (SI, DI)

São utilizados para acessar dados da memória de dados, nas operações com String e com operando nas operações

lógicas e aritméticas de 16 bits.

FLAGS

O 8086 possui um registrador de 16 bits denominado registrador de estado ou palavra de estado do programa (PSW)

ou ainda denominado simplesmente FLAGS. O esquema mostrado estão as FLAGS matemáticas que são:

C: Carry. Indica o vai um do bit mais significativo nas operações aritméticas de oito ou dezesseis bits. Por exemplo: após

realizar a seguinte seqüência de instruções a FLAG C assumirá o valor lógico um, pois:

MOV AL, #E1h

MOV AL, #D5h

P: Paridade. Indica a paridade Par dos 8 bits menos significativos do resultado da operação realizada. Se P = 0 significa que

existe um numero impar de 1 nos 8 bits menos significativos do resultado. Se P = 1 esse numero é Par. Assim no exemplo

anterior após a seqüência de instruções P = 0.

A: Auxiliar Carry. Indica o vai 1 no quarto bit de uma operação de 8 bits. No caso do exemplo, A = 0.

Z: Zero. Se Z = 1 indica que o resultado da operação é zero. Se Z = 0 indica que o resultado da operação é diferente de zero.

No exemplo Z = 0.

S: Flag de sinal. Se S = 0 indica que o resultado é positivo e S = 1 indica que o resultado é negativo. No exemplo S= 1.

(Complemento a 2).

T: Trap. Quando esta flag está em nível alto significa que o 8086 está no modo passo a passo, de forma que após a execução de

cada instrução é chamada uma exceção. Isso é utilizado para a depuração de programas.

I: Interrupção. Se I = 1 significa que foi habilitada uma interrupção. Se I = 0 interrupção está desabilitada. Essa Flag é

conectada ao Pino INTR (18).

D: Direção. Se D = 1 os registradores de indexação SI e DI serão decrementados, ou seja, a String será acessada a partir do

endereço mais alto para o endereço mais baixo. Se D = 0, os registradores de indexação SI e DI serão incrementados, ou seja, a

String será acessada a partir do endereço mais alto para o endereço mais baixo.

O: Overflow. Indica overflow aritmético em aritmética binária com sinal.

Ponteiro de Instrução (IP)

Junto com o CS é responsável para marcar o endereço da próxima instrução a ser executada.

MODOS DE ENDEREÇAMENTO NO 8086.

Uma dúvida surge quando se precisa de 20 bits para se endereçar 1Mega endereços diferentes e se tem registradores

de apenas 16 bits. É o caso do 8086. Para se resolver esse problema o endereço é gerar a partir da adição de um endereço

básico (vindo do registrador de segmento qualquer um dos quatro) com um OFFSET (deslocamento). O seletor é deslocado

4bits à esquerda e então adicionado ao OFFSET com o indicado a seguir.

Seletor

Offset

En. Fs.

X

0

Z

X

0

Z

X

0

Z

X

0

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

X

Y

Z

0

Y

Y

0

Y

Y

0

Y

Y

0

Y

Z

Inicio

Deslc.

Endereço físico é o código que a CPU envia pelo barramento de endereços para acessar um endereço da memória.

Analisando a adição percebe-se que com duas palavras de 16bits gera-se um endereço de 20bits. Por exemplo: Suponha que se

necessite transferir para o registrador AL o byte que se encontra presente na posição de memória 97AC4h. Como se trata de

um dado é necessário conhecer o valor de registrador DS, pois ele será o seletor do inicio do segmento de dados. Se instruções

apropriadas tornaram DS = 97AC, o segmento DS estará compreendido na faixa de 97AC0h à A7ABFh que significa 97AC0h

+ FFFFh. Assim para se fazer o acesso a um endereço desejado (97AC4h) basta a instrução MOV AL, #0004h. esse valor

0004h indica o OFFSET a ser somado ao endereço base gerado a partir de DS.

EXERCÍCIOS

1) Utilizando o 8086/8284 e os circuitos integrados 74373 e 74245 faça as ligações linha a linha de um projeto em modo

mínimo.

2) Após cada um dos programas a seguir, determine o valor em binário de cada registrador envolvido e também de cada

Flag do 8086. Considere que os registradores inicialmente estão com os seguintes valores:

A = [AC71] h B = [810A] h

C = [0001] h

D = [AEE0] h PSW = [0000] h

Endereços de Memória: 2300h = [AB] h

2301h = [01] h

FE00h = [C7] h

FE00h = [A1] h

2300 h

2301 h

AX

a)

MOV AX, 2300 h

ADD AX, # 022D h

AX [01AB] h

ADD [022D] h + AX

AX [03D8] h

O

0

01AB

022D

03D8

0

0

0

0

0

0

D

0

0

0

0

0

0

0

I

0

0

0

0

AB h

01 h

01AB

T

0

0

0

0

0

1

1

S

0

1

0

1

1

0

1

Z

0

0

0

1

A

1

1

1

0

0

0

1

P

1

C

0

1

1

1

0

1

0

1

0

0

1

1

0

1

0

1

1

1

1

1

0

1

b)

MOV AX, BX

SUB AX, BX

MOV FE00 h, AH

BX 810A h

AX BX

SUB AX – BX

FE00 h AH

O

0

D

0

I

?

T

0

S

1

Z

1

A

1

P

1

C

(BX = 810A h)

(AX = BX = 810A h)

(810A h – 810A h)

(FE00 h = 00)

c)

MOV AX, FE00 h

OR AX, BX

AX [A1C7] h

OR AX or BX

BX [810A] h

AX [A1CF] h

FE00 h

FE01 h

AX

O

0

A1CF

810A

A1CF

C7 h

A1 h

A1C7 h

D

?

1

1

1

I

?

0

0

0

1

0

1

T

?

0

0

0

S

0

0

0

0

0

0

0

Z

0

0

0

0

A

0

1

1

1

1

0

1

P

1

1

0

1

0

0

0

C

0

0

0

0

1

1

1

d)

CLR AX

INC CX

XOR AX, DX

MOV 2300 h, AL

AX [0000]

CX [0001]

DX [AEE0] h

XOR AX xor DX

AX [AEE0]

2300 h [E0] h

O

0

D

?

0000

AEE0

AEE0

I

?

0

1

1

T

?

0

0

0

0

1

1

S

0

0

0

0

0

1

1

Z

0

0

1

1

A

0

0

1

1

0

0

0

P

0

0

1

1

C

0

0

1

1

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

HISTÓRIA

A primeira geração (1968) marcou os IA – 16 (arquitetura Intel) que se caracterizou pelo como clones destes dois o V30 e o V-20 da MAC. A mesma época a Intel lançou o 80186 e o 80188 usados como MC. O 80286 caracterizaram a segunda

geração, motivando o surgimento da arquitetura AT. À época dessa segunda geração surgiram os primeiros chip sets. A

terceira geração (1985) marca o inicio da IA – 32. A Compaq ofereceu o primeiro PC AT com o 80386 da Intel. Como clones

desse processador citam-se o AM – 386 (AMD) e o 386 – 5LC (IBM), além de outros fabricantes que produziram seus 386. A

quarta geração (1989) teve como novidade o 80486 com a unidade aritmética integrada. A quinta geração (1993) foi marcada

pelo Pentium e viu-se o fim da nomenclatura 80XXX. A AMD fabricou seu clone, denominado K-5. A sexta geração (1995)

foi marcada pelo Pentium Pró, Pentium II e Pentium III. A AMD deu origem (nessa geração) com a série K6, onde se

destacaram o K6-II e o K6-III. A sétima geração (2000) foi marcada pelo Pentium IV e pelo Atlhon (Intel e AMD). A oitava

geração (2001) é caracterizada pela IA-64 com o Itanium da Intel e o Hammer da AMD.

80286

A preocupação com o 286 foi manter a compatibilidade com o 8086 e o 8088. Para isso o 286 trabalha em dois

modos: modo real (8086) e modo protegido (286). No primeiro, o 286 funciona como um 8086 mais veloz e com ciclos de

barramento mais custos e no modo protegido o 286 possui recursos para multitarefa além da unidade de gerenciamento de

memória integrada.

Avanços do 80286:

Endereçamento de 16MB endereços (24 linhas de endereços);

Clock até 25mhz;

Instruções para ambiente multitarefa;

Barramento de 16 bits com 2 períodos de relógio por ciclo;

O problema dessa CPU foi a passagem de um modo de operação para o outro. Ao ligar a CPU ela adotava o modo real

e para entrar no protegido era via software. Uma vez no protegido para voltar ao modo real, só resetando a maquina.

80386

Com essa CPU melhorou-se o modo protegido e o gerenciador de memórias mantendo ainda certa compatibilidade

como 8086/8088 e 286. As principais características são:

Barramento de dados de 32bits (IA-32bits)

Endereçamento de 9GB (32 linhas)

Fila e instruções de 16 Bytes

Menor quantidade de períodos de clock por instrução.

Clock de 16 à 33 MHz, chegando à 40 MHz com o 386 da AMD

Softwares compatíveis com o 8086, 8088 e 286.

O 80386 usou o processo que a Intel chamou de CHMOS III, combinando a velocidade do HMOS com o baixo

consumo da CMOS. A CPU do 386 tinha um núcleo de 1,5 um o que permitia uma densidade de 275mil transistores. O grande

sucesso do 386 foi a arquitetura de 32 bits e o seu sistema de gerenciamento de memória usado posteriormente pelo Pentium.

O 386 possui um conjunto de registradores de 32 bits que são usados como acumuladores OFFSETES ou registradores de

dados. Cada registrador pode ser acessado em 32 bits (EAX), em 16 bits assim como o ponteiro de instrução (EIP). Seis

registradores de 16 bits implementam a segmentação da memória.

Além das flags herdadas do 8086 aparecem ainda as flags IOPL de dois bits usada no nível de privilégio dos

dispositivos de I/O, a flag NT usada em tarefas aninhadas multitarefa, a flag RF usada na depuração de programas, e a Flag

VM usada no modo virtual modo protegido. Assim como o 286, o 386 no modo real é o 8086 de 32 bits e no modo protegido

apresenta novos recursos de endereçamento de proteção e de gerenciamento de memória. O modo protegido existe um

submundo chamado modo virtual VM = HIGH e pode rodar programas escritos para o 8086 simultaneamente com aplicativos

no modo protegido.

20 de março de 2007

PIPELINE

É a técnica onde diversas unidades se interligam e comunicam de forma a obter maior rapidez e eficiência na

execução das operações elementares que compõe uma instrução. Executa-se uma instrução por vez, porém, no Pipeline da

CPU, já estão sendo processadas as próximas instruções em estágios distintos.

O 386 tem 6 unidades funcionais independentes que operam simultaneamente em seu Pipeline:

a. Unidade de Interface com o Barramento: Gerencia o tráfego externo da CPU. Lê as instruções, transfere

os dados entre CPU e memória e entre CPU e dispositivos de I/º

b. Unidade de Pré-Busca: Sempre que o Barramento está ocioso. Lê os próximos códigos mantendo cheia sua

fila de 16 bytes de códigos.

c. Unidade de Decodificação: Possui uma fila interna de 3 instruções e através de uma tabela converte as

instruções em microinstruções gerando microcódigos.

d. Unidade de Execução: através dos microcódigos executa as operações especificadas pelas instruções. Essa

unidade realiza as operações lógicas e aritméticas como também os deslocamentos.

e. Unidade de Segmentação e Unidade de Paginação: as duas juntas gerenciam a memória do 386.

OBS.: FIGURA 3.4 PÁGINA 81

BARRAMENTO DE ENDEREÇOS E DE DADOS

O esquema seguinte representa um esquema simplificado da organização de memória com o 386. Nesse caso exigia-se

quatro banco de memória de mesma capacidade.

As linhas *BEi controlavam o acesso de bytes, palavras de 16 bits ou palavras de 32 bits. Qualquer combinação de

*BEi é válida desde que se habilitem bancos consecutivos.

A tabela seguinte mostram as possíveis combinações de *BEi e as respectivas palavras acessadas por estas

combinações.

OBS.: FIGURA 3.8 PAGINA 83

Palavra

32

24

24

16

16

16

8

8

8

8

*BE3

0

0

1

0

1

1

0

1

1

1

*BE2

0

0

0

0

0

1

1

0

1

1

*BE1

0

0

0

1

0

0

1

1

0

1

*BE0

0

1

0

1

1

0

1

1

1

0

As linhas *BEi gera os sinais A1, A0 e *BHE de forma análoga à estudada no 8086. Essa lógica é dada da seguinte

forma: (figura)

Por exemplo: quando o 386 é avisado que será usado um barramento de dados de 16 bits, as linhas *BEi devem gerar

A1, A0 e *BHE. Habilita-se o banco associado ao *BEi menos significativo que estiver ativado. Se o índice i for em numero

Par esse *BE (i + 1) também estiver ativado, a transferência devera ser de 16 bits. Caso nem todos os *BEi ativados resultem

em ativação de um banco, não haverá outro jeito senão ciclos de barramento extras.

80486

Esse processador usa 1.200.000 transistores, uma unidade de gerenciamento de memória, um cache de 8KB e uma

unidade de ponto flutuante. Ele tinha o co-processador matemático com desempenho maior, pois este era integrado na mesma

pastilha da CPU. Nesta CPU houve uma mudança no sistema de Interface com o barramento transferindo-se dados em um

único período de relógio. Isso ficou conhecido como módulo rajada, que transferia até 16 bytes em 5 períodos de relógio.

Outro item importante do 486 é o recurso para o cache L2. Outras características do 486 que o levaram a ter um

aumento de desempenho são:

a. Fila de instruções de 32 bytes

b. Muitas instruções executadas em um único período de clock

c. Clocks de 25, 33, 50, 66 e 100 MHz

O Diagrama a seguir apresenta Pipeline do 486 com oito estágios (FIGURA 3.14 PAGINA 89)

O estágio decodificador é que permite a execução de algumas instruções em um único período de clock, esse estágio

calcula o endereço do operando e inicia seu acesso de forma que assim que a CPU necessitar do operando ela já estará

disponível na Cache. Um exemplo de ganho de performance é a seguinte:

O co-processador matemático 80387 para realizar operações Load/Store (Carregar/Guardar) gasta de 15 a 20 períodos

de relógios. Já no 786 com o co-processador integrado se gasta 3 períodos. Além disso, existe o Pipeline do 486 um par de

caminhos de 32 bits formando um canal de dados de 64 bits o que permite um rápido tráfego de dados. Isso só foi possível

graças ao processo que a Intel chamou de CHMDIV com linhas de um micron de espessura.

Para se ter uma idéia a pastilha do 486 mede 6,49 X 4,13 mm. Apareceram outras versões do 486 onde não existia a

unidade de ponto flutuante (mais barato) 486 SX. Esse não tinha o co-processador matemático. Aumentando-se a freqüência

dos clocks aumentou-se o custo de placas mãe. O aumento da freqüência trás três problemas:

a. Interferência eletromagnética: blindagem

b. Reflexões de sinais pelas linhas: sinal que bate e volta, evitadas no casamento de impedâncias

c. Retardos introduzidos por outros cis da placa mãe

Surgem então as CPU´s dobradoras e triplicadoras de velocidade como o 486 DX2/50 (25 para 50 MHZ), 486 DX2/66

(33 para 66 MHZ) e 486DX4 (33para 100MHZ). As CPUs DX2 permitiam que placas projetadas para 25 ou 33 MHz

pudessem receber uma CPU de 50 ou 66 MHz. Assim o fabricante poderia utilizar hardware mais barato (25 ou 33 MHZ) e

nele colocar CPU extremamente rápidas. Para se resolver o problema do clock utiliza-se um monoestável disparado tanto na

bora de subida quanto na de descida do clock, ou um circuito RC adequado. Gera-se dois pulsos para cada borda do relógio.

Sendo assim surge também as CPUs triplicadoras, como é o caso do 486 DX4. Além de triplicar o relógio essa CPU

tinha um cache interno de 16kb. Testes mostraram que o desempenho do DX4 100 era aproximado ao do P5/60MHZ.