Trabalho

de

Eletrônica

Digital

Famílias de Circuitos Lógicos

Centro Federal de Educação Tecnológica UNED Cubatão

Eletrônica Digital

I.

Famílias de Circuitos Lógicos

Introdução

Família de Circuitos Lógicos.

Entende-se por famílias de circuitos lógicos estruturas internas que nos

permitem a confecção desse bloco em circuitos integrados. Cada família lógica

utiliza determinados componentes em seus blocos e de acordo com este, a família

possuirá determinadas características relacionadas ao seu funcionamento.

Dentre as famílias de circuitos lógicos destacam-se:

TTL (transistor-transistor-logic).

CMOS (complementary mos).

RDTL ()

HTL (high-thershold-logic).

ECL (emither-coupled-logic)

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

2

Eletrônica Digital

I I.

I.

Famílias de Circuitos Lógicos

Índice

Introdução ____________________________________ 2

II. Índice ________________________________________ 3

Parâmetros mais Utilizados dos Circuitos Lógicos ____________ 4

Interface entre as Famílias Lógicas _______________________ 4

Sensibilidade de Níveis Lógicos de Tensão __________________ 5

III. Família HTML _________________________________ 5

Características principais da família HTL ___________________ 5

IV.

Família ECL __________________________________ 6

Características da família ECL ____________________________ 7

V. Família TTL ____________________________________ 7

54/74LXXX __________________________________________ 8

Série 74_____________________________________________ 8

Série 54_____________________________________________ 8

Características Gerais e Parâmetros da Família TTL ___________ 8

Tipos de Blocos da Família TTL __________________________ 10

Saída Open-Colletor ____________________________________________ 10

Saída Tri-State (Três Estados) ____________________________________ 11

Entrada Schimitt-Trigger _________________________________________ 12

Versões de Circuitos TTL _______________________________ 13

Circuitos Integrados TTL_______________________________ 15

Alguns tipos de circuitos integrados TTL __________________ 16

VI.

Família CMOS________________________________ 20

Características Gerais e Parâmetros da Família CMOS ________ 22

Circuitos Integrados CMOS _____________________________ 24

VII. Conclusão ________________ Error! Bookmark not defined.

VIII. Bibliografia _______________ Error! Bookmark not defined.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

3

Eletrônica Digital

Famílias de Circuitos Lógicos

Parâmetros mais Utilizados dos Circuitos Lógicos

VIH - Tensão de entrada alta. É um valor de tensão no terminal de

entrada que representa um nível alto para o sistema.

VIL - Tensão de entrada baixa. É um valor de tensão no terminal de

entrada que representa um nível baixo para o sistema.

VOH - Mínima tensão de saída alta. É a mínima tensão num terminal

de saída que ainda permite fornecer a corrente de saída alta especificada com a

tensão de alimentação no seu valor mínimo.

VOL - Máxima tensão de saída baixa. É a máxima tensão em um

terminal de saída que ainda permite a "absorção" da corrente de saída baixa

especificada.

IOS - Corrente de curto circuito na saída. É a corrente que flui por

um terminal de saída quando uma saída alta é conectada ao terra.

Interface entre as Famílias Lógicas

As interfaces entre os circuitos integrados muitas vezes não podem

ser feitas de maneira direta, ou seja, a saída de um circuito integrado conectada à

entrada de um circuito integrado de outra família por causa das diferenças entre as

características elétricas do circuito alimentador, ou o circuito que está fornecendo o

sinal de saída, e o circuito que está recebendo o sinal. Para essa finalidade, usa-se

um circuito de interface. O circuito de interface tem a função de compatibilizar as

características do circuitos alimentador com as características do circuito

alimentado.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

4

Eletrônica Digital

Famílias de Circuitos Lógicos

Sensibilidade de Níveis Lógicos de Tensão

Um circuito lógico interpreta como nível 1, uma tensão próxima a da

máxima e, como nível zero, uma tensão próxima ao terra. As famílias lógicas têm

uma faixa de trabalho diferente para as tensões de cada nível. Assim se tivermos,

por exemplo, uma família que interpreta como nível baixo tensões entre 0 e 0.8 V,

e como nível alto entre 2 V e 5 V. Se ela for conectada a saída de outra família que

tenha nível lógico alto com tensões entre 1.4 V e 5 V, essa diferença entre 2 V e

1.4 V pode causar erro de interpretação n entrada da primeira, pois1.4 V está

dentro da faixa indeterminada desta família.

III. Família HTML

A família HTML (high-tueshold logic) foi criada para atender

necessidade de circuitos com uma alta imunidade ao ruído. Esses circuitos

,geralmente ,são empregados nas em equipamentos industriais que trabalham em

locais de grande ruído(comutação de chaves, motores de indução, etc).Possuem

circuitos muito semelhantes à família DTL como veremos a seguir. O circuito básico

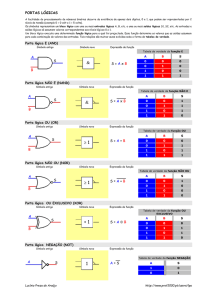

do seu bloco lógico principal, a porta NAND, é visto na figura 01 abaixo:

Figura 01

Como veremos o circuito tem um funcionamento análogo ao da

família DTL com a única diferença de possuir D3 como sendo um diodo zener, isso

fará com que aumente o potencial necessário para que T1 inicie a condução.

Características principais da família HTL

Como na família DTL, possui um bloco lógico principal a porta

NAND.

Possui um Fan-out Típico igual a 10.

A família HTL é de todas as famílias de circuitos lógicos a que

dissipa a maior potência.A potência dissipada por circuitos desta

família é de ordem de 60 mW.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

5

Eletrônica Digital

IV.

Famílias de Circuitos Lógicos

Devido à utilização de um diodo zener(D 3), necessitar-se-á de um

maior potencial nas entradas para que haja condução, isso fará

com que aumente a imunidade ao ruído.Essa é a família de

circuitos lógicos que possui maior imunidade ao ruído.

De todas as famílias que utilizam transistores como chaves, a

família HTL é a que possui maior tempo de atraso.

Família ECL

A família ECL (emiter-coupled-logic) utiliza nos circuitos o

acoplamento pelo emissor dos transistores. Esse fato faz com que os transistores

não trabalhem na região de saturação e traz como conseqüência um menor tempo

de resposta.

De todas as famílias lógicas, está é a que permite maior velocidade

de comutação.

Esta família apresenta dois blocos lógicos principais, a porta NOR e a

porta OU que serão obtidas a partir de um mesmo circuito, em duas saídas.

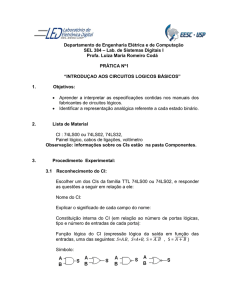

O circuito básico dos blocos principais é visto na figura 02 abaixo:

Figura 02

Esse circuito tem seu funcionamento baseado em um amplificador

diferencial. Sabendo-se disso , podemos dizer que quando ambas as entradas

estiverem em nível baixo(nível 0) os transistores T1 e T2 estarão no limiar da região

de corte, portanto I será pequeno e por isso o potencial de S 2 será alto.Sendo I um

valor baixo, diremos que I2 será um valor alto de modo a manter a corrente IE e

com isto o transistor T3 estará no limiar de saturação impondo assim o potencial de

S baixo. Quando pelo menos uma das entradas estiver com com

potencial

alto(nível 1) o seu respectivo transistor estará no limiar de saturação,com isso, I

será elevada, logo o potencial de S2 será baixo;sendo I elevado, I2 deverá ser

pequena de modo a manter a correspondente IE, com isto o transistor T 3 estará no

limiar do corte, impondo assim o potencial de S1 alto. Transpondo-se estas

situações para a tabela da verdade, teremos:

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

6

Eletrônica Digital

Famílias de Circuitos Lógicos

H-nível alto de

tensão.

L-Nível baixo de

tensão

A

L

L

H

H

B

L

H

L

H

S1

L

H

H

H

S2

H

L

L

L

Podemos notar na tabela que a saída S2 será o complemento da saída

S1, e mais, S1 segue a tabela de uma porta OU e portanto, S 2 segue uma tabela de

uma porta NOR.

Como sabemos, a partir de um bloco NOR podemos formar qualquer

outro tipo de bloco lógico.

Características da família ECL

V.

Blocos lógicos principais são a porta OU e a porta NOR.

Uma das vantagens do ECL é que possui um Fan-out igual a 25.

A potência dissipada pelos blocos dessa família é da ordem de 50

mW. Isso se dá pelo fato de nós não trabalharmos na região de

corte ou saturação e sim, na região ativa.

Apresenta uma boa imunidade ao ruído.

Como já foi dito, a grande vantagem da família ECL é de possuir

um tempo de atraso muito baixo, da ordem de 3ns.

Família TTL

Esta família é derivada da antiga família DTL, sendo o resultado de

inovações tecnológicas. Como a utilização nos seus circuitos internos de

transistores e bipolares de vários emissores também conhecidos como

multiemissores. Esta é uma família muito utilizada por causa de seu fácil manuseio

e a disponibilidade de uma série de circuitos integrados comerciais e padronizados.

Os circuitos da família TTL podem ser encontrados em duas séries

denominados: 74 (para uso comercial) e 54 para uso militar).

Primeiramente, os circuitos integrados eram fabricados para o uso

militar onde tamanho, consumo e potência eram preponderantes.

Mas no ano de 1964, surgiu a versão comercial a custo bem inferior.

Respeitando algumas especificações, os dispositivos 54 são compatíveis com a série

74.

Há também subdivisões da linha nesses dispositivos de acordo com

sua velocidade de comutação.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

7

Eletrônica Digital

Famílias de Circuitos Lógicos

54/74LXXX

Baixa potência. Dão o melhor produto velocidade versus potência,

entre todos os dispositivos lógicos. As resistências internas dos transistores do CI

são aumentadas, resultando numa menor dissipação de potência (1 mW por porta,

com retardo de 33nS por porta).

54/74HXXX – Alta velocidade. Os tempos de subida e descida

de pulsos são menores. Os transistores internos do CI são feitos

em configuração darlington. O retardo é de 6 ns por porta. A

desvantagem é que este tipo de circuito consome mais corrente

que o tipo comum.

54/74SXXX – Componentes com tecnologia schottky*. Ela

combina alta velocidade com baixo consumo.

Série 74

Identifica os dispositivos da família TTL de uso comercial.

Especificações:

Temperatura

Tensão de Alimentação

0 a 70 ºC

4,75 a 5,25V (5V +

- 10%)

Mas é importante lembrar que:

Os circuitos integrados da família AS e ALS de alguns fabricantes, a

tensão de alimentação pode estar compreendida entre 4,5V e 5,5V (5V +10%).

-

Série 54

Identifica os dispositivos da família TTL de uso militar.

Apesar da série 54 tenha as mesmas portas lógicas da série 74, suas

especificações técnicas são mais rígidas.

Especificações:

Temperatura

Tensão de Alimentação

-55 a 125 ºC

4,5 a 5,5V (5V +

- 10%)

Características Gerais e Parâmetros da Família TTL

Veja abaixo os principais parâmetros encontrados nos manuais em

nomenclaturas originais:

1. Alimentação (Vcc): Na família TTL temos para todos os blocos

de uma alimentação de 5V. Para a série 54 temos Vcc mínimo =

4,5V e Vcc máximo 5,5V que são os valores dentro da tolerância

permitida por esta série. No caso da série 74, o Vcc mínimo =

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

8

Eletrônica Digital

Famílias de Circuitos Lógicos

4,75V e Vcc máximo = 5,25V, sendo os valores máximos e

mínimos da tolerância da série 74.

2. Veja na tabela a baixo, os níveis de entrada e saída para a versão

padrão TTL Standard:

Parâmetros

VIL

VOL

VIH

VOH

IOL

IIL

IOH

IIH

TTL Standard

Valores

0,8

0,4

2,0

2,4

16

1,6

400

40

Unidade

V

V

V

V

mA

mA

A

A

3. Fan-out: o Fan-out em sua versão padrão é igual a 10, ou seja,

podemos ligar à saída deste bloco no máximo outros 10 blocos

similares. Este valor é generalizado para toda a família TTL.

4. Tempo de atraso de propagação: O tempo varia de acordo

com a versão que for utilizada, sendo o valor médio aproximado

de ordem de 10ns na versão mais comum.

Parâmetros

TPLH

tPHL

5.

TTL Standard

V. Típico

11

7

Unidade

ns

ns

Imunidade ao ruído: A margem correta de imunidade ao ruído

específica para a família TTL é obtida supondo a ligação da saída

de um bloco para a entrada de outro, sendo definida pela

margem de segurança colocada pelo fabricante entre os

parâmetros de entrada e saída. É calculada pela diferença de

parâmetros relativos a esses níveis de tensão (margem de

imunidade ao ruído DC). Então, temos:

No nível 1: VRH = VOH(mínimo) – VIH(mínimo) = 2,4 – 2,0 =

0,4V

No nível 0: VRL = VIL(máximo) – VOL(máximo) = 0,8 – 0,4 =

0,4V

VR = 0,4V

Portanto, a margem de imunidade ao ruído para a família TTL é

igual a 0,4V, sendo considerada baixa em relação a família CMOS.

6. Potência Dissipada: A família TTL tem um consumo médio de

potência de 10mW por porta na sua versão mais comum.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

9

Eletrônica Digital

Famílias de Circuitos Lógicos

Tipos de Blocos da Família TTL

Esta é uma das características da família TTL, que através de suas

séries possui blocos que estão disponíveis no mercado de componentes, com uma

vasta variação. Vamos destacar alguns deles como os blocos open-colletor, tristate e schimitt-trigger.

Saída Open-Colletor

Na família TTL há alguns blocos lógicos montados em open-colletor

(coletor aberto). Os circuitos destes tem semelhança aos convencionais, mas com

uma única diferença de não Ter em seu interior o resistor de coletor ligado ao

+Vcc. Ele deve ser ligado externamente quando este bloco for utilizado. Abaixo, a

figura 03, mostra um circuito interno de uma porta NE (TTL) open-colletor:

+Vcc

R1

R2

Rexterno

T1

S

T2

R3

Figura 03

Esta configuração possibilita o controle externo da corrente do coletor

de saída e, proporcionando o aumento do fan-out, além de poder habilitar saídas

diferentes interligadas entre si (num mesmo resistor coletor), podendo assumir

níveis lógicos opostos sem provocar danos.

A grande desvantagem deste tipo de saída é sua baixa velocidade de

chaveamento (mudança de nível lógico).

A figura 04 na próxima página, mostra a ligação por uma função E,

contendo ao lado a tabela da verdade e a simbologia utilizadas para se obter uma

função E através de blocos open-colletor.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

10

Eletrônica Digital

Famílias de Circuitos Lógicos

+Vcc

Tabela da Verdade

Rexterno

S1

0

0

1

1

E por fio

Bloco 1

S

S2

0

1

0

1

S

0

0

0

1

Bloco 2

Figura 04

Podemos notar que, o nível 0 é obtido pela saturação de cada

transistor ou por ambos, conforme a função lógica de cada bloco, sendo respectiva

corrente de coletor fornecida pelo mesmo resistor colocado na extremidade. O nível

1 é obtido pelo corte de ambos.

Podemos citar como outro tipo de aplicação, o uso muito comum de

saídas de open-colletor para ativar displays de 7 segmentos a led, possibilitando o

controle de luminosidade pelo resistor de coletor calculado e colocado na

externamente.

Saída Tri-State (Três Estados)

Podemos dizer também three-state ou 3-state, que estes modos

também estão corretos.

A configuração que pode fazer com que ela apresente uma alta

impendância (terceiro estado) em relação a linha na qual ela está conectada, ou

seja, para ativar o tri-state, o bloco específico possui um terminal que, conforme o

nível lógico assumido, faz a saída permanecer ou não em alta impendância. Para

entendermos melhor, observe na figura 05 abaixo, o circuito simplificado de uma

porta NE (TTL) de duas entradas com saída tri-state.

+Vcc

R1

A

B

G

X2

X1

T3

T2

T1

D2

R4

R2

D3

D1

T4

S

R3

Figura 05

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

11

Eletrônica Digital

Famílias de Circuitos Lógicos

No circuito da figura 05, da página anterior, se aplicarmos nível 1 ao

terminal de entrada de controle de saída (G) ou o deixarmos em aberto, o circuito

funcionará normalmente como uma porta NE, pois D2 e D3, estarão cortados. Se, no

entanto, aplicarmos nível 0, devido à respectiva condução de corrente pelos

mesmos diodos, os pontos X1 e X2 cairão para baixos potenciais, levando T2, T3 e T4

para a situação de corte. O terminal de saída, neste caso, será desligado do circuito

ocasionando o estado de alta impendância.

Na família TTL, as saídas tri-state são encontradas fazendo parte de

vários dispositivos, porém, isoladamente como portas, estão disponíveis apenas

como buffers comuns e inversores.

Os dispositivos com saídas de tri-state tem várias aplicações, sendo

principalmente em sistemas com microprocessadores, onde vários circuitos

integrados usam o mesmo conjunto de fios de forma compartilhada, assim,

formando a via de dados do sistema.

Entrada Schimitt-Trigger

Estes dispositivos também são encontrados na família TTL. Este tipo

de bloco possibilita tornar rápidas as variações lentas dos níveis de tensão de

determinados sinais a serem aplicados à sua entrada, causando na saída o

aparecimento de uma onda quadrada bem definida. Ou seja, este tipo de bloco,

além de realizar sua função lógica, quadra o sinal aplicado a entrada, desde que

sejam respeitados os parâmetros mínimos e máximos de tensão especificados para

cada bloco. O bloco irá considerar iguais a 0, os valores dde entrada abaixo do

especificado por VT - (Negative-Going Thershould Voltage) ou limiar negativo

de tensão, e irá considerar iguais a 1, os valores acima de VT - (Positive-Going

Thershould Voltage) ou limiarr positivo de tensão.

Podemos dizer em outras palavras que, este bloco recebe o sinal da

forma como ele é gerado(pulso distorcido, com ruídos, etc.) e isto pode causar

vários problemas durante o chaveamento dos dispositivos, tais como:

Dispositivos sensíveis à borda de subida podem não operar;

Dispositivos polarizados na região ativa por longo tempo podem

tornar-se instáveis;

Atrasos de propagação tornam-se de difícil previsão.

Abaixo, na figura 06, podemos observar um inversor TTL schimitttrigger (a) e a ação sobre um sinal de variação lenta aplicado à sua entrada (b)

VT+

E

S

VTS

(a)

(b)

Figura 06

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

12

Eletrônica Digital

Famílias de Circuitos Lógicos

O símbolo

(histerese) presente no interior do inversor (ver

figura 06 (a)) é utilizado em manuais de fabricantes para identificar as portas que

executam a função de schimitt-trigger, sendo atribuído devido a aparência da

característica de transferência do bloco. Veja esta curva e os valores práticos dos

parâmetros VT- e VT+ , a figura 07 mostra a característica de transferência típica

do circuito integrado TTL 7414 (6 inversores schimitt-trigger).

V0 (V)

4,0

VT-

VT+

3,0

2,0

0,4

1,0

0

0,4

0,8

1,2

1,6

2,0

V1 (V)

Entrada

Figura 07

Por este gráfico podemos notar que, para a saída assumir nível 0 (VOL

= 0,2V) é necessário que a variação de entrada atinja aproximadamente V T+ =

1,7V, e para assumir nível 1 (VOH = 3,4V), é necessário que a variação de entrada

caia abaixo de VT- = 0,9V aproximadamente.

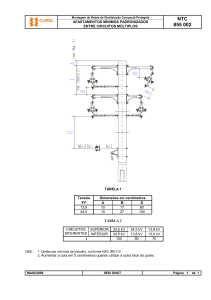

Versões de Circuitos TTL

Existem outros tipos de blocos TTL além dos blocos mais comuns

(Standard), com outras versões de circuitos com finalidade de atender a

solicitações de ordem prática nos parâmetros relativos à velocidade e consumo de

potência. Veja a tabela na próxima página, que mostra um quadro comparativo

com as versões, identificações, vantagens e desvantagens desses blocos:

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

13

Eletrônica Digital

Famílias de Circuitos Lógicos

Tempo de

atraso de

propagação

típico por

porta

Freqüência

Consumo de

de clock

potência por

máxima

Observações

porta

para flip-flop

Versão

Identificação

da série

Standard

54/74

10ns

10mW

35MHz

Comum

Low Power

54L/74L

33ns

1mW

3MHz

Baixíssimo

consumo

Hi Speed

54H/74H

6ns

22mW

50MHz

Alta

velocidade

Schottky

54S/74S

3ns

19mW

125MHz

Altíssima

velocidade

54AS/74AS

1,5ns

8,5mW

200MHz

54LS/74LS

10ns

2mW

45MHz

Advanced

Schottky

Low Power

Schottky

Advanced

Low Power

Schottky

54ALS/

74ALS

4ns

1mW

70MHz

Altíssima

velocidade e

baixo consumo

Baixíssimo

consumo

Altíssima

velocidade e

baixíssimo

consumo

Estes valores são válidos para circuitos integrados de portas NE e

servem apenas para comparações entre as versões, sendo estimados a partir de

faixas disponíveis nos manuais comerciais de diversos fabricantes.

Os dados do quadro, nos possibilita a comparação em termos de

velocidade e consumo de potência, tomando como ponto de referência a versão

comum, em seguida da versão de baixo consumo (L), e de alta velocidade (H).

Essas versões são diferentes entre si devido a alterações introduzidas nos circuitos

e nos valores de seus componentes internos. A partir deste passo, as versões do

quadro como podemos ver, os circuitos apresentam variações sobre a tecnologia

Schottky.

Nesta versão, é utilizado em seus circuitos o diodo Schottky, que é

um elemeto semicondutor construído em metal com um lado da junção internapara

aumentar a velocidade de comutação, que está devidamente colocado entre base e

coletor de um transistor, formando um conjunto denominado Transistor

Schottky.

Quando este conjunto é utilizado para chaveamento, não atinge a

saturação por completo, devido à ligação, apresentando um tempo de comutação

extremamente baixo e consequentemente uma altíssima velocidade de trabalho. A

figura 08 na próxima página, nos mostra a ligação de um diodo Schottky em um

transistor bipolar para formar o referido conjunto (a) e a simbologia que é utilizada

por este (b).

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

14

Eletrônica Digital

Famílias de Circuitos Lógicos

(a)

(b)

Figura 08

As alterações feitas nos circuitos e nos valores dos componentes,

produziam em relação à versão Schottky (S), uma variação de menor consumo

(LS), e nas versões Schottky Avançadas (AS e ALS), com uma grande melhora no

desempenho total, principalmente no produto velocidade-consumo, constituindo-se

nos menores entre todas as versões existentes.

Circuitos Integrados TTL

Esta família possui uma vasta variação de circuitos integrados

padronizados com configurações de pinagens disponíveis nos manuais dos

fabricantes. São circuitos integrados que possuem 14 pinos ou mais, conforme a

complexidade do circuito agregado, com encapsulamentos denominados DIP

(Dual-In-Line Package), cuja identificação da disposição dos terminais se faz

através da vista superior, em sentido antí-horário a partir de uma marca de

referência no encapsulamento do circuito integrado.

Veja abaixo as marcas de referência dos circuitos integrados:

Marca

de

Referência

Marca

de

Referência

No caso do circuito integrado acima, podemos verificar que a sua

alimentação é feita através do pino 14: +Vcc e do pino 7: terra ou GND (ground).

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

15

Eletrônica Digital

Famílias de Circuitos Lógicos

Alguns tipos de circuitos integrados TTL

7400 - 04 portas NAND de 02 entradas

7401 - 04 portas NAND de 02

entradas com saídas em coletor aberto

7402 - 04 portas NOR de 02 entradas

7403 - 04 portas NAND de 02

entradas com saídas em coletor aberto

7404 - 06 portas INVERSORAS

7404 - 06 portas INVERSORAS

7405 - 06 portas INVERSORAS com saídas

em coletor aberto

7406 - 06 portas INVERSORAS

Buffers/Drivers com saídas em coletor aberto

7407 - 06 portas BUFFERS/DRIVERS

com saídas em coletor aberto

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

16

Eletrônica Digital

Famílias de Circuitos Lógicos

7408 - 04 portas AND de 02 entradas

7409 - 04 portas AND de 02 entradas

com saídas em coletor aberto

7410 - 03 portas NAND de 03 entradas

7411 - 03 portas AND de 03 entradas

7412 - 03 portas NAND de 03 entradas

com saídas em coletor aberto

7413 - 02 portas NAND de 04

entradas Schmitt-Triggers

7414 - 06 portas INVERSORAS

Schmitt-Triggers

7421 - 02 portas AND de 04 entradas

7420 - 02 portas NAND de 04 entradas

7425 - 02 portas NOR de 04 entradas

com Strobe

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

17

Eletrônica Digital

Famílias de Circuitos Lógicos

7427 - 03 portas NOR de 03 entradas

7430 - 01 porta NAND de 08 entradas

7432 - 04 portas OR de 02 entradas

7433 - 04 portas NOR de 02 entradas

com saídas em coletor aberto

7437 - 04 portas NAND de 02 entradas

Buffer

7438 - 04 portas NAND de 02 entradas

com saídas em coletor aberto

7440 - 02 portas NAND de 04 entradas

com saídas em coletor aberto

7451 - 02 portas AND/NOR de 04

entradas

7473 - 02 FLIP FLOPS JK com entradas

de Clear

7474 - 02 FLIP FLOPS D com entradas

de Preset e Clear

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

18

Eletrônica Digital

7475 - 04 LACTCHES BIESTÁVEIS

7486 - 04 portas XOR de 02 entradas

Famílias de Circuitos Lógicos

7483 - SOMADOR PLENO DE 04 BITS

7488 - MEMÓRIA de apenas leitura de

256 BITs com saídas em coletor aberto

7489 - MEMÓRIA de escrita e leitura

7490 - CONTADOR de década

7491 - SHIFT REGISTER de 08 BITs

7495 - SHIFT REGISTER de 04 BITs

74125 - 04 BUFFER TRI STATE

74126 - 04 BUFFER TRI STATE

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

19

Eletrônica Digital

74138 - 01 DECODER 3 TO 8

VI.

Famílias de Circuitos Lógicos

74139 - 02 DECODER 2 TO 4

Família CMOS

A outra família de externa importância a ser abordada é a CMOS

(Complementary MOS). Trata-se de ima família que tem seus circuitos construídos

por transistores MOS-FET complementares do tipo canal N e canal P.Suas

configurações básicas permitem obter-se uma série de vantagens, tais como: alto

Fan-Out, alta margem de imunidade ao ruídoe baixíssimo consumo, sendo esta

uma de suas mais importante características.

Vamos, a seguir, analisar o funcionamento dos blocos lógicos

principais desta família que são as portas NOU e NE. A figura 09 logo abaixo, nos

mostra o circuito básico de uma porta NOU CMOS.

Figura 09

Quando ambas as entradas estiverem em 0 (potencial do terra), os

MOS-FET canal P, M1 e M2 estarão conduzindo e os Mos-FET canal N, M3 e M4

estarão cortados. Isso fará com que a tensão de saída assuma valor igual a +Vdd

(nível 1). Quando pelo menos uma das entradas estiver em +Vdd (nível 1),

teremos o respectivo MOS-FET canal N, M3 ou M4 conduzindo, fazendo com que na

saída tenhamos uma tensão igual a 0. Transpondo estas situações para uma tabela

verdade, concluímos que o circuito comporta-se como uma porta NOU:

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

20

Eletrônica Digital

Famílias de Circuitos Lógicos

A

0

0

1

1

B

0

1

0

1

S

1

0

0

0

Vamos analisar agora, o funcionamento da porta NE CMOS. O circuito

básico é visto na figura 10:

Figura 10

Quando pelo menos uma das entradas estiver em 0, o respectivo

MOS-FET canal N, M3 ou M4 estará cortado e o respectivo MOS-FET canal P, M1 ou

M2 estará conduzido, logo, teremos na saída uma tensão igual a VDD (nível 1).

Quando ambas as entradas estiverem em +VDD (nível 1), tanto M3 como M4

estarão conduzindo, ficando M1 e M2 cortados, logo, teremos na saída uma tensão

igual a 0. Transpondo estas situações para uma tabela verdade concluímos que o

circuto comporta-se como uma porta NE:

A

0

0

1

1

B

0

1

0

1

S

1

1

1

0

Convém ressaltar que a partir destes circuitos básicos o fabricante

pode estruturar, internamente no circuito integrado, qualquer outro bloco

mantendo as mesmas características de entrada e saída.

Um outro ponto importante a ser ressaltado é que ao contrário da

família TTL, não é aconselhável deixar terminais de entrada em vazio nas portas

CMOS, pois nesta situação, estes se tornam susceptíveis à captação de cargas

estáticas e ruídos indesejáveis, causando pela polarização errônea dos dispositivos,

um aumento da dissipação de potência e consequentemente sobreaquecimento. Os

terminais não utilizados devem ser conectados, conforme o caso da função lógica

envolvida, ao terra ou Vdd do circuito.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

21

Eletrônica Digital

Famílias de Circuitos Lógicos

Características Gerais e Parâmetros da Família CMOS

A família CMOS possui circuitos integrados disponíveis nas séries

comerciais 4000A, 4000B e 54/74C, sendo esta ultima semelhante à TTL na

pinagem dos circuitos integrados e função dos blocos disponíveis. Além destas, a

família CMOS também possui versões de alta velocidade e melhor desempenho:

74HC/74HCT (High-speed CMOS), sendo a HCT especialmente desenvolvida para

atuar com parâmetros de tensões compatíveis co TTL-LS e as apropriadas para

operar com baixa tensão de alimentação: 74LV/74VC (Low Voltage CMOS).

Os circuitos integrados CMOS são dimensionados para operar na

faixa de temperatura de -40 a +85 C nas séries comuns, e nas variações de uso

profissional (militar) na faixa de -55 a +125 C.

Veja logo abaixo, os principais parâmetros encontrados nos manuais

em nomenclaturas originais:

1. Alimentação (Vdd): Quanto á tensão de alimentação, esta

família permite para as séries 4000 e 74C operam na faixa de 3V

a 15V, para a versão HC de 2V a 6V e para a HCT de 4,5V a 5,5V.

Para as séries de baixa voltagem, a faixa de 1V a 3,6V para a LV

e 1,2V a 3,6V para a LVC, sendo estas especialmente projetados

para operar com 3,3V, tensão de vários sistemas atuais. Podemos

notar que esta família e suas versões apresentam a vantagem de

possuir uma larga faixa de tensão de alimentação, não

necessitando de regulagem precisa na fonte como no caso da

TTL.

2. Níveis de tensões e correntes de entrada e saída: Os blocos

da família CMOS apresentam estes níveis, especificados nos

manuais, com variações em função da versão e tipo de bloco

utilizado. De maneira geral, apresentam nas entradas, valores de

Vil (máx.) iguais a 30% do Vdd e Vih (min.) iguais a 70% do Vdd,

com exceção da versão HCT que possui estes níveis iguais a TTLLS. Nas saídas dos blocos, devido principalmente á baixa

absorção de corrente na ligação com o bloco seguinte (alta

resistência de entrada), apresentam valores muito próximos a 0

(Vol max.) e Vdd (Voh min.). A tabela 9.14 apresenta os valores

de tensões e correntes para a série 4000B, operando com Vdd

igual a 5V.

Parâmetros

Vil

Vol

Vih

Voh

Iol

Iil

Ioh

Iih

CMOS 4000B

Valores

1,5

0,05

3,5

4,95

0,4

1

0,4

1

Unidade

V

V

V

V

MA

A

MA

A

3. Fan-Out: Nesta família, de modo generalizado, Fan-Out é igual a

50, porém varia conforme as versões empregadas. Este valor

considerável é devido principalmente á pouca deriva da corrente

de saída, em função da alta resistência de entrada dos

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

22

Eletrônica Digital

Famílias de Circuitos Lógicos

dispositivos CMOS conextados, sendo a limitação causada pela

ação das capacitâncias de entrada dos blocos subseqüentes

somados. Devido à compatibilidade de algumas versões com TTL,

é comum nos manuais, encontrar este parâmetro definido para

um carregamento da saída com TTL-LS, sendo este um menor

valor (Fan-Out = 10 para HC/HCT).

4. Tempo de atraso de propagação: Nas séries mais comuns, o

tempo de atraso de propagação médio é da ordem de 90ns,

constituindo-se em uma grande desvantagem. O problema foi

superado com o aparecimento das versões apropriadas para uso

em alta velocidade (HC/HCT), com parâmetros compatíveis com

os das versões TTL para a mesma finalidade. Para exemplificar, a

tabela 9.15 apresenta os parâmetros de velocidades para a série

básica e as versões citadas, com tensão de alimentação igual a

5V.

Versão

4000B

HC/HCT

Tempo de atraso

de propagação

típico por porta

90 ns

8 ns

Freqüência de

clock máxima para

flip-flop

12 MHz

55 MHz

5. Imunidade ao Ruído: A margem de imunidade ao ruído para a

família CMOS é igual a 45% de Vdd, sendo muito alta se

comparada com a família TTL. Devido a isso, estes blocos são

adequados para ser utilizados em circuitos que operam em

sistemas ou ambientes de alto nível de ruído.

6. Potência Dissipada: O consumo de potência da família CMOS

(com Vdd=5V) é da ordem de 1nW por porta na série 4000 e

2,5nW por porta na versão 74HC, sendo estes valores muito

baixos, caracterizando-se em mais uma grande vantagem desta

família.

7. Manuseio: A família CMOS, ao contrario da TTL, possui

problemas com o manuseio dos circuitos integrados que devido à

ação da eletricidade de estática, provoca a degradação das

junções internas dos chips, comprometendo sua vida útil. A

danificação total do bloco pode só acontecer após um certo tempo

de uso, causando sérios transtornos ao fabricante do sistemas no

qual o componente está engajado.

Para contornar o problema, possibilitando um manuseio mais seguro,

existe no mercado uma série de dispositivos antiestáticos (pulseiras de

aterramento, pisos, borrachas de bancada, estações de solda, etc.), sendo inclusive

os circuitos integrados comercializados em embalagens com isolação apropriada.

As versões mais recentes desta família possuem internamente nas

entradas e saídas dos blocos, diodos de proteção para evitar a ação da eletricidade

estática, porém, aconselha-se seguir da mesma forma as normas de manuseio

apropriadas.

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

23

Eletrônica Digital

Famílias de Circuitos Lógicos

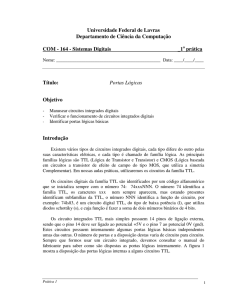

Circuitos Integrados CMOS

Da mesma forma que na TTL, a família CMOS colocou no mercado

uma série de circuitos integrados padronizados com configurações de pinagens

disponíveis nos manuais dos fabricantes.Para exemplificar, a figura 9.22 apresenta

a pinagem do circuito integrado 4001B (4 NOU com 2 entradas) e do

74HC04/74HCT04 (6 inversores), sendo estes últimos de mesma pinagem que o

7404 da família TTL.

4001

04 portas NOR de 02 entradas

7404

06 portas INVERSORAS

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

24

Eletrônica Digital

Famílias de Circuitos Lógicos

VII. Bibliografia.

Livros 01 e 02: Elementos da Eletrônica Digital

Edições: 13º e 30º Edição Revisada

Autores: Francisco Gabriel Capuano e

Ivan Valeije Idoeta

Editora: Érica

Livros 03: Manual de Circuitos Integrados TTL

Edição: Não consta

Autores: Eduardo Cesar Alves Cruz e

Luiz Carlos da Cunha e Silva

Editora: Érica

Livros 04: Circuitos Digitais

Edição: Não consta

Autores: Eduardo Cesar Alves Cruz

Antonio Carlos de Lourenço

Sabrina Rodero Ferreira

Salomão Choueri Júnior

Editora: Érica

www.triac.cjb.net

www.eletronica1.cjb.net

www.members.xoom.com/curtocircuit

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

25

Eletrônica Digital

Famílias de Circuitos Lógicos

Ricardo Gouveia nº 26; Wagner S. Pires nº 34; Wenderson Luis nº 35; I – 111

26