Universidade Federal de Campina Grande

Centro de Engenharia Elétrica e Informática

Departamento de Engenharia Elétrica

____________________________________________________________________________________________________________________

Laboratório de Circuitos Lógicos

Nome: _____________________________________________________________________________________

1o Experimento: Portas Lógicas

Este modelo está de acordo com as regras Como Fazer a Preparação do Relatório e Como Realizar a Montagem e a

Verificação do Funcionamento, que deverão ser seguidas para a preparação dos relatórios dos demais experimentos. O

Relatório deve ser integralmente preparado com antecedência, em papel de tamanho A4, e, no início da aula de laboratório,

deve ser obtido o visto do professor na capa. As partes referentes à parte prática deverão ser completadas durante a

realização dos experimentos, no próprio laboratório e também deverá ser obtido o visto para a verificação de cada montagem.

O relatório completo deverá ser entregue ao final da aula.

Observação: completar as áreas sombreadas.

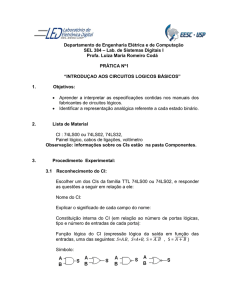

1. Objetivos

Usar a Lógica e a Álgebra de Boole de 2 Valores para modelar Sistemas Digitais;

Descrever as Funções Lógicas Elementares e as Portas Lógicas correspondentes;

Utilizar Expressões Lógicas, Blocos Funcionais, Diagramas Lógicos, Tabelas da

Verdade, Tabelas de Funcionamento, Diagramas de Pinos e Diagramas Elétricos;

Implementar Funções Lógicas (gerais) a partir de funções lógicas elementares, usando a

Lei da Associatividade;

Descrever as principais características dos Circuitos Integrados Digitais da Família

Lógica TTL e das Subfamílias TTL;

Realizar a Montagem de um Circuito Lógico, a Verificação de seu Funcionamento, e a

Desmontagem desse circuito, tomando os cuidados necessários;

Realizar a Depuração Lógica de um circuito lógico que não funcione como esperado;

Elaborar um Relatório que descreva um experimento de Circuitos Lógicos.

2. Material Utilizado

Módulo de Treinamento. Identificação:

CI’s: 7402, 7408 e 7486.

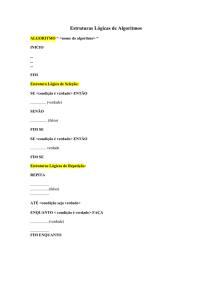

3. Resumo da Teoria

As variáveis dos Sistemas Digitais Binários (0 e 1), dos Sistemas Lógicos (F e V) e dos

Sistemas Booleanos (0 e 1) podem ser usadas de modo análogo, pois podem assumir apenas dois

valores.

Portas lógicas são dispositivos usados para implementar funções lógicas elementares. As

funções elementares disponíveis são: NEGAÇÃO (Inversor), IDENTIDADE (Buffer), AND, NAND,

OR, NOR, XOR e XNOR. Essas funções/portas podem ser representadas por expressões lógicas,

por tabelas da verdade ou funcionais, e, graficamente, por blocos funcionais lógicos. Os circuitos

integrados usados para implementá-las são representados por diagramas de pinos.

UFCG/DEE — Laboratório de Circuitos Lógicos – 06.2

2/7

Essas portas podem ser associadas para implementar uma função lógica geral, que também

pode ser representada por um Bloco Lógico. Entretanto, esse bloco corresponde a um diagrama de

blocos, que constitui o Diagrama Lógico e representa a associação/interligação de portas que

constitui o Circuito Lógico. Ao Diagrama Lógico deve corresponder, integralmente, um Diagrama

Elétrico, que mostra como os pinos são usados.

Os circuitos integrados usados no laboratório são da família TTL, série 74. Com relação ao

estágio de saída, existem três tipos de implementações para uma porta lógica: saída normal, saída

a coletor aberto e saída triestado. Dentre as várias subfamílias existentes, serão usadas a TTL

padrão, a LS (Schottky de baixa potência) e a L (baixa potência), com estágio de saída normal

(totem-pole).

Ao usar portas lógicas com saída normal é necessário tomar cuidado para não ligar saídas

entre si, o que pode danificar o circuito. Portas lógicas com saída com coletor aberto devem ter

sua saída conectada a uma fonte de tensão através de um resistor externo. Portas lógicas com

saída triestado possuem uma entrada adicional que controla o funcionamento da porta. Quando

essa entrada está ativada a porta funciona normalmente, quando está desativada a saída fica

flutuando.

As principais características de algumas subfamílias TTL são dadas na Tabela 1.

Tabela 1 - Principais Características das Subfamílias TTL

Definição

7400

74L00

Símbolo

VCC

VOH

VIH

VOL

VIL

IOL

IIL

TD

74LS00

Un.

Tensão de alimentação (NOM)

Tensão de saída em nível alto (MIN)

Tensão de entrada em nível alto (MIN)

Tensão de saída em nível baixo (MAX)

Tensão de entrada em nível baixo (MAX)

Corrente de saída em nível baixo (MAX)

Corrente de entrada em nível baixo (MAX)

Fan-out para a própria subfamília

Tempo de Atraso: TPLH /TPHL (MAX)

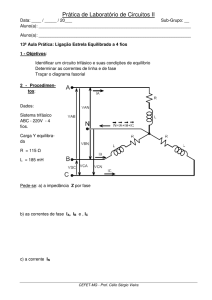

4. Montagens

1a Montagem: Porta NOR de duas entradas

a) Descrição do Funcionamento

A porta NOR implementa a função lógica que é a negação do OR, ou seja, o valor da saída é

1 se e somente se os valores de todas as entradas forem 0 . Essa porta pode ser representada pelo

diagrama lógico (que contém apenas um bloco funcional lógico) e pela tabela da verdade dados

abaixo, e corresponde à seguinte expressão lógica: S A B .

A

0

0

1

1

Diagrama Lógico

UFCG/DEE — Laboratório de Circuitos Lógicos – 06.2

B

0

1

0

1

S

Tabela da Verdade

3/7

b) Diagrama Elétrico

c) Verificação do Funcionamento

A

0

0

1

1

B

0

1

0

1

S

2a Montagem: Porta AND de três entradas

a) Descrição do Funcionamento

Para esta porta, o valor da saída é 1 se e somente se os valores de todas as entradas forem 1.

Como a função lógica AND é associativa, é possível obter uma função de três variáveis a partir de

duas portas AND de duas entradas, pois S = A.B.C = (A.B).C . Essa expressão corresponde ao

diagrama lógico e à tabela da verdade dados abaixo.

A

0

0

0

0

1

1

1

1

Diagrama Lógico

b) Diagrama Elétrico

UFCG/DEE — Laboratório de Circuitos Lógicos – 06.2

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

AB

S

Tabela da Verdade

4/7

c) Verificação do Funcionamento

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

S

3a Montagem: Porta XOR/XNOR

a) Descrição do Funcionamento

Como a função lógica XOR é associativa, a expressão lógica correspondente ao circuito

desta montagem, cujo diagrama lógico é dado abaixo, pode ser escrita da seguinte forma: Z =

(AB) C = _____________________ , ou seja, este circuito corresponde a uma função XOR de

três variáveis obtida a partir de duas portas XOR de duas entradas (modo de operação 1).

Realmente, a tabela da verdade para esse modo, construída abaixo, comprova esse fato, pois a

função XOR, com qualquer número de entradas, pode ser interpretada da seguinte forma: “o valor

da saída é 1 se e somente se for ímpar o número de entradas que valem 1”.

Alternativamente, a entrada C pode ser usada como uma entrada de controle para

selecionar duas diferentes funções para a porta XOR de saída: se C = 0 , ela implementa a função

identidade , ou seja, Z = Y C = _________________ = _______ , enquanto que, se C = 1 , ela

implementa a função negação, ou seja, Z = Y C = ________________ = _______ .

Assim, para C = 0, que corresponde ao modo de operação 2, é possível implementar uma

função XOR de duas entradas, pois, usando a associatividade e a função identidade, Z = A (B0)

=_______________________ = AB . Realmente, a tabela da verdade para esse modo, construída

abaixo, comprova esse fato, pois “a saída vale 1 se as entradas forem diferentes” (caso particular

para o XOR de duas entradas).

Por outro lado, para C = 1, que corresponde ao modo de operação 3, é possível implementar

uma função XNOR de duas entradas (equivalência ou coincidência), pois, usando a associatividade

e a função negação, Z A (B 1) _______________________ A B . Realmente, a tabela

da verdade para esse modo, construída abaixo, comprova esse fato, pois “a saída vale 1 se as

entradas forem iguais” (caso particular para o XNOR de duas entradas).

Y

Diagrama Lógico

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

Modo 1

C AB

0

1

0

1

0

1

0

1

UFCG/DEE — Laboratório de Circuitos Lógicos – 06.2

Z

Modo 2

C=0

A B AB

0 0

0 1

1 0

1 1

Z

Modo 3

C=1

A B AB

0 0

0 1

1 0

1 1

Z

5/7

b) Diagrama Elétrico

c) Verificação do Funcionamento

Modo 1

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Modo 2

C=0

Modo 3

C=1

Z

A

0

0

1

1

B

Z

0

1

0

1

5. Anexo: Mapa de Planejamento das Montagens

UFCG/DEE — Laboratório de Circuitos Lógicos – 06.2

A

0

0

1

1

B

0

1

0

1

Z

6/7

6. Conclusões

7. Questões

a) Comentar a diferença entre diagrama lógico, diagrama de pinos e diagrama elétrico.

O diagrama lógico é uma maneira gráfica de exibir expressões booleanas ou lógicas, que

fornece uma idéia clara do fluxo de dados ou dos sinais.

O diagrama de pinos mostra, para cada CI, qual a função de cada pino.

O diagrama elétrico representa a implementação física, explicitando com clareza como os

CI’s estão conectados entre si e com os outros dispositivos físicos, incluindo a fonte de

alimentação, bem como as chaves e os leds.

b) Descrever a função obtida se, no circuito da fig. 6.b, forem usadas duas portas NAND no

lugar das portas AND.

A função NAND não é associativa, assim esse circuito deve ser avaliado por meio de uma

tabela da verdade, obtendo-se:

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

AB

Z

c) Como é possível obter uma função NAND de três entradas a partir de portas NAND de duas

entradas.

Como a função NAND não é associativa, é necessário negar a saída da porta NAND de

entrada, por meio de um inversor, antes de conectá-la à entrada da porta NAND de saída do

circuito. De fato, como duas negações se anulam, obtem-se: Z (A.B).C A.B.C

UFCG/DEE — Laboratório de Circuitos Lógicos – 06.2

7/7

d) A NEGAÇÃO é uma função lógica unária que é implementada por um dispositivo

denominado de INVERSOR, cujo bloco funcional é dado na fig. 4.a. Descrever o circuito

integrado usado no laboratório para implementar essa função (dar a tabela de

funcionamento).

O circuito integrado usado é o 7404 que implementa seis inversores: Y A . O diagrama de

pinos e a tabela de funcionamento são os seguintes:

A

Y

L

H

e) Uma outra função lógica unária é a IDENTIDADE, que é implementada por meio de um

dispositivo denominado de BUFFER, cujo bloco funcional é dado na fig. 4.b. Descrever um

circuito integrado que possa ser usado para implementar essa função (dar a tabela de

funcionamento).

Um circuito integrado que pode ser usado é o 7407 que implementa seis buffers, com saída

a coletor aberto: Y = A . O diagrama de pinos e a tabela de funcionamento são os seguintes:

A

Y

L

H

Existem outras opções equivalentes, como por exemplo: o 7417, com saída a coletor

aberto, e o 74125 ou o 74126, com saída triestado.

UFCG/DEE — Laboratório de Circuitos Lógicos – 06.2