Universidade Federal de Ouro Preto

ICEB – Instituto de Ciências Exatas e Biológicas

DECOM – Departamento de Computação

Relatório 2

Portas Lógicas Básicas

Aluno: Paulo A. Atanazio Jr

Setembro/2010

Ouro Preto - MG

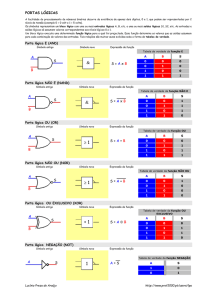

[1] Introdução

Portas lógicas ou circuitos lógicos, são dispositivos que operam um ou mais sinais lógicos de

entrada para produzir uma e somente uma saída, dependente da função implementada no circuito. São

geralmente usadas em circuitos eletrônicos, por causa das situações que os sinais deste tipo de circuito

podem apresentar: presença de sinal, ou "1"; e ausência de sinal, ou "0". As situações "Verdadeiro" ou

"Falso" são estudadas na Lógica Matemática ou Lógica de Boole; origem do nome destas portas. O

comportamento das portas lógicas é conhecido pela tabela verdade que apresenta os estados lógicos

das entradas e das saídas.

Em 1854, o matemático britânico George Boole (1815 - 1864), através da obra intitulada An

Investigation of the Laws of Thought (Uma Investigação Sobre as Leis do Pensamento), apresentou um

sistema matemático de análise lógica conhecido como álgebra de Boole.

No início da era da eletrônica, todos os problemas eram resolvidos por sistemas analógicos, isto

é, sistemas lineares. Apenas em 1938, o engenheiro americano Claude Elwood Shannon utilizou as

teorias da álgebra de Boole para a solução de problemas de circuitos de telefonia com relés, tendo

publicado um trabalho denominado Symbolic Analysis of Relay and Switching, praticamente

introduzindo na área tecnológica o campo da eletrônica digital. Esse ramo da eletrônica emprega em

seus sistemas um pequeno grupo de circuitos básicos padronizados conhecidos como Portas Lógicas.

A Lógica Transistor-Transistor (Transistor-Transistor Logic ou simplesmente TTL) é uma classe de

circuitos digitais construídos de transistores de junção bipolar (BJT), e resistores. Isso é chamada lógica

transistor-transistor porque ocorrem ambas as funções porta lógica e de amplificação pelos transistores

(em contraste com a RTL e a DTL). Isso é notável por ser uma família difundida de circuitos integrados

(CI) usada por muitas aplicações como computadores, controle industrial, eletrônica de consumo,

sintetizadores etc. Por causa do grande uso desta família lógica, sinais de entrada e saída de

equipamentos eletrônicos podem ser chamados entrada ou saída "TTL", significantemente compatível

com os níveis de tensão usados.

Estes circuitos têm como principal característica a utilização de sinais de 5 volts para níveis

lógicos altos. Seus circuitos integrados são constituídos basicamente de transistores, o que os torna

pouco sensíveis à eletricidade estática.

[2] Objetivos

- Familiarizar o aluno com o ambiente de simulação do freeware Qucs – Quite Universal Circuit

Simulator.

- Levantar e confirmar parâmetros e características elétricas essenciais usadas em projetos de

circuitos digitais.

[3] Desenvolvimento

3.1) Equipamentos Necessários

- Computador com o software Qucs instalado.

3.2) Simulando com o Qucs

Após a leitura do item “Começando com Simulações Digitais” do Índice de Ajuda disponível no

Menu Ajuda do Qucs, simulou-se o seguinte circuito:

Utilizando o recurso “Wire Label” do Qucs obteve-se o valor do potencial nos pontos chamados

de “VR1” e “VR2”, como pode-se observar na figura anterior.

Calculando-se o mesmo potencial VR2 por meio da relação V=r.i, o resultado encontrado foi

6.923076923 Ohms, a partir daí concluiu-se que a simulação está correta.

Após a substituição do resistor R2 por um capacitor de 10 nF e da fonte por um sinal de onda

quadrada, obteve-se o seguinte circuito:

Após simulação em regime transiente do circuito obtido verificou-se que a tensão no capacitor

se comporta de acordo com o gráfico a seguir:

Alterou-se no circuito anterior o resistor R3 de 300 Ohms por um R4 de 10 KOhms e obteve-se:

Devido o aumento no valor do resistor associado em série ao capacitor de 10 nF no circuito

simulado, percebeu-se um aumento no tempo necessário para carga do capacitor e significativa

alteração no gráfico que representa o seu comportamento ao longo do tempo. Tal fato coincide com o

que já era teoricamente esperado nessa situação.

3.3) Conceitos e Parâmetros de Famílias Lógicas

Consultando o TTL Databook obtivemos que a função lógica do CI é a inversora. A pinagem é a

apresentada abaixo:

A função lógica que o CI 7404 executa é a inversora, como se pode observar na tabela verdade a

seguir:

Entrada A Saída Y

1

0

0

1

O CI 7404 apresenta 6 portas lógicas inversora

A Família lógica TTL funciona com uma tensão de alimentação DC de 5V. As especificações de

uma família lógica são dadas pelas medidas mostradas na tabela abaixo:

O CI TTL 7404, especificamente, apresenta as seguintes características:

2V

0.8V

3.4V

0.2V

4.0mA

-1.6mA

-0.4mA

16mA

12ns

8ns

De acordo com as informações fornecidas pelo TTL Databook a margem de ruído do CI 7404

pode ser definida como:

Mrh = Voh - Vih (Margem de ruído para nível lógico 1) = 1.4V

Mrl = Vil – Vol (Margem de ruído para nível lógico 0) = 0.6V

3.4) Simulação Digital

Após as considerações e comparações a respeito de alguns parâmetros elétricos da família

lógica TTL, simulou-se o circuito abaixo utilizando o mesmo valor teórico do tempo de atraso de um CI

TTL 7404(12ns):

O tempo de atraso acumulado no circuito em questão pode ser verificado através do gráfico que

representa a presença de sinal nos “Wire Labels” ent e SAIDA.

De acordo com as informações apresentadas no gráfico, o tempo de atraso total ao se associar

em série vários inversores do tipo 7404 é equivalente a soma dos atrasos dos CI’s associados, nesse caso

60ns. Isso ocorre por que cada CI gasta cerca de 12ns para alterar o estado lógico de sua saída depois de

constatada alteração na entrada.

Feitas as análises e considerações necessárias a respeito do tempo de atraso de um CI do tipo

7404 e da propagação desse tempo ao se associar esse elemento em série, simulou-se o seguinte

circuito:

Ao se analisar graficamente o comportamento de circuito anterior, percebe-se novamente o

efeito do tempo de atraso na resposta do mesmo a alterações. Sabendo-se que cada porta tem um

tempo de atraso de 10ns e que a fonte digital emite pulsos com largura de 50ns, a forma de onda na

saída é determinada por:

3.5) Considerações e Análise dos Resultados

● É necessário conhecer a margem de ruído de uma determinada porta lógica para que não

haja alteração na funcionalidade da mesma, pois esta determina a tolerância que haverá sobre os

limites dos níveis lógicos.

● Os parâmetros relacionados ao acoplamento de portas lógicas (fan-in e fan-out) referem-se à

possibilidade de interligação de portas lógicas ou blocos lógicos entre si. Se estes fatores forem

excedidos na ligação da saída de um bloco às entradas de outros, os limites máximos de corrente serão

ultrapassados, acarretando principalmente a queda do nível 1 de saída. Que no caso do CI utilizado no

laboratório são:

TTL 7404

Parâmetros

Valores máximos

Unidade

IOL

16

mA

IIL

-1,6

mA

IOH

-0,4

mA

IIH

40

μA

Fan-in(NIVEL 0) = IOL / IIL = 16/-1,6 = -10

fan-out(NIVEL 1) = IOH / IIH= -0,4/40 = -0,01

● É necessário conhecer o tempo de atraso de propagação ao se projetar um circuito digital

para saber o tempo que o bloco leva para mudar de estado desde a aplicação de um nível lógico para

outro. Para a família TTL padrão, o tempo de atraso por porta é de ordem de 10ns.

● Deve se levar em conta a freqüência máxima de chaveamento de um circuito, que pode ser

facilmente calculada analisando os tempos de atraso Tplh(subida) e Tphl(descida).

[4] Conclusão

A partir das atividades realizadas no laboratório, da leitura e compreensão de material

relacionado ao assunto “Portas Lógicas Básicas” conclui-se que os parâmetros elétricos são

características essenciais que devem ser analisadas e levadas em conta ao se projetar um circuito digital

utilizando CI’s.