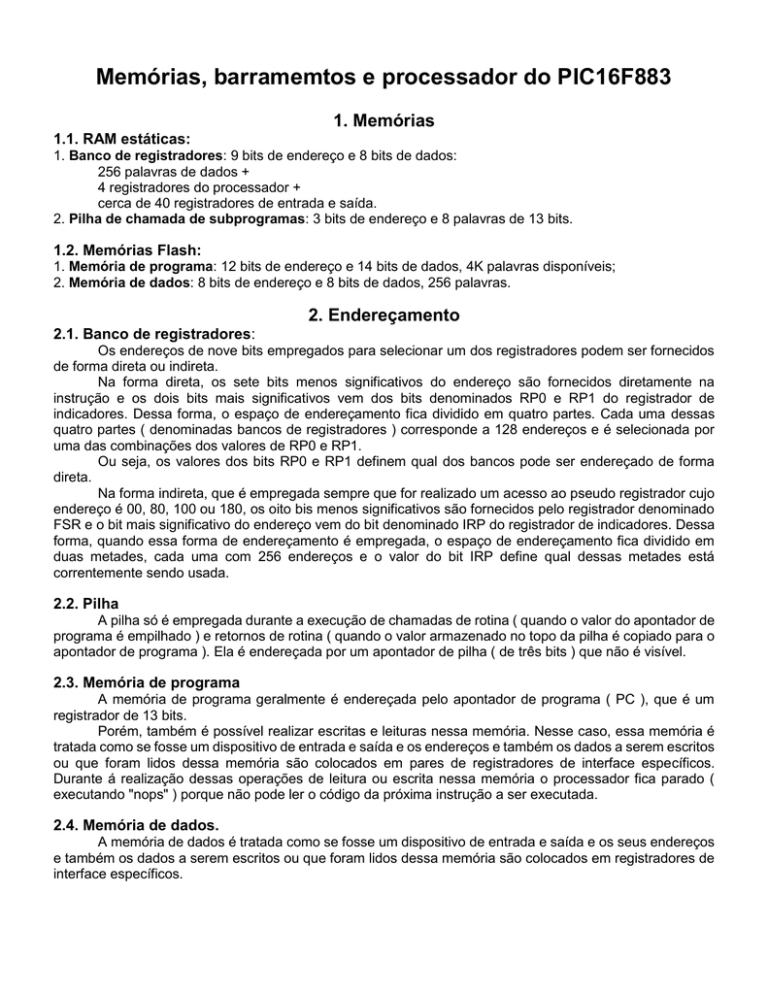

Memórias, barramemtos e processador do PIC16F883

1. Memórias

1.1. RAM estáticas:

1. Banco de registradores: 9 bits de endereço e 8 bits de dados:

256 palavras de dados +

4 registradores do processador +

cerca de 40 registradores de entrada e saída.

2. Pilha de chamada de subprogramas: 3 bits de endereço e 8 palavras de 13 bits.

1.2. Memórias Flash:

1. Memória de programa: 12 bits de endereço e 14 bits de dados, 4K palavras disponíveis;

2. Memória de dados: 8 bits de endereço e 8 bits de dados, 256 palavras.

2. Endereçamento

2.1. Banco de registradores:

Os endereços de nove bits empregados para selecionar um dos registradores podem ser fornecidos

de forma direta ou indireta.

Na forma direta, os sete bits menos significativos do endereço são fornecidos diretamente na

instrução e os dois bits mais significativos vem dos bits denominados RP0 e RP1 do registrador de

indicadores. Dessa forma, o espaço de endereçamento fica dividido em quatro partes. Cada uma dessas

quatro partes ( denominadas bancos de registradores ) corresponde a 128 endereços e é selecionada por

uma das combinações dos valores de RP0 e RP1.

Ou seja, os valores dos bits RP0 e RP1 definem qual dos bancos pode ser endereçado de forma

direta.

Na forma indireta, que é empregada sempre que for realizado um acesso ao pseudo registrador cujo

endereço é 00, 80, 100 ou 180, os oito bis menos significativos são fornecidos pelo registrador denominado

FSR e o bit mais significativo do endereço vem do bit denominado IRP do registrador de indicadores. Dessa

forma, quando essa forma de endereçamento é empregada, o espaço de endereçamento fica dividido em

duas metades, cada uma com 256 endereços e o valor do bit IRP define qual dessas metades está

correntemente sendo usada.

2.2. Pilha

A pilha só é empregada durante a execução de chamadas de rotina ( quando o valor do apontador de

programa é empilhado ) e retornos de rotina ( quando o valor armazenado no topo da pilha é copiado para o

apontador de programa ). Ela é endereçada por um apontador de pilha ( de três bits ) que não é visível.

2.3. Memória de programa

A memória de programa geralmente é endereçada pelo apontador de programa ( PC ), que é um

registrador de 13 bits.

Porém, também é possível realizar escritas e leituras nessa memória. Nesse caso, essa memória é

tratada como se fosse um dispositivo de entrada e saída e os endereços e também os dados a serem escritos

ou que foram lidos dessa memória são colocados em pares de registradores de interface específicos.

Durante á realização dessas operações de leitura ou escrita nessa memória o processador fica parado (

executando "nops" ) porque não pode ler o código da próxima instrução a ser executada.

2.4. Memória de dados.

A memória de dados é tratada como se fosse um dispositivo de entrada e saída e os seus endereços

e também os dados a serem escritos ou que foram lidos dessa memória são colocados em registradores de

interface específicos.

3. Processador

3.1. Registradores

Nome

Endereço

W

00 | 80 |

100 | 180

02 | 82 |

102 | 182

IND

PCL

STATUS

FSR

PCLATH

INTCON

03 | 83 |

103 | 183

Função

Registrador de trabalho ( acumulador )

Pseudo registrador usado para referenciar o registrador cujo endereço é igual ao

valor armazenado no registrador FSR

8 bits menos significativos do apontador de instrução

Registrador de Indicadores

Bit Nome Função

C

0

Vai um ou não pede emprestado

DC Vai um do quarto para o Quinto bit

1

Z

2

Zero

PD\ É zerado pela instrução "SLEEP"

3

TO\ É zerado quando ocorre um reset causado pelo Watch dog

4

RP0

5

Bits mais significativos do endereço usado em endereçamento direto

RP1

6

IRP Bit mais significativo do endereço usado em endereçamento indireto.

7

04 | 84 |

Informa o endereço do registrador referenciado indiretamente

104 | 184

0A | 8A |

Valor a ser atribuído aos bits mais significativos do apontador de instrução

10A | 18A

Registrador de controle das interrupções

Bit Nome Função

0 RBIF Interrupção de alteração do registrador B pendente

1 INTF Interrupção externa ( RB0 ) pendente

T0IF Interrupção do “Timer0” pendente

2

0B | 8B |

10B | 18B 3 RBIE Interrupção de alteração do registrador B habilitada

4 INTE Interrupção externa ( RB0 ) habilitada

T0IE Interrupção do “Timer0” habilitada

5

6 PEIE Interrupção das demais interfaces habilitada

GIE Interruções habilitadas

7

3.2. Ciclo de execução das instruções:

Cada instrução normalmente é executada em quatro ciclos de relógio. Durante a execução de cada

instrução é realizada simultaneamente a busca do código da próxima instrução a ser executada.

Por causa dessa simultaneidade, sempre que o apontador de programa é modificado durante a

execução de uma instrução, a instrução empregará dois ciclos de instrução ( oito ciclos de relógio ) para ser

executada. Isso é necessário porque o código de instrução buscado durante a execução da instrução foi

aquele que está armazenado na posição da memória de programa cujo endereço corresponde ao valor que o

apontador de programa tinha antes de ser modificado pela instrução.

Durante o ciclo de instrução adicional, o processador executa um "nop" e busca o código da instrução

armazenada na posição de memória endereçada pelo novo valor do apontador de instrução.

Essa duplicação do tempo da execução ocorre tanto durante a execução de instruções de desvio

incondicional como durante a execução de intruções de desvio condicional com a condição atendida e

também durante a execução de instruções que alterem o valor armazenado no registrador PCL.

Sempre que o valor do registrador PCL for alterado por uma instrução o apontador de programa

receberá um valor formado pela concatenação dos cinco bits menos significativos do valor armazenado no

registrador PCLATH com os oito bits que foram enviados para o registrador PCL.

3.3. Os formatos das instruções

As palavras de instrução são formadas por 14 bits que contém o código da instrução e valores literais

que desempenham o papel de operandos imediatos. São empregados cinco formatos de instrução:

Nome do

formato

Número de

instruções

Controle

Byte oriented

5

16 ( 31 )

Bit oriented

4

0

1

Desvios

2

1

0

Com literal

7

1

1

13

12

00

11

10

9

Número do bit

8

7

6

5

00.0000.0

Código de operação Dst

Código de

Número do bit

operação

Cod

Op.

Código de operação

4

3

2

1

0

Código de operação

Endereço

Endereço

Alvo do desvio

Constante

São empregados os seguintes valores literais:

Nome do

valor literal

Tamanho

Posição

( bits )

Dst

1

Bit 7

Endereço

7

Bits 0 a 6

Número do bit

3

Bits 7 a 9

Alvo do desvio

11

Bits 0 a 10

Constante

8

Bits 0 a 7

Função

Se for zero, indica que o valor produzido deve ser armazenado no

registrador W, se for um, indica que esse valor deve ser armazenado

em um registrador do banco de registradores

Fornece os sete bits menos significativos do valor empregado para

selecionar qual dos registradores deve ser empregado

Indica qual é o bit que deve ser alterado ou testado

Fornece os onze bits menos significativos do valor a ser colocado no

apontador de instrução para realizar um desvio

Fornece uma constante que será diretamente empregada como

operando pela instrução

3.4. Instruções em ordem de código de operação

Mnemônico e

Ciclos

operandos

Código

Tipo

Descrição

00.0000.0XX0.0000

00.0000.0000.1000

00.0000.0000.1001

00.0000.0110.0011

00.0000.0110.0100

C.1

D.1

D.2

C.2

C.3

NOP

RETURN

RETFIE

SLEEP

CLRWDT

1

2

2

1

1

Nenhuma operação

Retorno de subrotina

Retorno de interrupção ( GIE recebe 1 )

Entra no modo "stand by"

Zera o tempo do "watch dog"

00.0000.1FFF.FFFF

00.0001.0XXX.XXXX

00.0001.1FFF.FFFF

M.1

M.2

M.3

MOVWF F

CLRW

CLRF F

1

1

1

00.0010.DFFF.FFFF

A.1

SUBWF F,D

1

00.0011.DFFF.FFFF

00.0100.DFFF.FFFF

00.0101.DFFF.FFFF

00.0110.DFFF.FFFF

00.0111.DFFF.FFFF

00.1000.DFFF.FFFF

00.1001.DFFF.FFFF

00.1010.DFFF.FFFF

A.2

A.3

A.4

A.5

A.6

M.4

A.7

A.8

DECF F,D

IORWF F,D

ANDWF F,D

XORWF F,D

ADDWF F,D

MOVF F,D

COMF F,D

INCF F,D

1

1

1

1

1

1

1

1

00.1011.DFFF.FFFF

D.3

DECFSZ F,D

1|2

00.1100.DFFF.FFFF

00.1101.DFFF.FFFF

00.1110.DFFF.FFFF

A.9

A.10

A.11

RRF F,D

RLF F,D

SWAPF F,D

1

1

1

00.1111.DFFF.FFFF

D.4

INCFSZ F,D

1|2

Move o W para um registrador

Zera o W

Zera um registrador

Soma o complemento a dois de W a um

registrador

Decrementa um registrador

Ou de W com um registrador

E de W com um registrador

Ou exclusivo de W com um registrador

Soma W a um registrador

Move um registrador

Complementa um registrador

Incrementa um registrador

Decrementa um registrador e se o

resultado for zero, pula a próxima

instrução

Rola um registrador para a direita

Rola um registrador para a esquerda

Troca os Quartetos de um registrador

Incrementa um registrador e se o

resultado for zero, pula a próxima

instrução

01.00BB.BFFF.FFFF

01.01BB.BFFF.FFFF

A.12

A.13

BCF F,B

BSF F,B

1

1

01.10BB.BFFF.FFFF

D.5

BTFSC F,B

1|2

01.11BB.BFFF.FFFF

D.6

BTFSS F,B

1|2

10.0KKK.KKKK.KKKK

10.1KKK.KKKK.KKKK

D.7

D.8

CALL K

GOTO K

2

2

Chama um subprograma

Desvia para o alvo especificado

11.00XX.KKKK.KKKK

M.5

MOVLW K

1

11.01XX.KKKK.KKKK

D.9

RETLW K

2

11.1000.KKKK.KKKK

11.1001.KKKK.KKKK

11.1010.KKKK.KKKK

A.14

A.15

A.16

IORLW K

ANDLW K

XORLW K

1

1

1

11.110X.KKKK.KKKK

A.17

SUBLW K

1

11.111X.KKKK.KKKK

A.18

ADDLW K

1

Move uma constante para o W

Move uma constante para W e retorna

do subprograma

Ou de uma constante com W

E de uma constante com W

Ou exclusivo de uma constante com W

Soma uma constante ao complemento a

dois de W

Soma uma constante a W

Indicadores

alterados

GIE

TO\, PD\

TO\, PD\

Z

Z

C, DC, Z

Z

Z

Z

Z

C, DC, Z

Z

Z

Z

C

C

Zera um bit de um registrador

Coloca um em um bit de um registrador

Se o bit especificado for zero, pula a

próxima instrução

Se o bit especificado for um, pula a

próxima instrução

Z

Z

Z

C, DC, Z

C, DC, Z

Código

00.0001.1FFF.FF

FF

00.0001.0XXX.XX

XX

00.1000.DFFF.FF

FF

11.00XX.KKKK.KK

KK

00.0000.1FFF.FF

FF

Aritméticas

Rot

3. Aritméticas e Lógicas com

op. imediato

Lógicas

2. Aritméticas e Lógicas sem op. imediato

Bits

Grupo

1.

Movimentação de dados

3.5 Tabela de instruções em ordem de tipo e mnemônico

01.00BB.BFFF.FF

FF

01.01BB.BFFF.FF

FF

00.1110.DFFF.FF

FF

00.0111.DFFF.FF

FF

00.0011.DFFF.FF

FF

00.1010.DFFF.FF

FF

00.0010.DFFF.FF

FF

00.1101.DFFF.FF

FF

00.1100.DFFF.FF

FF

00.0101.DFFF.FF

FF

00.1001.DFFF.FF

FF

00.0100.DFFF.FF

FF

00.0110.DFFF.FF

FF

11.111X.KKKK.KK

KK

11.110X.KKKK.KK

KK

11.1001.KKKK.KK

KK

11.1000.KKKK.KK

KK

11.1010.KKKK.KK

KK

Tipo

Mnemônico e

Ciclos

operandos

Descrição

Indicadores

alterados

M.3

CLRF F

1

Zera um registrador

Z

M.2

CLRW

1

Zera o W

Z

M.4

MOVF F,D

1

Move um registrador

Z

M.5

MOVLW K

1

Move uma constante para o W

M.1

MOVWF F

1

Move o W para um registrador

A.12

BCF F,B

1

Zera um bit de um registrador

A.13

BSF F,B

1

Coloca um em um bit de um registrador

A.11

SWAPF F,D

1

Troca os Quartetos de um registrador

A.6

ADDWF F,D

1

Soma W a um registrador

A.2

DECF F,D

1

Decrementa um registrador

Z

A.8

INCF F,D

1

Incrementa um registrador

Z

A.1

SUBWF F,D

1

Soma o complemento a dois de W a um

registrador

A.10

RLF F,D

1

Rola um registrador para a esquerda

C

A.9

RRF F,D

1

Rola um registrador para a direita

C

A.4

ANDWF F,D

1

E de W com um registrador

Z

A.7

COMF F,D

1

Complementa um registrador

Z

A.3

IORWF F,D

1

Ou de W com um registrador

Z

A.5

XORWF F,D

1

Ou exclusivo de W com um registrador

Z

A.18

ADDLW K

1

Soma uma constante a W

C, DC, Z

A.17

SUBLW K

1

Soma uma constante ao complemento a

dois de W

C, DC, Z

A.15

ANDLW K

1

E de uma constante com W

Z

A.14

IORLW K

1

Ou de uma constante com W

Z

A.16

XORLW K

1

Ou exclusivo de uma constante com W

Z

C, DC, Z

C, DC, Z

4. Desvios incondicionais

10.0KKK.KKKK.KK

KK

10.1KKK.KKKK.KK

KK

00.0000.0000.10

01

11.01XX.KKKK.KK

KK

00.0000.0000.10

00

5. Desvios condicionais

01.10BB.BFFF.FF

FF

01.11BB.BFFF.FF

FF

00.1011.DFFF.FF

FF

00.1111.DFFF.FF

FF

6. Controle

00.0000.0110.01

00

00.0000.0XX0.00

00

00.0000.0110.00

11

D.7

CALL K

2

Chama um subprograma

D.8

GOTO K

2

Desvia para o alvo especificado

D.2

RETFIE

2

Retorno de interrupção ( GIE recebe 1 )

D.9

RETLW K

2

Move uma constante para W e retorna do

subprograma

D.1

RETURN

2

Retorno de subrotina

D.5

BTFSC F,B

1|2

D.6

BTFSS F,B

1|2

D.3

DECFSZ F,D

1|2

D.4

INCFSZ F,D

1|2

C.3

CLRWDT

1

Zera o tempo do "watch dog"

C.1

NOP

1

Nenhuma operação

C.2

SLEEP

1

Entra no modo "stand by"

GIE

Se o bit especificado for zero, pula a

próxima instrução

Se o bit especificado for um, pula a próxima

instrução

Decrementa um registrador e se o resultado

for zero, pula a próxima instrução

Incrementa um registrador e se o resultado

for zero, pula a próxima instrução

TO\, PD\

TO\, PD\