Concepção de Circuitos e Sistemas Integrados

João Paulo Cunha

Bolsa Voluntária/PIBIC

Prof. André Augusto Mariano, Ph.D. / Bernardo R. B. A. Leite, Ph.D.

Introdução e objetivos: RFID é um método

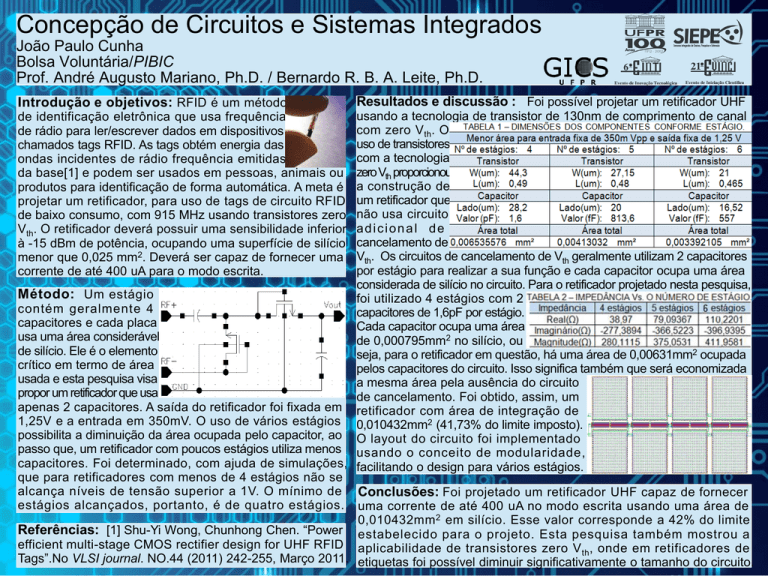

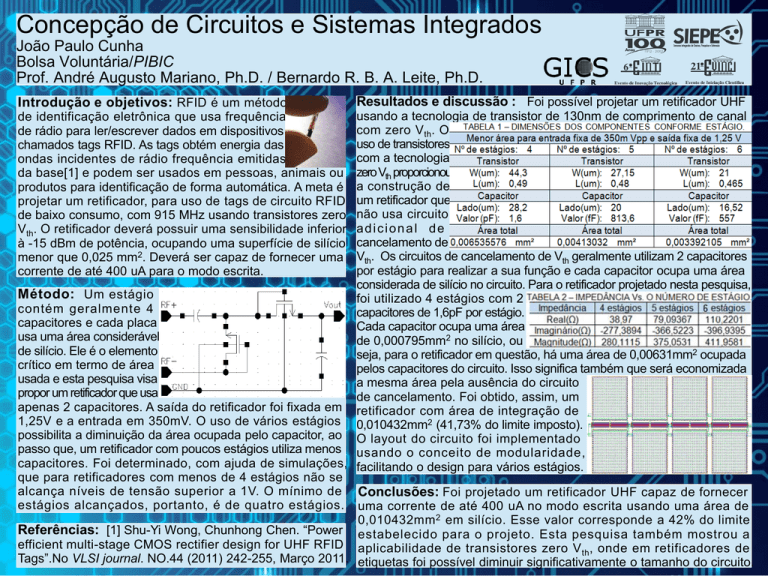

Resultados e discussão : Foi possível projetar um retificador UHF

usando a tecnologia de transistor de 130nm de comprimento de canal

com zero Vth. O

uso de transistores

com a tecnologia

zero Vth proporcionou

a construção de

um retificador que

não usa circuito

adicional de

cancelamento de

Vth. Os circuitos de cancelamento de Vth geralmente utilizam 2 capacitores

por estágio para realizar a sua função e cada capacitor ocupa uma área

considerada de silício no circuito. Para o retificador projetado nesta pesquisa,

Método: Um estágio

foi utilizado 4 estágios com 2

contém geralmente 4

capacitores de 1,6pF por estágio.

capacitores e cada placa

Cada capacitor ocupa uma área

usa uma área considerável

de 0,000795mm2 no silício, ou

de silício. Ele é o elemento

seja, para o retificador em questão, há uma área de 0,00631mm2 ocupada

crítico em termo de área

pelos capacitores do circuito. Isso significa também que será economizada

usada e esta pesquisa visa

a mesma área pela ausência do circuito

propor um retificador que usa

de cancelamento. Foi obtido, assim, um

apenas 2 capacitores. A saída do retificador foi fixada em retificador com área de integração de

1,25V e a entrada em 350mV. O uso de vários estágios 0,010432mm2 (41,73% do limite imposto).

possibilita a diminuição da área ocupada pelo capacitor, ao O layout do circuito foi implementado

passo que, um retificador com poucos estágios utiliza menos usando o conceito de modularidade,

capacitores. Foi determinado, com ajuda de simulações, facilitando o design para vários estágios.

que para retificadores com menos de 4 estágios não se

alcança níveis de tensão superior a 1V. O mínimo de Conclusões: Foi projetado um retificador UHF capaz de fornecer

estágios alcançados, portanto, é de quatro estágios. uma corrente de até 400 uA no modo escrita usando uma área de

0,010432mm 2 em silício. Esse valor corresponde a 42% do limite

Referências: [1] Shu-Yi Wong, Chunhong Chen. “Power estabelecido para o projeto. Esta pesquisa também mostrou a

efficient multi-stage CMOS rectifier design for UHF RFID aplicabilidade de transistores zero V , onde em retificadores de

th

Tags”.No VLSI journal. NO.44 (2011) 242-255, Março 2011. etiquetas foi possível diminuir significativamente o tamanho do circuito.

de identificação eletrônica que usa frequência

de rádio para ler/escrever dados em dispositivos

chamados tags RFID. As tags obtém energia das

ondas incidentes de rádio frequência emitidas

da base[1] e podem ser usados em pessoas, animais ou

produtos para identificação de forma automática. A meta é

projetar um retificador, para uso de tags de circuito RFID

de baixo consumo, com 915 MHz usando transistores zero

Vth. O retificador deverá possuir uma sensibilidade inferior

à -15 dBm de potência, ocupando uma superfície de silício

menor que 0,025 mm2. Deverá ser capaz de fornecer uma

corrente de até 400 uA para o modo escrita.