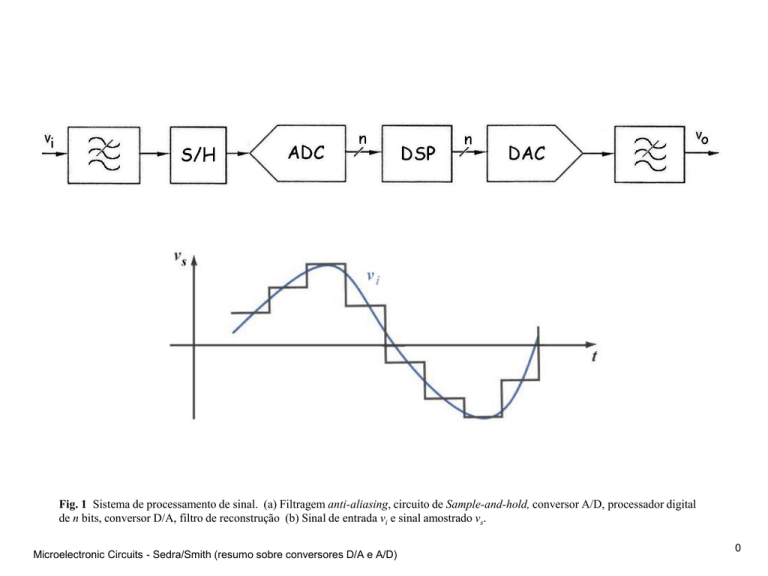

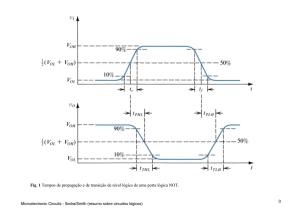

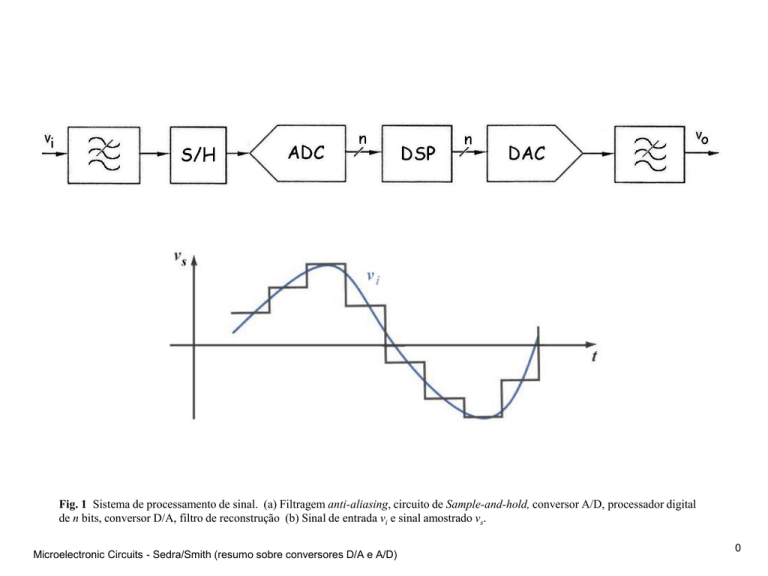

Fig. 1 Sistema de processamento de sinal. (a) Filtragem anti-aliasing, circuito de Sample-and-hold, conversor A/D, processador digital

de n bits, conversor D/A, filtro de reconstrução (b) Sinal de entrada vi e sinal amostrado vs.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

0

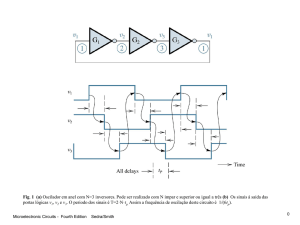

Fig. 2 Processo de amostragem de um sinal fs=1/T. (a) Circuito de Sample-and-hold (S/H). O interruptor está fechado enquanto vs

está activo (durante a fase ) (b) Sinal de entrada (genérico) (c) fase de amostragem (controla o interruptor). (d) O sinal de saída será

a entrada de um bloco seguinte de conversão A/D.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

1

Fig. 3 Conversor D/A de N-bits usando um agregado binário de resistências.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

2

Fig. 4 Conversor D/A com base numa malha resistiva R-2R.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

3

Fig. 5 Conversor D/A flash ou paralelo.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

4

Fig. 6 Conversor A/D flash ou paralelo.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

5

Fig. 7 Conversor A/D por aproximações sucessivas (SAR). O comparador comanda a subida e descida do contador até que o resultado

à saída do conversor D/A, vo seja aproximadamente igual ao valor da tensão de entrada vA.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

6

Fig. 8 Conversor A/D de dupla rampa (a tensão de entrada vA é negativa).

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

7

Fig. 9 Conversor multi-passo ou pipeline. Este exemplo apresenta uma arquitectura de 2 bits por andar. Cada andar inclui um

conversor D/A e A/D flash de 2 bits e um módulo de soma e ganho. O erro de cada andar é transmitido ao andar seguinte já escalado

pelo que todos os andares são iguais. O bloco de registos sincroniza os bits na saída. Este conversor tem um tempo de arranque/latência

longo n*T (para aquisição da 1ª amostra), mas a partir dai fornece uma amostra por período.

Microelectronic Circuits - Sedra/Smith (resumo sobre conversores D/A e A/D)

8