EA869

Interrupção

Faculdade de Engenharia Elétrica e de Computação (FEEC)

Universidade Estadual de Campinas (UNICAMP)

Prof. Levy Boccato

1

Objetivos

Definir o conceito de interrupção.

Diferenciar interrupções de subrotinas.

Conhecer as diversas estratégias para implementar

interrupções.

Aprender a instalar interrupções na memória.

2

Recordando

No tópico anterior, vimos como desviar a execução de um programa

através de chamadas de subrotinas.

Utilidades: (1) eliminar redundâncias, (2) reutilização de código para

diferentes entradas de dados, (3) decompor problemas grandes em

pequenas partes (modularização), entre outras.

Entretanto, nem sempre a mudança do fluxo normal de execução de

um programa acontece de forma programada, como ocorre no caso

de subrotinas.

Quais condições podem

acarretar a interrupção da

execução de um programa?

Atendimento de eventos externos e internos

Mouse, teclado, sensores, telas touchscreen, ou sinais internos (reset) podem

interromper a execução da CPU para o atendimento dos seus eventos.

3

Exemplo

Vamos supor que você esteja jogando 2048 no seu smartphone

e

alguém resolve ligar para você.

MEM

CPU

PROG

Controlador

GSI

RSI

Gerador de Sequência de interrupção: é o hardware dentro do controlador

que irá receber o sinal de interrupção, interromper a execução do programa

e desviar para a ROTINA DE SERVIÇO DE INTERRUPÇÃO (RSI), a qual é

responsável por atender e tratar o evento que gerou a interrupção.

4

Interrupção

Definição:

INTERRUPÇÃO

É a quebra da sequência normal de operação de forma a atender

eventos especiais, tais como:

Entrada de dados vindos de periféricos.

Atendimento de sinal de sensor.

Sinais internos.

Como o processador

descobre que um

evento quer

interrompê-lo?

Através de um sinal de interrupção

enviado ao GSI por linhas de

interrupção

Cada linha de interrupção está

associada a um dispositivo (ou

a um conjunto deles) que envia

o sinal de interrupção quando

deseja ser atendido.

5

Interrupção

Vejamos agora o atendimento de uma interrupção:

O que vai

acontecer?

MOV R0, #100

MOV R1, (R0)+

MOV R2, (R0)+

ADD R3, R1, R2

MOV (R0), R3

MOV R0, #200

MOV R1, (R0)+

MOV R2, (R0)+

ADD R3, R1, R2

MOV (R0), R3

MOV R0, #300

BUSCA

SINAL DE

INTERRUPÇÃO

EXECUÇÃO

RSI:

MOV

(R0)+

Para

queR1,

tudo

isto

MOV R2,

(R0)+

ocorra,

quais

ADD R3, R1, R2o

microoperações

MOV (R0), R3

GSI deve realizar?

RTI

Ao aparecer um sinal de interrupção:

1. Controlador termina de executar a instrução corrente.

2. GSI salva o estado atual da máquina e o endereço de

retorno, desviando, então, a execução do programa para

a rotina de serviço de interrupção (RSI).

3. Ao terminar de executar a RSI, o controlador restaura

o estado anterior à interrupção e volta a executar o

programa principal.

6

Interrupção

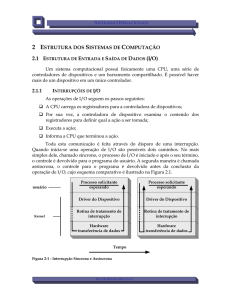

Gerador de sinais de interrupção (GSI):

É um dispositivo do controlador que, ao receber um sinal de

interrupção, salva o estado atual do processador (Registrador de

Estado ou PSW), assim como o endereço de retorno, e desvia a

execução do programa para a rotina de serviço de interrupção

(RSI).

Arquitetura:

sinais de controle

sinal de

interrupção

...

C.O. sinais de controle

BUSCA

D

...

EXECUÇÃO

sinal do fim da

sequência de microcomandos

Q

PARTIDA

CLR

Q

Flip-Flop

de

Interrupção

GERADOR DE SEQUÊNCIA

DE INTERRUPÇÃO

sinais de controle

sinal do fim

da sequência

de microcomandos

...

7

Interrupção

Atendimento de uma interrupção:

Armazenar o conteúdo do PC para posterior retorno ao programa

interrompido (endereço de retorno).

Armazenar o estado corrente do processador para restaurar, após

o retorno, a situação (o cenário) existente no momento da

interrupção.

Desviar o controle de execução para a rotina de serviço de

interrupção (RSI).

Onde iremos

armazenas essas

informações?

PILHA!

SINAIS DE CONTROLE DO GSI

PUSH PC

PUSH PSW

JUMP RSI

Pilha ← (PC) Endereço de retorno

Pilha ← (PSW) Estado corrente do processador

PC ← Endereço da RSI Desvia a execução para RSI

8

Interrupção

Retorno de uma interrupção:

À semelhança do retorno de subrotina, temos uma instrução

especial ao final da RSI.

RS1: MOV R1, (R0)+

MOV R2, (R0)+

ADD R3, R1, R2

MOV (R0), R3

RTI

Quais operações a instrução

RTI deve executar?

POP PSW

POP PC

PSW ← Estado anterior à Interrupção

PC ← Endereço de retorno

Note que o retorno deve ser programado na RSI.

Ele não é automaticamente executado pelo GSI.

9

Rotinas de Serviço de Interrupção

Qual é o endereço da Rotina de

Serviço de Interrupção?

Antes de executar os sinais de controle para o atendimento de uma

interrupção, o GSI deve conhecer o endereço da RSI.

Existem 3 formas de informar qual é este endereço.

Mapeamento Interno à CPU

Neste caso, cada linha de interrupção está associada a um endereço de

memória.

O programador deve instalar a RSI no endereço de interrupção associado

ao pino de interrupção no qual foi conectado o dispositivo.

CPU

RS1

L1

L2

MEM

Mapeamento

RS2

10

Rotinas de Serviço de Interrupção

Qual é o endereço da Rotina de

Serviço de Interrupção?

Antes de executar os sinais de controle para o atendimento de uma

interrupção, o GSI deve conhecer o endereço da RSI.

Existem 3 formas de informar qual é este endereço.

Mapeamento Externo à CPU

Neste caso, temos um hardware chamado “Controlador

que informa ao GSI qual é o endereço da interrupção.

Antes de executar o JUMP para a RSI, a CPU precisa

enviado pelo controlador.

CPU

MEM

L1

Controlador

de

end

GSI

Interrupçõe

L2

s

de Interrupções”

ler este endereço

PUSH PC

PUSH PSW

IN CONTRL

JUMP RSI

11

Rotinas de Serviço de Interrupção

Qual é o endereço da Rotina de

Serviço de Interrupção?

Antes de executar os sinais de controle para o atendimento de uma

interrupção, o GSI deve conhecer o endereço da RSI.

Existem 3 formas de informar qual é este endereço.

Polling

Neste caso, temos uma Rotina de Serviço que lê o status de todos os

dispositivos conectados à linha de interrupção.

Caso algum dispositivo tenha emitido um sinal de interrupção, acontece o

desvio para RSI correspondente.

RS: IN STATUS2

Jcond RS1

CPU

MEM

IN STATUS2

Jcond RS1

LI

GSI

...

IN STATUSn

12

Jcond RSn

Resumindo

Definição: uma interrupção nada mais é do que a quebra da

sequência de operação para o atendimento de um evento interno ou

externo.

Atendimento: desvio a execução da CPU para uma Rotina de

Serviço de Interrupção. Uma vez finalizada, as condições anteriores

do processador são restauradas.

Hardware: uma área dentro do controlador, o Gerador de Sinais de

Interrupção (GSI), é responsável por atender a interrupção. O

retorno é executado por uma instrução (RTI) ao final da RSI.

Endereço: o sinal de interrupção é enviado pelo dispositivo através

de uma linha de interrupção. Cada linha de interrupção tem

associada a si um endereço da memória.

Onde se encontram as

Rotinas de Serviço de

Interrupção?

Possibilidade 1:

Nos endereços associados às

linhas de interrupção

L1 → RS1

L2 → RS2

...

L3 → RS3

13

Endereços de Interrupção

(1) Em posições não-contíguas de memória

MEMÓRIA

L1

END1

RS1

“mouse”

L2

Nesta forma de

organização,

cada endereço

associado à

linha de

interrupção

possui um

conjunto de

palavras para

instalação das

RSIs.

RS2

END2

Existe

uma

solução

mais

“teclado” – P1

elegante para instalar as RSIs?

Ln

SINAIS DO GSI

PUSH PC

PUSH PSW

JUMP ENDi

PC ← ENDi

RS1

“mouse”

RS2

RS2

...

“teclado”

“teclado”

VETORES DE

INTERRUPÇÃO!

JUMP

ENDX

ENDn

ENDX

RS2

“teclado” – P2

Invadiu a área reservada para a

RSI

de

outra

linha

de

interrupção!

Desviar a execução para uma área livre

da memória

Solução?

14

Endereços de Interrupção

(2) Em vetores (interrupção vetorizada)

L1

END1

L2

END2

MEMÓRIA

RS1

RS2

...

Ln

Nesta forma de organização,

os endereços associados a

cada linha de interrupção

estão em posições contíguas

da memória...

ENDn

Isto implica não

haver espaço para

a instalação da

RSI...

VETOR DE

INTERRUPÇÕES

RS3

Desta forma, os

endereços de

interrupção

conterão apenas os

endereços das RSI

apropriadas.

SINAIS DO GSI

PUSH PC

PUSH PSW

JUMP (ENDi)

PC ← (ENDi) = RSIi

Processadores mais modernos (por exemplo, ARM) possuem uma área da memória

reservada para os endereços das RSIs. Essa área é chamada de “Vetor de Interrupções” e

geralmente localiza-se no início do espaço de memória, a partir do endereço 0.

A vantagem desta estratégia é que as RSIs podem ser instaladas em qualquer área livre

da memória sem restrição de tamanho.

15

Endereços de Interrupção

•

•

Em algumas circunstâncias, para que a Rotina de Serviço de Interrupção seja

executada corretamente, podem ser necessárias algumas condições especiais.

Por exemplo, considere o evento “reiniciar”:

Ao pressionar o botão “reiniciar”, o programa corrente é interrompido e a

execução é desviada para uma RSI que inicializa o Sistema Operacional.

Durante esta inicialização, nenhum sinal de interrupção pode interromper a RSI.

Para que nenhuma interrupção aconteça, precisamos desabilitá-las no

Registrador de Estado (PSW);

Uma forma de implementação é associar bits do PSW às linhas de interrupção.

Se bit = 1, a linha correspondente ao bit pode interromper a execução. Se bit = 0,

não pode interromper.

REGISTRADOR DE ESTADO (PSW)

Se, antes de executar a RSI eu

coloco 001 no PSW, quem

poderá interrompê-la?

Apenas a Linha 1!

L3

L2

L1

0

0

1

O valor colocado no registrador PSW é

chamado de máscara de interrupção.

Muitas vezes, é necessário passar uma máscara

para o Registrador de Estado antes de iniciar a

execução da RSI.

16

Como faremos isso?

Endereços de Interrupção

(3) Em vetores (interrupção vetorizada) com PSW (estado)

L1

L2

END1

MEMÓRIA

mask1

RS1

END2

mask2

Qual a diferença

RS2entre a

Interrupção

e Subrotina?

...

Li

Uma forma de alterar o

estado do processador,

adequando-o

para

a

execução da RSI, é

enviando-lhe

uma

máscara de interrupção.

ENDi

VETOR DE

INTERRUPÇÕES

(com PSW)

maski

RSi

Esta máscara pode ser

alocada no Vetor de

Interrupções, em uma

posição

antes

do

endereço da RSI.

Qual outra forma de enviar a

máscara para o PSW?

SINAIS DO GSI

PUSH PC

PUSH PSW

MOV ENDi, PSW

JUMP (ENDi + 1)

Através da primeira

linha da RSI:

PSW ← (ENDi) = pswi

PC ← (ENDi + 1) = RSIi

RS1: MOVE mask1, PSW

...

RTI

17

Interrupções versus Subrotinas

ATENDIMENTO

ENDEREÇO DA

ROTINA DE SERVIÇO

DESVIO DA

EXECUÇÃO

QUEM EXECUTA O

DESVIO PARA RS

SUBROTINAS

INTERRUPÇÃO

Síncrono

(programa)

Assíncrono

(sinal externo)

Própria Instrução

Salva PC

Controlador ao

executar CALL

RETORNO AO

PROGRAMA

Restaura PC

QUEM EXECUTA

O RETORNO

Controlador ao

executar RTS

Vetor de

Interrupções

Salva PC e PSW

GSI

Restaura PC e PSW

Controlador ao

executar RTI

18

Instalando RSIs

•

•

Agora que sabemos os mecanismos de funcionamento da interrupção e onde se

localizam os endereços e as rotinas de serviço, vamos analisar como se escreve um

programa Assembly para implementar interrupções.

Exemplo:

Considere uma arquitetura na qual as linhas de interrupção L1, L2 e L3 estão associadas a

um Vetor de Interrupções de endereços contíguos e sem PSW. O Vetor de Interrupções

começa na posição 0 de memória e as RSIs estão, respectivamente, nas posições 300, 400 e

500. Escreva um programa que implemente estas condições.

L1

END1

RS1

0

300

L2

END2

RS2

1

400

L3

END3

RS3

2

500

Antes de continuar, vamos falar mais um

pouco sobre pseudo-instruções...

19

Instalando RSIs

Pseudo-instruções

É um tipo especial de instrução não executável, que

insere valores em posições de memória, reserva espaço e

organiza na memória o local de instalação das instruções.

Quem lê e “executa” as pseudo-instruções é o montador

ao alocar o programa Assembly na memória.

Em resumo, pseudo-instruções são regras que ajudam o

montador a definir o conteúdo de cada posição da memória

ao instalar um programa.

DS X

Reserva X palavras da memória a partir

da posição da pseudo-instrução.

DW V Posição de memória desta pseudoinstrução recebe o valor V.

ORG Y A próxima instrução é alocada na posição

Y de memória.

ADR rótulo Posição recebe o endereço de “rótulo”.

20

Instalando RSIs

•

•

Agora que sabemos os mecanismos de funcionamento da interrupção e onde se

localizam os endereços e as rotinas de serviço, vamos analisar como se escreve um

programa Assembly para implementar interrupções.

Exemplo:

Considere uma arquitetura na qual as linhas de interrupção L1, L2 e L3 estão associadas a

um Vetor de Interrupções de endereços contíguos e sem PSW. O Vetor de Interrupções

começa na posição 0 de memória e as RSIs estão, respectivamente, nas posições 300, 400 e

500. Escreva um programa que implemente estas condições.

L1

END1

RS1

0

300

L2

END2

RS2

1

400

L3

END3

RS3

2

500

Definindo o vetor de interrupções:

ORG 0

ADR RS1 ou DW 300

ADR RS2 ou DW 400

ADR RS3 ou DW 500

ORG 300

Instalando as RSIs: RS1: ...

RTI

ORG 400

RS2: ...

RTI

ORG 500

RS3: ...

RTI

21

Instalando RSIs

Considere agora uma arquitetura na qual as linhas L1, L2 e L3 estão

associadas a um vetor de interrupções de endereços contíguos e

com PSW.

O vetor de interrupções começa na posição 0 da memória e as RSIs

estão, respectivamente, nas posições 150, 350 e 400.

Cada linha pode ser interrompida pelas outras, exceto por si mesma.

Os 3 bits menos significativos do PSW habilitam e desabilitam as

interrupções nas linhas.

Vamos, então, escrever um programa Assembly que implemente esta

situação, lembrando que os sinais de controle gerados pelo GSI

correspondem às operações:

PUSH PC

PUSH PSW

MOV ENDi, PSW

JUMP (ENDi + 1)

22

Instalando RSIs

Solução:

Definindo as

máscaras:

psw1: 1102

psw2: 1012

L3

L2

L1

PSW

psw3: 0112

Instalando o vetor de interrupções:

ORG 0

DW 110

ADR RS1 ou DW 150

DW 101

ADR RS2 ou DW 350

DW 011

ADR RS3 ou DW 400

Instalando as RSIs:

ORG 150

RS1: ...

...

RTI

ORG 350

RS2: ...

...

RTI

ORG 400

RS3: ...

RTI

23

Créditos

Este material está baseado nas notas de aula elaboradas pelo

Prof. Léo Pini e pelo aluno de doutorado Tiago Novaes.

24