Curso de Eletrônica

Parte Analógica

Ademarlaudo Barbosa

III – Dispositivos semicondutores

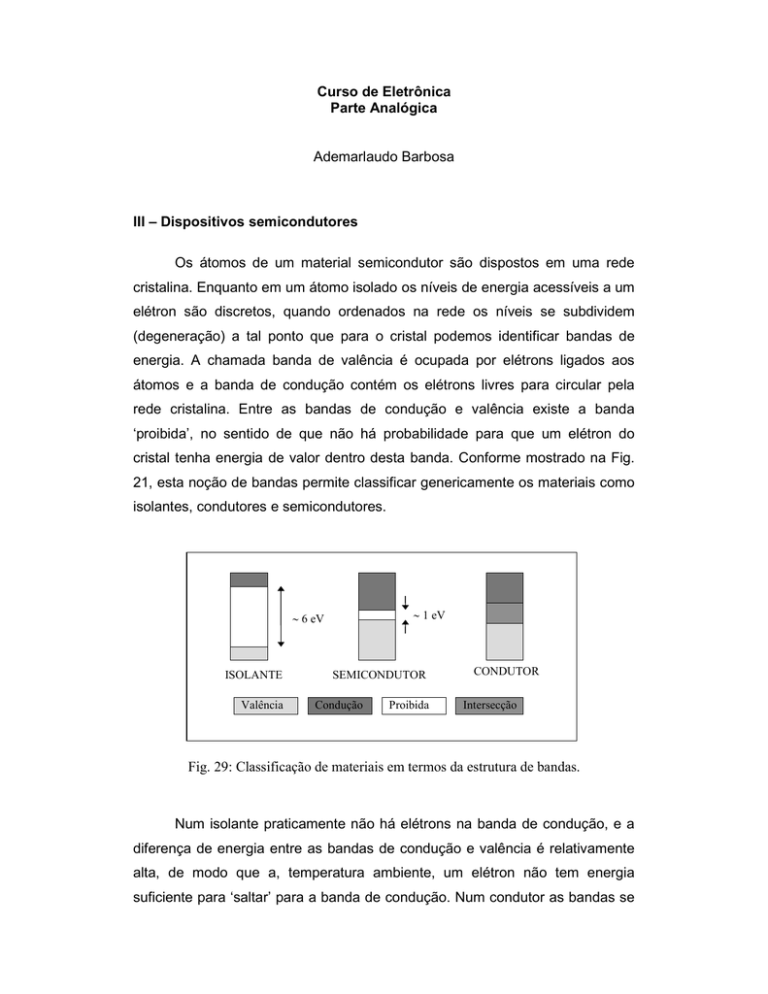

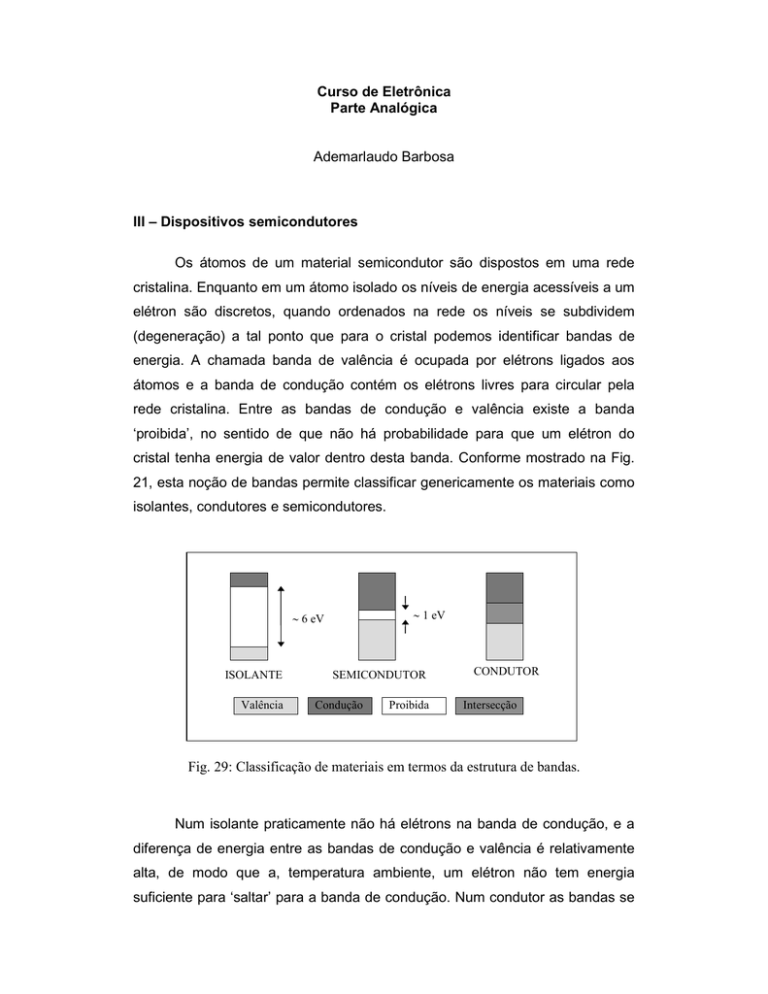

Os átomos de um material semicondutor são dispostos em uma rede

cristalina. Enquanto em um átomo isolado os níveis de energia acessíveis a um

elétron são discretos, quando ordenados na rede os níveis se subdividem

(degeneração) a tal ponto que para o cristal podemos identificar bandas de

energia. A chamada banda de valência é ocupada por elétrons ligados aos

átomos e a banda de condução contém os elétrons livres para circular pela

rede cristalina. Entre as bandas de condução e valência existe a banda

‘proibida’, no sentido de que não há probabilidade para que um elétron do

cristal tenha energia de valor dentro desta banda. Conforme mostrado na Fig.

21, esta noção de bandas permite classificar genericamente os materiais como

isolantes, condutores e semicondutores.

∼ 1 eV

∼ 6 eV

ISOLANTE

Valência

SEMICONDUTOR

Condução

Proibida

CONDUTOR

Intersecção

Fig. 29: Classificação de materiais em termos da estrutura de bandas.

Num isolante praticamente não há elétrons na banda de condução, e a

diferença de energia entre as bandas de condução e valência é relativamente

alta, de modo que a, temperatura ambiente, um elétron não tem energia

suficiente para ‘saltar’ para a banda de condução. Num condutor as bandas se

interceptam, e os elétrons podem se mover livremente pelos átomos do

material. No semicondutor a diferença de energia entre bandas é pequena, os

elétrons podem facilmente passar para a banda de condução deixando um

buraco na banda de valência.

3.1 Semicondutor intrínseco, dopado e junção

Na rede cristalina de um semicondutor puro (também denominado

intrínseco) a temperatura ambiente, existe uma probabilidade não nula para

que elétrons passem para a banda de condução, de modo que pares elétronburaco são constantemente gerados. Em condições de equilíbrio elétrico e

térmico a concentração ni de elétrons ou buracos pode ser expressa por:

ni ≈ T

3/ 2

e

−

Eg

2 kT

Onde T é a temperatura e Eg é a diferença de energia entre bandas a 0o

K. Para os semicondutores de fato utilizados em componentes eletrônicos, o

valor de ni a 300 K é de aproximadamente 2.5 x 1013 /cm3 (silício) e 1.5 x 1010

/cm3 (germânio). Essa concentração é pequena relativamente à densidade do

próprio semicondutor ( ∼ 1022 átomos/cm3).

O semicondutor intrínseco pode ser dopado com uma impureza que

tenha um elétron de valência a mais ou a menos. A Fig. 22 mostra o resultado

da adição de um átomo de impureza na rede.

Tanto silício quanto germânio são átomos tetravalentes. A substituição

de um dos átomos da rede por um átomo pentavalente equivale a acrescentar

um elétron à rede, enquanto que a substituição por um átomo trivalente

equivale a acrescentar um buraco. Segundo este critério os semicondutores

dopados são referidos como ‘tipo-n’ e tipo ‘tipo-p’. Nos semicondutores tipo-n a

corrente elétrica é principalmente determinada pelo movimento de elétrons, e

nos tipo-p pelo movimento de buracos. As impurezas tipicamente usadas são:

fósforo, arsênio, antimônio, gálio, índio e boro. Note-se que no semicondutor

dopado o equilíbrio elétrico é mantido, já que o átomo acrescentado também é

eletricamente neutro.

Elétron em excesso

Buraco em excesso

(a)

(b)

Fig. 30: Dopagem de semicondutores: (a) impureza tipo ‘n’, (b) impureza tipo ‘p’

Uma junção p-n é obtida quando se fabrica um semicondutor tipo-p

justaposto a um tipo-n. Na região de interface entre os dois, haverá tendência

dos elétrons a migrar para a região tipo-p, e dos buracos a migrar para a região

tipo-n. Dessa forma a região tipo-n torna-se carregada positivamente por haver

capturado buracos, e a região tipo-p torna-se carregada negativamente por

haver capturado elétrons. Um campo elétrico portanto se estabelece, com uma

diferença de potencial tipicamente da ordem de 1V.

3.2 Diodo semicondutor

O dispositivo resultante de uma junção p-n, como descrito em 3.1, é

chamado de diodo semicondutor. Ele pode ser polarizado de modo a favorecer

ou a bloquear a passagem de corrente, como mostrado na Fig. 31.

Se aplicamos uma diferença de potencial entre os terminais p e n, de

modo que do lado n o potencial seja inferior ao do lado p, estaremos

favorecendo a migração de portadores de carga através da junção. Haverá

portanto passagem de corrente pelo diodo. Aqui notamos que o movimento de

elétrons é oposto ao que convencionalmente adotamos para simbolizar a

direção da corrente elétrica (do potencial positivo para o negativo).

Invertendo a diferença de potencial, ou seja, aplicando ao lado n um

potencial superior ao do lado p, estaremos confinando ainda mais os elétrons à

região p e os buracos à região n. Neste caso somente uma pequena corrente

residual passa pela junção, em direção oposta à anterior. A magnitude desta

corrente residual depende da temperatura, da concentração de impurezas p e

n, e está também relacionada com as características do material semicondutor.

Sob polarização reversa, a região de interface da junção p-n fica desprovida de

portadores de carga. Quanto maior a diferença de potencial reversa, maior a

região desprovida de portadores de carga, chamada de ‘região de depleção’.

p

n

n

p

Fig.31: Polarização do diodo:

À esquerda: polarização favorável ⇒ passagem de corrente;

À direita: polarização reversa ⇒ aumento da região de depleção.

O comportamento da corrente, I, em função do potencial aplicado, V,

pode ser estimado e resulta em:

eV

I = I o e kT − 1

Io

(64)

eV

− kTo

= Ke

Onde Vo é a diferença de potencial presente quando a junção está em

equilíbrio (sem potencial externo aplicado) e K uma constante determinada

pelas propriedades geométricas da junção e pelas características do

semicondutor. Io é a corrente residual mencionada acima,

chamada de

‘corrente de saturação’. Vemos que para o diodo o comportamento de I em

função de V não é linear, como era o caso para resistores, capacitores e

indutores. Na Fig. 32 está esboçado um gráfico qualitativo de I(V).

I

V

≈ 0,6 Volts

Fig. 32: Comportamento genérico da corrente em função

da tensão para um diodo semicondutor

O fato de não haver uma relação linear entre I e V para o diodo implica

que

não

podemos

obter

analiticamente

a

função

de

transferência

correspondente (pelo menos não da maneira como fizemos para R, L e C).

Ademais, conforme veremos a seguir nos circuitos envolvendo diodos, a

resposta a uma oscilação harmônica não é facilmente modelável por uma

função matemática.

3.3 Circuitos elementares com diodos

3.3.1 Retificador de meia onda

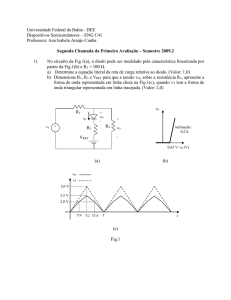

Na Fig. 24 está mostrado o mais simples dos circuitos com diodo. Uma

fonte de tensão alternada, de freqüência fixa e amplitude Ve (>Vo) é aplicado à

entrada do diodo. O resistor representa uma carga, e também um limitador de

corrente. Seu valor deve ser tal que a corrente que passa pelo circuito (Vs/R)

seja inferior a à corrente máxima (Imax) suportável pelo diodo. Imax é uma das

especificações fornecidas pelo fabricante.

Como visto em 3.2, haverá passagem de corrente quando a polarização

do diodo estiver no sentido favorável (Ve>0). Isto ocorre a cada meio ciclo de

onda, de modo que a tensão de saída reproduz a parte positiva da tensão de

entrada, a menos da queda de potencial sobre o diodo (Fig. 41). Assim o diodo

cumpre a função de retificar o sinal de entrada, eliminando sua parte negativa.

Ve

t

Vs

Ve

R

Vs

t

Fig. 33: Circuito retificador de meia-onda (esquerda) e sua

resposta a uma oscilação harmônica (direita).

3.3.2 Retificador de onda completa

Ao circuito da Fig. 33 faltaria inverter a parte negativa da tensão de

entrada, para que Vs apresente tensão positiva em todos os ciclos de onda. Isto

é obtido com o circuito mostrado na Fig. 34. O circuito é tal que, para o ciclo

em que Vs>0, corrente flui pelos diodos D1 e D3 , passando pela carga R. Para

o ciclo em que Vs<0, corrente flui pelos diodos D3 e D4, passando também pela

carga R. Nos dois ciclos a direção da corrente em R é a mesma. O efeito final é

portanto reproduzir na saída o valor absoluto da tensão de entrada, a menos da

queda de tensão sobre dois diodos.

Ve

D2

t

D1

Ve

Vs

D3

D4

R

Vs

t

Fig. 34: Circuito retificador de onda completa (esquerda) e

sua resposta a uma oscilação harmônica (direita).

Pode-se agora introduzir um capacitor de filtragem, C, antes da carga R,

tal que o produto RC seja muito maior que o período da oscilação de entrada, a

fim de se obter um nível de tensão na saída Vs. Um filtro LC seria ainda mais

recomendável, desde que os valores de L e C sejam elevados. Como vimos no

capítulo anterior, para ω> ωo o ganho do filtro L-C decresce com 1/ω2, enquanto

que para o filtro R-C o ganho decresce com 1/ω. Escolhendo ωo≈0 (ou seja, L e

C elevados), a filtragem L-C praticamente só permite a passagem de um nível

de tensão constante. A Fig. 35 apresenta um circuito para gerar um nível de

tensão constante a partir de uma fonte de corrente alternada. Foi acrescentado

um transformador para converter a amplitude de tensão de entrada à amplitude

esperada na saída.

D2

D1

L

Vs

Ve

D3

D4

C

C

R

Fig. 35: Gerador de nível de tensão a partir de uma fonte de corrente alternada

3.3.3 Diodo Zener, Fonte de Tensão

Para ser qualificado como fonte de tensão, o circuito da Fig. 35 teria

ainda que assegurar que a tensão de saída não varie. Entretanto, variações da

corrente sobre a carga (R), ou da tensão de entrada, ou mesmo quedas de

tensão sobre os indutores implicam variações na tensão de saída. Para

contornar este inconveniente utiliza-se outra peculiaridade dos diodos.

Em 3.2 notamos que em um diodo polarizado na direção oposta à

condução de corrente, a diferença de potencial tende a aumentar a região de

depleção, confinando elétrons e buracos em lados opostos da junção.

Aumentando esta diferença de potencial chega-se a um limite de ruptura, Vz, a

partir do qual elétrons são desprendidos de suas posições na rede cristalina, e

acelerados em direção ao eletrodo correspondente. Um elétron nestas

condições colide com outros elétrons, que por sua vez colidem com outros e

contribuem em uma avalanche de carga elétrica. Resulta que uma corrente

importante passa pelo diodo (Fig. 36). Esta corrente não é necessariamente

destrutiva. Fabricam-se diodos que podem suportar correntes reversas de até

alguns amperes.

I

Vz

V

Fig. 36: Comportamento da corrente em função

da tensão para um diodo Zener.

Os diodos que funcionam sob este regime são chamados de diodos

Zener (Clarence Zener propôs uma explicação para o aumento acentuado da

corrente na região de ruptura). Eles são indicados para manter fixo um nível de

tensão, Vz, independentemente de variações de corrente. O circuito da Fig. 37

mostra a utilização de um diodo Zener como regulador de tensão. Desde que

Vfonte seja maior que Vz, podemos escrever:

V fonte = IR fonte + V ⇒ I =

V fonte

R fonte

−

1

R fonte

V

O ponto de intersecção da equação de reta acima com a curva I(V) para

o diodo Zener dá a corrente Ifonte que passa sobre o resistor Rfonte. Sobre a

carga passa corrente Icarga = V/Rcarga. Enquanto Icarga for menor que Ifonte, o

diodo atua como regulador de voltagem, ou seja, supre corrente de modo a

manter fixo o nível de tensão Vz. Caso contrário a queda de tensão sobre Rfonte

é muito grande para manter o diodo zener na tensão de ruptura.

Rfonte

Vfonte

V=Vz

Rcarga

Fig. 37: Regulagem de tensão com diodo Zener.

3.3.4 Modulação e Demodulação de Frequência

Em (59) está expressa uma função I(V) válida para o comportamento do

diodo semicondutor. Esta função é da forma:

f ( x) = K (e x − 1)

Que expandida em série de potências de x leva a:

f ( x) = Kx +

K

2

x 2 + K6 x 3 + ...

Para valores pequenos de tensão (<<1V), podemos então exprimir I(V)

por:

I = a1V + a 2V 2

Suponhamos que seja injetado em um diodo um estímulo composto pela

sobreposição de duas oscilações harmônicas:

V = V (t ) = V1 Sen(ω 1t ) + V2 Sen(ω 2 t )

A corrente de saída será então expressa por:

I=

a2

2

[

(V12 + V22 ) − a22 V12 Cos (2ω 1t ) + V22 Cos (2ω 2 t )

+ [a1V1 + (a1V2 + 2a 2V1V2 )Sen(ω 2 )t ]Sen(ω 1t )

]

O último termo representa uma oscilação harmônica de frequência ω1,

cuja amplitude está modulada pela frequência ω2. Se favorecemos este termo

na saída do diodo, obtemos portanto um circuito modulador de amplitude em

frequência. Isto é feito, conforme vimos no capítulo anterior, com filtros L-C

que selecionam uma frequência específica. O circuito de modulação é

mostrado na Fig. 38.

V(t)=[2+Sinω2t]Sinω1t

3

ω1=10ω 2

2

L1 C1

L1 C1

1

ω1

V(t)

ω1||ω2

0

-1

-2

ω2

-3

0

20

40

60

80

100

t

Fig. 38: Circuito modulador de amplitude em freqüência

(esquerda) e seu sinal de saída (direita).

O funcionamento adequado do circuito requer que a onda portadora

tenha frequência ω1 muito superior a ω2, e que os filtros (L1-C1) estejam

sintonizados em ω1. Note-se que, como ω2<<ω1, de acordo com a função de

transferência para filtros L-C, embora o filtro não esteja sintonizado em ω2 esta

frequência passa à saída com ganho 1.

O circuito da Fig. 38 representa o princípio básico utilizado na

transmissão de sinais de rádio e vídeo. A recepção, ou demodulação, é obtida

por exemplo com o circuito da Fig. 39, onde a constante de tempo do filtro de

saída é escolhida tal que RC >> (ω1)-1. Com esta escolha a onda portadora é

eliminada, e a saída Vs traz apenas a contribuição das frequências ω2<<ω1 que

se pretende sintonizar.

L1 C1

ω1||ω2

RC<<ω1

Vs

Fig. 39: Circuito demodulador de frequência

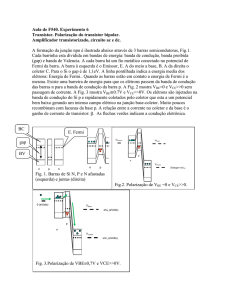

3.4 Transistores Bipolares

Transistores bipolares são dispositivos semicondutores em que há duas

junções, cada uma delas semelhante à que está presente nos diodos. Há duas

possibilidades básicas de construção, como mostrado na Fig. 40. Três

terminais são disponibilizados em um transistor, conectados a elementos

denominados emissor, base e coletor.

Nos transistores a junção base-emissor é normalmente polarizada de

modo a favorecer a passagem de corrente (≈ 0.6V). Já a junção base-coletor é

polarizada reversamente. Sabemos que para o diodo configurado entre base e

emissor uma pequena variação de tensão na base implica uma variação

proporcionalmente muito maior da corrente (Ver Fig. 41). Esta corrente é

fornecida pela junção base-coletor, ou seja, os portadores de carga requeridos

na junção base-emissor para transmissão de corrente provêm da junção basecoletor.

Um transistor permite portanto o controle de corrente a partir de

pequenas variações de tensão. A corrente efetivamente aplicada à base, Ib, é

pequena em comparação à corrente que passa pelo emissor, Ie, fornecido pela

junção base-coletor. O transistor é tanto mais eficiente quanto maior for a

fração de corrente de emissor relativamente à corrente de coletor.

pnp

npn

Junções

c

c

Símbolo

Circuito

b

b

e

e

c

c

b

b

e

Fig. 40: representações de transistores bipolares

Expressamos esta fração como:

e

α=

Ic

Ie

A corrente total disponibilizada no emissor é dada pela soma da corrente

de base (suprida quando se aplica uma ‘tensão de controle’ à base), mais a

corrente de coletor (suprida pela junção base-coletor). Como Ie=Ic+Ib, podemos

também escrever:

Ic =

α

1−α

I b ≡ βI b

(60)

O valor de α é um número muito próximo da unidade, enquanto que o

valor de β como definido acima tipicamente assume valores entre 102 e 103.

Por isto o parâmetro β é geralmente usado para exprimir a eficiência, ou ganho

em corrente, do transistor.

Entretanto, para que o transistor opere como anunciado acima, deve

haver uma polarização mínima entre coletor e emissor. Ou seja, uma vez

polarizada a junção base-emissor para que haja condução de corrente,

também deve haver uma polarização VCE ( = VC-VE) entre base e coletor para

que a corrente fornecida pela junção base-coletor flua pelo emissor. Este fato

define uma característica fundamental dos transistores e está expresso na Fig.

41.

IC

(VBE)3

(VBE)2

(VBE)1

Região de Operação

VCE

Fig: 41: Curvas características IC x VCE para transistores bipolares

Conforme mostrado na figura, existe uma região de operação para a

qual a corrente de coletor, IC, é praticamente independente da tensão de

polarização VCE. O valor de IC é determinado por VBE ( = VB-VE), a tensão de

polarização entre base e emissor. O comportamento de IC como função de VBE

pode ser avaliado analiticamente. De fato é o mesmo da junção pn definido

pela equação (59), conhecido como ‘modelo de Ebers-Moll’:

BE

I C = I S e VT − 1 , com VT =

V

kT

e

(61)

O valor de VT a temperatura ambiente é de aproximadamente 26 mV. IS

é chamado de corrente de saturação do transistor, parâmetro que depende da

temperatura.

Mais genericamente podemos assumir que IC é uma função das duas

tensões de polarização e escrever:

I C = I C (VBE ,VCE )

∂

∂

dI c = ∂VIBEC dVBE + ∂VICEC dVCE

(62)

Com (62) passamos a tratar as variações das grandezas quiescentes

dos transistores. As grandezas quiescentes, ou estáticas, são as tensões e

correntes de polarização (IC, IB, IE, VB, VC, VE), que definem a região de

operação do transistor. As variações destes valores estáticos são precisamente

os sinais elétricos tratados nos circuitos envolvendo transistores. Convencionase usualmente referir-se aos sinais com letras minúsculas, enquanto que os

parâmetros estáticos são escritos com letras maiúsculas. Assim (62) é

expressa como:

ic =

∂I C

∂V BE

v BE +

∂I C

∂V CE

v CE

Ou, de acordo com (60)

ic = β

∂I B

∂VBE

v BE +

∂I C

∂VCE

v CE

Definindo agora:

r=

∂VBE

∂I B

, eρ =

∂VCE

∂I C

(63)

Chegamos a:

ic = βr v BE + ρ1 v CE

r, β e ρ são parâmetros intrínsecos do transistor que definem suas

características de funcionamento dinâmico. r e ρ têm dimensão de resistência

elétrica. Podemos ver pela Fig. 41 que, na região de operação, ρ equivale a

uma resistência de valor muito elevado, já que IC praticametne não varia com

VCE. Neste contexto, admitindo que a base seja o terminal de entrada, r

equivale a uma resistência de entrada intrínseca ao transistor:

r≈

β

iC

v BE =

v BE

iB

(64)

A partir do modelo de Ebers-Moll podemos também ver que:

V BE

∂I C

I e VT

I + I S IC

= S

= C

≈

∂v BE

VT

VT

VT

A aproximação acima é válida porque IC é tipicamente muito maior que

IS. Note-se que IS, segundo (61), é a corrente residual que permanece quando

a junção base-emissor é polarizada reversamente. Portanto podemos também

estimar que, de acordo com a definição (63):

r≈

VT

IB

≈

26 mV

I B ( mA)

A expressão acima mostra diretamente como a corrente de polarização

da base define a resistência de entrada do transistor.

3.5 Circuitos básicos com transistores bipolares

Conforme apresentado acima, o transistor é um dispositivo com três

terminais. Um circuito genérico pode ser visto como um quadrupolo com dois

terminais de entrada e dois terminais de saída, conforme mostrado na Fig. 42.

No caso mais simples um dos terminais da entrada e um da saída são comuns

e correspondem ao ‘terra’ ou referência de potencial zero. Para o transistor

podemos conceber três modos de funcionamento

básicos que permitem a

exploração de suas propriedades: coletor comum (a), emissor comum (b) e

base comum (c). A seguir avaliamos alguns parâmetros de desempenho que

evidenciam as particularidades de cada um destes modos: ganho em tensão

(Av), ganho em corrente (Ai), impedância de entrada (Ze) e impedância de saída

(Zs). O ganho em potência (Ap) é dado pelo produto dos ganhos em corrente e

em tensão. Outro parâmetro importante é a banda passante, mas este só será

abordado quando considerarmos a influência de capacitâncias sobre o

desempenho de transistores [§?] . Supõe-se que em cada caso o transistor

esteja adequadamente polarizado, ou seja, que IC, IB, IE, VC, VB e VE o

configurem para sua região de operação como indicado na Fig.

41. Esta

configuração requer o uso de resistores de polarização que não estão

mostrados nos circuitos tratados. Tomamos o caso do transistor tipo npn. Os

resultados para o tipo pnp podem ser obtidos pelo mesmo procedimento.

(a)

Base

(b)

Emissor

Coletor

Base

(c)

Coletor

Emissor

Emissor

Coletor

Base

Fig. 42: Possíveis modos de funcionamento de transistores

Coletor comum (a), emissor comum (b), base comum (c)

3.5.1 Modo coletor comum

Neste modo o coletor é comum à entrada e à saída, estando conectado

a uma fonte de tensão VCC, como ilustrado na Fig. 43. Embora não esteja

diretamente conectado ao ‘terra’, para efeitos de propagação de sinais a tensão

VCC representa também uma referência de potencial constante equivalente ao

próprio terra.

Notamos inicialmente que, como existe uma junção ou diodo polarizado

para conduzir corrente entre base e emissor, a diferença de tensão entre estes

dois terminais, VBE, é praticamente fixa e vale cerca 0,6 Volt (Ver Fig. 32). Isto

se deve ao comportamento exponencial da corrente de emissor em função de

VBE.

VCC

ve

Vs

RE

Fig. 43: Modo coletor comum

Portanto a própria polarização do transistor impõe:

V B − V E ≈ 0,6 ≈ constante

Os sinais elétricos de entrada (ve) e de saída (vs) são justamente as

variações de VB e de VE, de modo que podemos afirmar que:

ve ≈ v s

Ou seja, o ganho em tensão é aproximadamente unitário. Este resultado

pode ser obtido de maneira mais metódica. Consideremos as quedas de

tensão deste a base até o terra quando há um sinal de entrada. Vemos que:

v e = ri B + RE i E

Onde riB é a queda de tensão na junção base-emissor devida à presença

da resistência de entrada intrínsica do transistor, r. Como iE=iC+iB, e iC=β iB,

encontramos:

v e = [r + (β + 1)RE ]i B

O sinal de saída é a variação de tensão sobre o resistor RE:

v s = RE i E = (β + 1)RE iB

Portanto o ganho em tensão é dado por:

Av =

vs

ve

=

(β +1)RE

r + (β +1)RE

Lembrando que (β+1)RE é tipicamente >> r, vemos que Av ≈1 e que

Av≤1.

Para obter o ganho em corrente basta ver que

i s = i E = (β + 1)i B = (β + 1)ie

Donde:

Ai =

is

ie

= β +1 ≈ β

A impedância de entrada define-se como o quociente entre tensão de

entrada e corrente de entrada, ou seja, para o coletor comum:

Ze =

ve

ie

=

vb

iB

=

[r + (β +1)R E ]i B

iB

= r + (β + 1)R E ≈ βR E

Para a impedância de saída supomos que existe uma carga conectada à

saída do circuito, e definimos impedância de saída como a queda de tensão

devida à presença da carga dividida pela corrente efetivamente fornecida:

Zs =

δv

is

No circuito do coletor comum, como mostrado na Fig. 43, a carga é

representada pelo resistor RE. Caso haja uma carga extra, R, a carga efetiva

será dada pela combinação RE||R (RE e R em paralelo).

Para calcular Zs, podemos notar que o circuito do coletor comum é

equivalente a um divisor de tensão, como mostrado na Fig. 44 (a).

(a)

(b)

r/(β+1)

r

ve (=vB)

vs (=vE)

iB

vs (=vE)

iE

RE

iE

ve (=vB)

iE

RE

Fig. 44: Circuitos equivalentes para o modo coletor comum

Entretanto, como o transistor é um componente ativo, a corrente (iB) que

passa pelo resistor de entrada (r) é menor que a corrente (iE) sobre o resistor

de saída (RE). O transistor pode ser considerado como um gerador de corrente.

Para reduzir o circuito a um divisor de tensão passivo, notamos que a queda de

tensão de ve para vs pode também ser expressa em função de iE. Isto equivale

a supor que o resistor r é dividido pelo fator (β+1), já que iE=(β+1)iB, como

mostrado na Fig. 44 (b).

Podemos então escrever:

vs =

RE

r

β +1

+ RE

ve =

( β + 1 )R E

r + ( β + 1 )R E

ve

A expressão acima reproduz o resultado obtido anteriormente para Av.

Mas a analogia com o circuito divisor de tensão permite-nos visualizar mais

claramente o conceito de impedância de saída. A queda de tensão devida à

carga é a queda de tensão sobre o resistor de entrada, e a corrente fornecida à

carga é a corrente de emissor, iE. Zs pode então ser expressa como:

Zs =

ri B

iE

=

riB

(β +1)iB

=

r

β +1

Ou seja, a impedância de saída é efetivamente representada pelo

resistor r/(β+1) que aparece na Fig. 44 (b).

Um gerador de tensão perfeito apresentaria impedância de saída nula, o

que significaria que o gerador é capaz de manter o mesmo valor de tensão na

saída independentemente da corrente consumida pela carga.

Analisando as características do coletor comum, podemos concluir que é

um circuito recomendável para funcionar como interface entre outros circuitos.

Isto porque apresenta impedância de entrada elevada, portanto não exige

muita corrente do circuito do qual recebe sinais. Por outro lado apresenta

impedância de saída baixa, sendo por isto capaz de fornecer corrente ao

circuito de carga sem muita queda de tensão na saída.

O ganho em tensão praticamente unitário e o alto ganho em corrente

traduzem o fato de o coletor comum transferir o sinal de entrada à saída,

fornecendo a corrente necessária para que não haja queda de tensão.

3.5.2 Modo emissor comum

Neste modo o sinal de saída é tomado no terminal coletor, estando o

emissor conectado ao terra, portanto comum à entrada e à saída, como

mostrado na Fig. 45 (a).

VCC

VCC

(a)

(c)

(b)

RC

RC

vs

ve

VCC

RC

vs

ve

RE

vs

ve

RE

C

Fig. 45: Modo coletor comum, com (a) e sem (b) resistor de emissor, e com

capacitor de desacoplamento (c).

As variações de tensão no terminal coletor correspondem diretamente

ao sinal de saída. Podemos portanto escrever:

VC = VCC − RC I C

⇒ v s = − RC iC

O sinal de entrada é vB, que, conforme vimos na seção anterior, tem

aproximadamente a mesma amplitude que vE :

v e = v B ≈ v E = R E i E ≈ R E iC

Assim chegamos a uma primeira estimativa do ganho em tensão:

Av ≈

− RC iC

RE iC

= − RCE

R

Um circuito emissor comum pode então constituir um amplificador de

tensão, desde que RC>RE. Av tem valor negativo, o que indica que o sinal de

saída é invertido relativamente ao de entrada. O máximo ganho do amplificador

seria obtido quando RE≈0. Essa possibilidade se realiza quando o terminal

emissor é diretamente conectado ao terra, ou quando introduzimos um

capacitor de desacoplamento, como ilustrado nas Figs. 45 (a) e (b). Neste

último caso o resistor de emissor contribui para fixar a polarização do transistor,

mas os componentes espectrais de mais alta frequência do sinal de entrada

são passados ao terra através da (menor) impedância representada pelo

capacitor.

Na prática o ganho é limitado, como podemos notar ao analisar mais

rigorosamente o circuito, incluindo a contribuição da resistência de entrada do

transistor. Mesmo que o emissor seja conectado ao terra, permanece a

resistência interna, r, que implica uma ligeira queda de tensão do sinal de

entrada:

v e = riB + RE iE = [r + (β + 1)RE ]iB

(β )

β

R

i

R

∴ Av = − [r +(βC+1)RB E ]iB = − r +(β +C1)RE

Mesmo nos casos em que RE=0, o valor do ganho está limitado a:

Av ≤ −

β RC

r

O ganho em corrente é dado por:

i s = iC = βi B = βie

⇒ Ai = β

Para a impedância de entrada encontramos:

Ze =

vB

iB

=

[r + ( β +1)RE ]iB

iB

= r + (β + 1)RE

Notamos que Ze pode apresentar valor tanto mais elevado quanto maior

for o valor de RE. Entretanto, já que Av depende inversamente de RE, aumentar

a impedância de entrada implica reduzir o ganho.

Caso RC represente a própria carga conectada à saída do emissor

comum, a variação de tensão de coletor devida à presença da carga tem

origem na resistência intrínseca da junção base-coletor, definida em (63). A

corrente fornecida à carga é ic, portanto:

Zs ≈

− ρiC

iC

= −ρ

O fato de o valor ser negativo significa que a corrente flui da carga ao

transistor.

Caso RC a carga seja representável por uma resistência externa, R,

conectada à saída, a combinação de RC||ρ é responsável pela queda de tensão

devida ao circuito de carga. A corrente de saída é iC. O valor máximo de

corrente efetivamente utilizada por R seria ic, quando R fosse muito menor que

RC. Com isto podemos estimar a impedância de saída:

Zs =

(RC || ρ )ic

iC

= RC || ρ

Os dois casos estão ilustrados na Fig. 46.

ρ

ve (=vB)

iC

iC

vs (=vC)

ρ||RC

ve (=vB)

RC

(a)

vs (=vC)

iC

iC

R

(b)

Fig. 46: Circuitos equivalentes para o modo emissor comum:

(a) RC é a carga, (b) carga externa R.

Como ρ tipicamente apresenta valor elevado (impedância de um diodo

polarizado reversamente) e como RC também tende a ter valor elevado num

circuito amplificador, concluímos que a impedância de saída do circuito coletor

comum é alta. Isto o torna inadequado como circuito transmissor de sinal,

apesar de funcionar como amplificador.

A fim de preservar seu desempenho como amplificador, um circuito em

modo emissor comum deve ser intermediado por outro circuito que apresente

alta impedância de entrada e ganho em corrente, como é o caso do modo

coletor comum.

3.5.3 Modo base comum

Conforme mostrado na Fig. 47, no modo base comum o sinal entra pelo

terminal emissor, e sai pelo terminal coletor. A base é conectada a uma tensão

de referência constante, comum ao coletor e ao emissor.

Caso desprezemos a corrente de entrada em comparação com a

corrente de emissor, chegamos à seguinte avaliação para Av e Ai:

Av = −RRECiEiC = − (ββ+R1C)RiBE iB = − (ββ+R1C)RE ≈ − RRCE

Ai =

− iC

iE

βi

= − (β +1B)iB ≈ −1

Para a impedância de entrada notamos que uma variação de tensão no

terminal emissor (=sinal de entrada) implica uma queda de tensão através da

junção base-emissor, onde passa corrente iB pela resistência interna r. Como

vimos anteriormente, esta situação é equivalente a uma queda de tensão sobre

um resistor r/(β+1), por onde passa corrente iE. Pelo menos uma fração desta

corrente passa pelo resistor RE. Vemos assim que a corrente de entrada é

dividida pela associação de dois resistores, de modo que:

Ze =

( )|| R

r

β +1

E

=

rRE

(β +1)RE + r

≈

r

β +1

VCC

RC

vs

I[emissor]

I[entrada]

VBB

ve

I’

RE

Fig. 47: Modo base comum e representação do nó de correntes na entrada.

I’ é a corrente que passa pelo resistor RE.

Em geral não se pode desprezar a corrente de entrada, Ie, diante da

corrente de emissor, IE. Notamos também que no circuito base-comum a

corrente de entrada pode estar ‘saindo’ do circuito. Nesse caso podemos

escrever:

I E = I ' + Ie

Onde I’ é a corrente que passa pelo resistor RE.

Portanto a tensão de entrada é dada por:

ve = RE i' = RE (iE − ie ) = RE (iE − vZee )

Substituindo o valor encontrado acima para Ze, chegamos a:

ve =

rRE2

rRE + r + RE ( β +1) E

i =

rRE2 ( β +1)

rRE + r + RE ( β +1) B

i

Donde podemos calcular:

Av = vves =

− βRC iB

ve

=

− βRC [ rRE + r + RE ( β +1)]

rRE2 ( β +1)

Para obter o ganho em corrente fazemos

Ai = iies =

v

− Rs

C

ve

Ze

= − vves

+ +

ZE

RC

= − Av

ZE

RC

β+

1)]

E r RE (

⇒ Ai = − [ rR

[ r + RE ( β +1)] RC

Caso a corrente de entrada esteja ‘entrando’ no circuito (em sentido

oposto à corrente de coletor), Av e Ai devem ser invertidos, ou seja, deve ser

suprimido o sinal ‘menos’ em Av e em Ai. Neste caso a montagem coletor

comum não atua como circuito inversor.

Para a impedância de saída vale a mesma análise feita para o caso do

emissor comum, visto que no modo base comum o sinal de saída também é

dado pela variação de tensão no coletor:

Zs = ρ

(se RC é a carga)

Z s = ρ || RC

(se a carga é externa)

Vemos então que o modo base comum é semelhante ao modo coletor

comum, a menos pelo fato de apresentar baixa impedância de entrada e não

prover ganho em corrente. Esta característica é importante quando se

pretenda, por exemplo, converter uma variação de corrente em variação de

tensão.

Os resultados obtidos para os três modos estão resumidos na tabela

apresentada na Fig. 48.

Ze

Zs

Coletor comum

r + (β + 1)RE ≈ βRE

Emissor comum

r + (β + 1)R

Base comum

rRE

(β +1)RE + r

≈

r

β +1

r

β +1

Av

Ai

Ap

(β +1)RE

r + (β +1)RE

β+1≈β

≈β

β

−

ρ ou RC||ρ

− r +(β +C1)RE

ρ ou RC||ρ

±

βR

βRC [ rRE + r + RE ( β +1)]

rRE2 ( β +1)

+ +

β+

1)]

E r RE (

± [ rR

[ r + RE ( β +1)] RC

β 2 RC

r + (β +1)R E

[ rRE + r + RE ( β +1)]2

[ r + RE ( β +1)]rRE2 ( β +1)

Fig. 48: Resumo das propriedades de montagens básicas com transistores bipolares

3.6 Transistores a efeito de campo

É possível obter um dispositivo semicondutor de comportamento

semelhante ao transistor bipolar, com apenas um tipo de junção. O princípio de

funcionamento deste dispositivo é mostrado na Fig. 49.

Dois terminais condutores são previstos nas extremidades opostas de

uma região dopada com excesso de portadores tipo n. Entre estes terminais

implanta-se uma região com excesso de portadores tipo p. Os terminais

condutores são denominados ‘fonte’ (referido como S, de source) e ‘dreno’

(referido como D, de drain). O terceiro terminal é implementado na região p, e é

denominado ‘porta’ (referido como G, de gate). O próprio dispositivo é referido

como FET (field effect transistor), por razões que ficarão claras a seguir, e é

simbolizado como mostrado na Fig. 49

D

D

(a)

(b)

n

n

D

p

p

p

G

p

S

S

S

Fig. 49 Esquema para o transistor a efeito de campo com canal n

(a) VGS=0, (b) VGS <0.

Estabelecendo-se uma diferença de potencial entre D e S (VDS)

favorece-se a passagem de corrente de S a D (canal S-D). Entretanto, o valor

desta corrente não varia linearmente com VDS. De fato, suponhamos que porta

e fonte estejam ao mesmo potencial (VGS=0). À medida em que se aumenta

VDS, forma-se uma região de depleção cada vez maior entre G e D, como

mostrado na áreas pontilhada da Fig. 49 (a).

Para valores de VDS muito pequenos o volume da região de depleção é

desprezível, e a corrente nesse caso varia linearmente com VDS. Mas se

aumentamos o valor de VDS, e consequentemente o volume da região de

depleção, a resistividade do canal S-D também aumenta, de modo que relação

de linearidade entre corrente e VDS é gradualmente perdida. Continando a

aumentar a tensão VDS , chega-se a uma situação limite em que as duas

regiões de depleção mostradas na Fig. 49 praticamente se encontram através

do canal. A partir deste limite, incrementos de VDS são contrabalanceados pelo

incremento da resistividade do canal, de tal forma que a corrente permanece

aproximadamente constante para uma ampla faixa de valores de VDS.

O valor de VDS para o qual a situação limite é atingida é conhecido como

tensão de ruptura (pinchoff) do canal. Esta tensão marca o início da região de

operação do dispositivo como um transistor. Além da região de operação, ou

seja, para valores de VDS muito elevados, ocorre ruptura da própria junção pn.

Caso a tensão VGS seja menor que zero a mesma análise é válida, mas

observamos que a corrente obtida na região de operação é menor do que a

verificada quando VGS=0. Isto se deve essencialmente ao fato de que VGS <0

se opõe à passagem de corrente pelo canal (diodo polarizado reversamente).

Nesse caso a região de depleção se estende também em direção à fonte, com

mostrado na Fig. 49 (b).

A Fig. 50 mostra os distintos regimes de funcionamento do transistor a

efeito de campo num gráfico de corrente no dreno, ID, em função de VDS. A

região ôhmica corresponde aos valores muito pequenos de VDS.

Naturalmente a tensão VGS não deve ser positiva. Nesse caso haveria

condução de corrente no sentido oposto a ID no diodo configurado na junção

pn, o que impediria o funcionamento regular do transistor.

ID

Ruptura (pinchoff)

(VGS)1

(VGS)2

(VGS)3

Região de Operação

VDS

Fig: 50: Curvas características ID x VDS para transistores a efeito de

campo com canal n.

Concluímos que VGS define a corrente ID no transistor a efeito de campo,

assim como VBE define IC no transistor bipolar.

3.7 Tipos de transistores a efeito de campo

O comportamento ID x VGS acima descrito para o transistor a efeito de

campo também pode ser modelizado por uma função matemática. Encontra-se

que, para um dispositivo com canal n:

(

I D = I DSS 1 + VVGST

)

2

(65)

IDSS (drain to source with gate shorted) é a corrente obtida quando

VGS=0, portanto corresponde ao máximo valor possível para ID no transistor.

Para ID=0 encontramos VGS=-VT, o que significa que VT

é a tensão de

polarização reversa abaixo da qual não há passagem de corrente pelo canal.

Ou seja, VT é a máxima polarização reversa admissível enquanto o dispositivo

atue como transistor.

A equação (65) é equivalente ao modelo de Ebers-Moll apresentado

para transistores bipolares. Como ID é também determinada por VDS na região

de operação, podemos igualmente generalizar sua expressão matemática e

identificar os parâmetros dinâmicos intrínsecos ao FET:

I D = I D (VGS ,VDS )

⇒ dI D =

∂I D

∂VGS

dVGS + ∂∂VIDSD dVDS

Em termos dos sinais elétricos, podemos re-escrever a equação acima

como:

i D = sv GS + ρ1 v DS

Onde introduzimos as definições:

s=

∂I D

∂VGS

ρ=

,

∂VDS

∂I D

Na região de operação ρ ≈ ∞, pelo que podemos interpretar s como uma

transcondutância, que relaciona tensão de entrada e corrente de saída.

1

s

≈

v GS

iD

(66)

3.7.1 Canal p

O modelo a que se refere a equação (65) é conhecido como ‘FET canal

n’ ou n-FET. Caso substituamos o semicondutor presente no canal por outro

dopado com impurezas do tipo p e o gate por um do tipo n, chegamos a um

dispositivo que também opera como transistor. A diferença é que no FET com

canal p a polarização VGS tem que ser invertida relativamente ao n-FET. A

equação que expressa ID em função de VGS nesse caso muda para:

(

I D = I DSS 1 − VVGST

)

2

(67)

Para o p-FET, de acordo com a argumentação anterior, devemos

polarizar a junção com VGS>0. A Fig. 51 mostra o comportamento gráfico de

(65) e (67).

ID

ID

n-FET

p-FET

IDSS

IDSS

VT

VT

VGS

VGS

Fig. 51: Representação de ID(VGS) para n-FET e p-FET.

3.7.2 MOS-FET, IG-FET

A Fig. 52 mostra um esboço da implementação prática de um FET de

junção (n ou p), como descrito acima. Note-se que o eletrodo gate está em

contado direto com o canal semicondutor.

G

S

Substrato

D

Canal

Fig. 52: Esboço da implementação de um FET

Há outras possibilidades de implementação em que o gate é fisicamente

isolado do canal. Na Fig. 53 (a) por exemplo está mostrada uma estrutura em

que o gate é separado do canal por uma camada de óxido de silício. Por esta

razão o transistor é chamado MOSFET (metal oxide FET) ou IGFET (insulated

gate FET). Quando se aplica tensão entre gate e source, VGS<0, os elétrons do

canal n são repelidos, gerando uma região em que não há portadores de

carga. Esta região é equivalente à região de depleção formada no FET de

junção. Com isto se reproduz o princípio de funcionamento descrito

anteriormente para o n-FET. A tensão de pinchoff é atingida quando a região

de depleção se estende sobre todo o canal. Também pode ser obtido um pFET. Neste caso a região do canal é formada por um semicondutor dopado

com impureza tipo p, e trabalha-se com VGS≥0.

S

G

D

S

G

D

SiO2

n

p

SiO2

p

Substrato

(a)

Substrato

(b)

Fig. 53: Esquemas para depletion MOSFET (a) e enhanced MOSFET (b)

Suponha-se agora que o canal n é suprimido, como mostrado na Fig. 53

(b) e que o substrato seja um semicondutor tipo-p. Nesta situação, quando

VGS>0 os portadores de carga do substrato (p) são repelidos e começa a

formação de uma região desprovida de portadores de carga na superfície entre

o substrato e o óxido de silício. Acima de uma tensão limite, VGS≥VT, começa a

passagem de corrente entre source e dreno (desde que haja polarização VDS,

ou seja, que o transistor esteja polarizado em sua região de operação).

Transistores operando sob esse regime são denominados enhancement

MOSFETs.

Voltando ao caso da Fig. 53 (a) e supondo que o substrato seja um

semicondutor tipo-p, notamos que para VGS>0 a espessura do canal (n) terá

sido ocupada pela região de depleção, e começa se formar uma região de

depleção (desprovida de portadores de carga) no substrato, pelo mesmo

processo que ocorre no enhancement MOSFET. Portanto pode haver

passagen quando VGS>0. Finalmente são possíveis os três comportamentos da

curva ID(VGS) especificados na Fig. 54.

ID

ID

ID

IDSS

VT

VT

Depletion n-FET

VT

VGS

VGS

VGS

Enhancement

n-MOSFET

Enhancement &

depletion n-MOSFET

Fig. 54: Características ID(VGS) possíveis para FETS.

3.8 Circuitos básicos com FETs

A principal característica dos transistores a efeito de campo é a alta

impedância de entrada. No caso dos MOSFETs, como o terminal de entrada

está fisicamente isolado dos outros terminais, a resistência de entrada atinge

valores altíssimos, tipicamente da ordem de 1014 Ω. Sinais elétricos são

transmitidos devido essencialmente a variações de campo elétrico através do

material isolante presente entre o eletrodo de entrada e o semicondutor. Por

isto é pertinente a denominação “transistores a efeito de campo”. Também no

caso dos FETs em que o gate está em contato com a junção, ou J-FETS, como

os ilustrados na Fig. 52, a impedância de entrada é alta porque a junção

semicondutora gate-source é polarizada reversamente. A junção equivalente

nos transistores bipolares, base-emissor, é polarizada para favorecer

passagem de corrente. Portanto a impedância de entrada nos FETs

é

normalmente muito maior do que em transistores bipolares.

Para efeitos práticos pode-se assumir que a corrente de entrada nos

FETs é nula. Acrescente-se que este fato implica baixo ruído eletrônico na

entrada, o que também representa uma característica importante dos FETs.

Os modos de operação expostos para transistores bipolares podem ser

obtidos também com FETs. Consideremos por exemplo o equivalente à

montagem emissor-comum, como mostrada na Fig. 55.

VDD

RD

vs

ve

RG

RS

C

Fig. 55: FET em modo source-comum.

Notamos que vs=-RDiD, e que ve≡vGS. Como, pela definição (66) iD=svGS,

o ganho em tensão é dado por:

Av = − sR D

É fácil ver que o ganho em tensão é máximo quando VGS=0. Se

tomamos o caso do n-FET:

(

V

s = ∂∂VIGSD = 2 IVDSS

1 + VGST

T

)

No n-FET temos -VT!VGS"0, donde o valor máximo de s e

consequentemente de Av é obtido quando VGS=0.

A impedância de entrada é dada pela combinação de RG em paralelo

com a resistência de entrada do FET. Como esta última é praticamente infinita

porque a corrente de entrada é nula, temos Zin=RG. A impedância de entrada

deve ser fixada externamente pelo resistor RG. Caso contrário o potencial no

terminal de entrada estará flutuando. Tipicamente utilizam-se para RG

resistores de valor elevado ( > Mega-Ω).

Para a impedância de saída vale a mesma análise feita para o emissor

comum. Ou seja, Zs é dada por RD ou por RD|| ρ.

Para os FETs não faz muito sentido definir o ganho em corrente, já que

o sinal de entrada é sempre uma variação de tensão que excita o campo

elétrico a que está sujeita a junção. Por outro lado vimos que a corrente de

entrada é nula, o que indicaria ganho infinito em corrente, embora saibamos

que a corrente de saída é finita e definida pela condutividade do canal.

Um FET pode também ser operado em modo dreno comum, que seria o

equivalente ao modo coletor comum dos bipolares, como mostramos na Fig.

56.

VDD

ve

Vs

RG

RS

Fig. 56: FET em modo dreno comum

A mesma corrente passa por dreno e por source. Portanto:

v s = RS i S = RS i D = RS sv GS = sRs (v G − v S )

Como vG=ve, podemos escrever:

Av = 1+ sRS S

sR

Encontramos então, Av"1, como no caso do modo coletor comum. Mas

sRS é tipicamente menor do que o fator (#+1)RE que aparece para o transistor

bipolar, donde se conclui que a atenuação é maiot no caso do FET.

A impedância de entrada é dada por RG, devido a que a corrente de

entrada no FET é nula. Para encontrar a impedância de saída podemos

retomar a expressão para o ganho:

Av =

vs

ve

= 1+ sRS S ⇒ v s =

sR

RS

1

+ RS

s

ve

Aí vemos que vS resulta de uma divisão de tensão entre os resistores RS

e 1/s, e podemos identificar que a impedância de saída é dada por Zs=1/s,

como fizemos no caso do coletor comum.