3. Unidade Central de Processamento

Um microprocessador é um chip responsável por buscar e executar instruções e

dados existentes na memória RAM. Vai de regra as instruções são bastante simples,

como por exemplo operações aritméticas, lógicas, comparações, leituras e gravações na

memória. Um programa corresponde a um conjunto de instruções que vai ser executado

pela CPU.

O ciclo de funcionamento de uma CPU consiste em:

1. Buscar na memória a próxima instrução a ser executada; corresponde a etapa de

leitura;

2. Interpretar a instrução a ser executada; é a etapa de decodificação;

3. Buscar na memória os dados associados a instrução;

4. Execução da instrução, operando sobre os dados;

5. Armazenar o resultado da execução na memória (se for o caso);

6. Reiniciar o processo, na etapa 1.

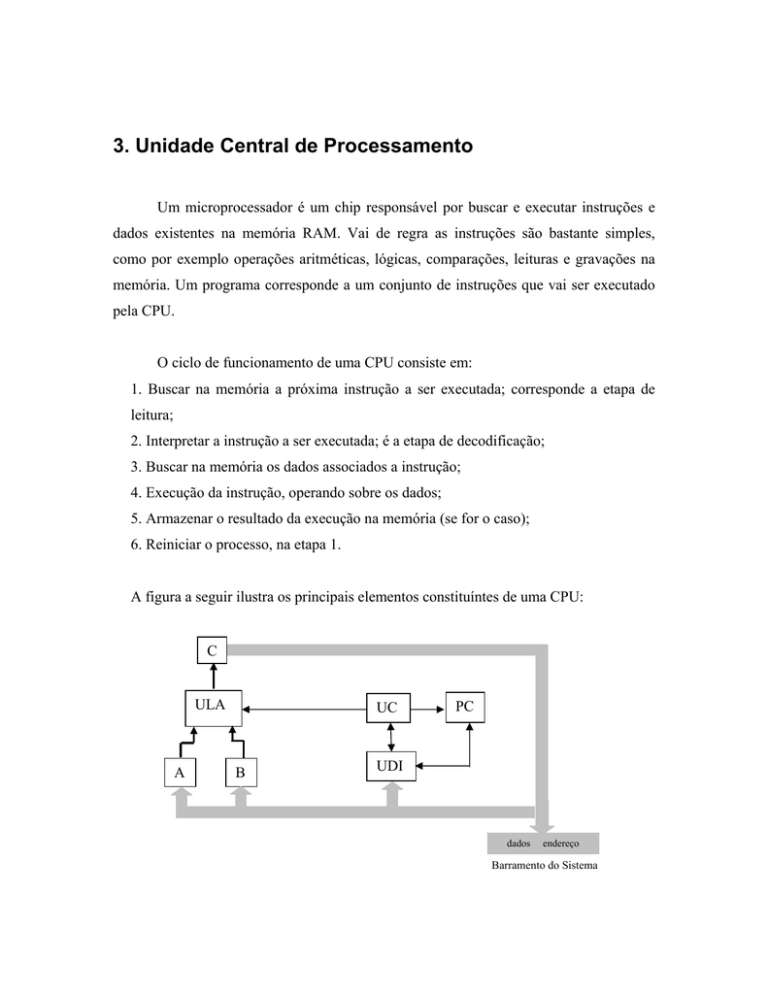

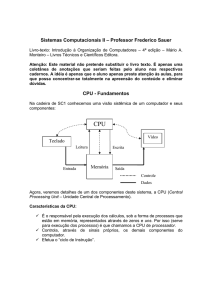

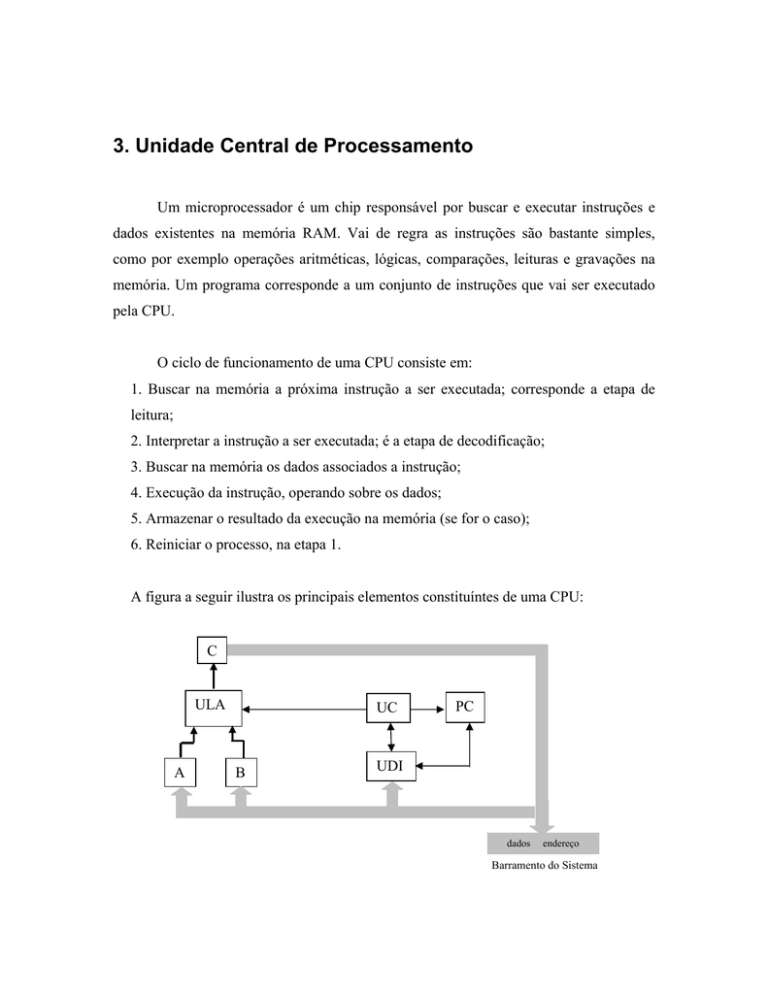

A figura a seguir ilustra os principais elementos constituíntes de uma CPU:

C

ULA

A

UC

B

PC

UDI

dados

endereço

Barramento do Sistema

Unidade Lógica e Aritmética (ULA): Responsável pela realização

das instruções

matemáticas e de comparação;

Registradores: Utilizados para o armazenamento temporário de dados; no diagrama

aparecem os registradores A, B, C e PC (que é o Program Counter, registrador que

armazena o endereço da próxima instrução a ser executada);

Unidade de Controle (UC): É

responsável pela busca de instruções na memória

controlando também a ULA e o Decodificar de Instruções

Clock: gera pulsos (na forma de uma onde quadrada); a frequência com a qual o clock

gera estes pulsos é medida em Hertz (um Hertz equivale a um ciclo por segundo). A CPU

realiza suas operações no ritmo ditado pelo seu clock; atualmente as CPUs operam com

frequências na ordem de Gigahertz.

Um microprocessador da empresa AMD

Tecnologia CISC/RISC

Todo microprocessador é capaz de decodificar um certo número de instruções

(que é chamado de seu Instruction Set). Quando uma instrução é decodificada pela CPU,

ela executa uma sequência de microcódigo referente a esta instrução. Com a evolução

das CPUs o conjunto de instrução aumentou de tamanho e microprocessadores com um

conjunto grande de instruções é denominada CISC. Quanto maior o conjunto de

instruções, menor o desempenho do microprocessador pois a decodfificação de uma

determinada instrução e a sua execução irá demorar um tempo maior. Mas apesar de

existir um conjunto de instruções grande, nota-se que geralmente somente algo em torno

de 30% das instruções são efetivamente empregadas pelos programas.

A partir desta constatação foi desenvolvida uma geração de CPUs com um

conjunto reduzido de instruções, com uma consequente otimização do decodificador de

instruções e também do microcódigo. Microprocessadores desenvolvidos desta forma são

classificados como RISC (Reduced Instruction Set Computing).

Algumas técnicas desenvolvidas a partir da família Pentium

Previsão de desvio

Empregada pela CPU quando existe uma condição do tipo “se A>B, vá para

<endereço>”. O controlador de memória carrega para a cache todos os resultados

possíveis ao invés de aguardar o núcleo do microprocessador acabar o processamento

para saber qual o desvio a ser tomado.

Arquitetura superescalar

A arquitetura superescalar esta associada a estrutura do processador. Um único

processador funciona internamente como se existisse vários processadores convencionais,

permitindo realizar várias instruções ao mesmo tempo.

Quando um processador com arquitetura superescalar possui dupla canalização,

isto significa que pode realizar duas instruções simultaneamente.

Multiprocessamento

Quando um microprocessador consegue operar em uma placa-mãe com mais de

um processador simultaneamente. Isto depende do tipo da placa-mãe (que deverá suportar

mais de um processador), do chipset e também dos processadores, que deverão ser

compatíveis.

Tecnologias MMX, 3DNow e SSE

Conjunto de instruções que consegue manipular vários dados simultaneamente. É

um exemplo da aplicação da técnica SIMD (Single Instruction on Multiple Data). O

conjunto de instruções MMX tem 57 instruções, e evoluiu com o tempo para tecnologias

como SSE e SSE2.

Um pouco da evolução da Família Intel x86