UNIVERSIDADE FEDERAL DE SANTA CATARINA

PÓS-GRADUAÇÃO EM ENGENIIARLAELÉTRICA

APLICAÇÕES DE REDE Mos DIvIsORA DE CORRENTE EM

CIRCUITOS INTEGRADOS ANALÓGICOS PROGRAMÁVEIS

DISSERTAÇÃO SUEMETIDA

À UNIVERSIDADE FEDERAL DE SANTA CATARINA

PARA A OBTENÇÃO DO GRAU DE MESTRE

EM ENGENHARIA ELÉTRICA

RICARDO TAKASE GONÇALVES

'

FLOR1ANÓPOLIs,DEzEMERO DE

1994

ll

APLICAÇÕES DE REDE Mos DIvIsoRA DE CORRENTE EM cIRcUITos

INTEGRADOS ANALÓGIcos PROGRAMÁVEIS

~

CANDIDATO: RICARDO TAKASE GONÇALVES

Esta dissertação

foi

MESTRE EM ENGENIMIÃ.

julgada para obtenção do título de

ESPECIALIDADE ENGENHARIA ELÉTRICA e aprovada em sua fonna final pelo Curso de

Pós Graduação.

Prof.

MÁRcIo cHIêfr(EM sc

IDER, Dr.

\

ORIENTADOR

Prof

C/Q V QQ X

CARLOS

z..

'

CO-ORIENT

if ¶

Q

M0

I

ORO,

Dr.

O

R

`\

I

P

Prr›f.›‹

E

ovAI..MoRlKAss

A

cooRDENADoRDoc

so DE Pos-GRADUA -s M_

Pri. Adroaldo Raizer, U .

Íllinfiønldlldør do Curso de P. G. Eng'

-

K,

â

GENHARIA

ETRICA

Eléttlt'-I

BANCA ExA1vIINADoRAz/¿/

Prof.

MÁRCIO

Prof.

CÍÃÍ Qàx

CARLOS GALUP MONT

Prof.

P!'0f.

cÉm~mEE

Dr.

4

SIDNEI NocET11=IL1fIo,

O, Dr.

D.sz.

ANTONIÓ CARLQS MÔREIRAO DE QUEIROZ, D.SC.

À minha adorável esposa

e ao nosso futuro bebê.

IV

AGRADECIMENTOS

Agradeço os professores do LINSE '(Laboratório de Instrumentação Eletrônica) da

UFSC. Especialmente aos meus

orientadores Márcio

Cherem Schneider

e Carlos Galup Montoro,

pelo imenso apoio para a realização deste trabalho.

Agradeço também a todos os colegas do laboratório que me incentivaram durante

periodo,

em

especial a

Ana Isabela Araújo Cunha pelo

este

inestimável apoio científico e a Elton Luiz

Fontão por sua grande ajuda na edição do trabalho.

Agradeço aos meus

pais Silvio e Lúcia pelo incentivo e pelo carinho.

Agradeço de

maneira muito especial à minha esposa Selma por todo seu apoio, compreensão e dedicação

durante todos estes anos de convivência.

sUMÁR1o

Sumário

'

....................................................................................................................

..

Lista de figuras ..........................................................................................................

..

Lista de tabelas

.........................................................................................................

..

Resumo .....................................................................................................................

..

Abstract ....................................................................................................................

._

Introdução .............................................................................................. ..

Capítulo

I -

Capítulo

II -

Capítulo

O Divisor de Corrente MOS

..................................................................

2.1

-

Introdução.

2.2

-

Característica estática

2.3

-

Associação de transistores ..............................................................

..

....................................................................................

do transistor MOS .......................................

Associação

em série ............................................................

..

2.3.2

-

Associação

em paralelo .......................................................

..

-

A rede "ladder" T-2T

2.5

-

Não

2.6

-

.....................................................................

..

idealidades da rede proposta ...................................................

..

Propriedades da rede proposta .......................................................

..

Aplicação da Rede Divisora de Corrente

em um Amplificador de Ganho

Capitulo

..

3.1

-Introdução

3.2

-

O amplificador de Ganho Programável ...........................................

3.3

-

Implementação de um protótipo discreto - resultados experimentais.

3.4

-

O Amplificador Programável atuando como conversor D/A

3.5

-

.....................................................................................

...........

3.4.1

-

Introdução

3.4.2

-

Conversor digital-analógico ................................................

.........................................................................

~

..

..

..

..

_.

Uma Nova Metodologia

..

SI Progrmáveis

-

..................................

13

..

Conclusao ......................................................................................

IV - Filtros

3

..

-

Programável ..............................................................................................................

-

..

2.3.1

2.4

III -

.

..

20

-

4.1

4.2

4.3

~

Introduçao

O integrador em corrente chaveada

-

-

V

Bibliografia

-

.

..

............................

..

..

4.2.1

-

Circuitos de 1° geração ....................................

4.2.2

-

Circuitos de 2” geração ....................................

..

30

Uma nova metodologia de implementação de filtros SI

4.3.1

Capítulo

................................................................

`

-

Resultados experimentais ................................

Conclusoes

......................................................................

..

..

46

LISTA DE FIGURAS

Figura 2.1

-

Estrutura de

um transistor canal-n .................................................................

Figura 2.2

-

Transistores

MOS conectados em série

Figura 2.3

-

Características ID x

._

3

......................................................... ..

5

VD - transistor unitário,

associação série

e associação paralelo de dois transistores unitários

.......................................

..

6

Figura 2.4

-

Topologia da rede "ladder" R-2R ..................................................................

..

7

Figura 2.5

-

Rede

"ladder"

T-2T de 2 bits programável .....................................................

..

8

Figura 2.6

-

Rede

"ladder"

T-2T de 2-bits compensada para minimizar

os efeitos da saturação da velocidade dos portadores ..................................

Rede

"ladder"

T-2T de

Figura 2.7

-

Figura 3.1

-

Figura 3.2

-

(a) rede divisora

Figura 3.3

-

Características estáticas das redes

Figura 3.4

-

V0 x V¡ do amplificador programável. Ganhos

Figura 3.5

-

Distorção harmônica total

Figura 3.6

-

Função de transferência

Figura 3.7

-

Conversor

1-bit12

....................................................................

de corrente e

-

(b) seu símbolo ...........................................

rede

ideal

de

e B.

ot

VG = 2,5

-

com ganho de

V e VB = -2,5 V

1/4, 1/2, 1, 2, 3

1/4, 1,

D/A de 4 bits - (a) rede de escalamento

..

12

..

14

..

17

e 4 ............. .. 17

4 e rede linear

.........

..

18

..

21

da corrente

conversor linear V-I da entrada e (c) conversor linear I-V da saída ........ .. 22

do protótipo discreto de 4

-

Característica estática

Figura 3.9

-

Leiautes da rede de escalamento implementadas no

(a)

.............

um conversor D/A de 3 bits .......................

Figura 3.8

-

10

Amplificador de ganho programável ........................................................... .. 13

(b)

Figura 4.1

..

SoG

e (b) "full-custom"

Espelho de corrente

e (c) proposto modificado

bits

..................................

-

(a) convencional, (b)

não sobrepostos

-

Sinais de "clock"

Figura 4.3

-

Circuito de atraso (la geração)

Figura 4.4

-

Integrador SI universal de

Figura 4.5

-

espelho de corrente chaveado (2“ geração)

1”

-

...............................................................

(a)

geração

..25

proposto

..............................................................................................

Figura 4.2

24

PMU 9

.......................................................................

(la geração)

..

..

..

28

30

convencional e (b) proposto ............... .. 30

-

(a)

convencional e (b) proposto ..... .. 31

..................................................

..

32

vii

(a) convencional e (b)

Figura 4.6

-

Circuito de atraso (2“ geração)

Figura 4.7

-

Integrador sem perdas (23 geração)

Figura 4.8

-

Integrador de 2” geração

(a)

Figura 4.9

-

-

-

(a)

convencional e (b) proposto ........ .. 36

com amortecimento

-

convencional e (b) proposto ................................................................... .. 38

Integradores programáveis da nova metodologia

(a) 1°

-

geração e (b) 2” geração ..................................................................... .. 40

Figura 4.10

-

Circuito gerador de 2 fases de "clock" não sobrepostas

Figura 4.11

-

Resposta

Figura 4.12

-

Resposta

Figura 4.13

-

proposto ............... .. 35

em freqüência do protótipo

discreto

-

B

.............................

= 7/8,

3/4 e 1/2

em freqüência do protótipo discreto teórica e experimental ([3 = 7/8) ................ ....................................

..

Curvas da corrente de saída do integrador para

freqüência do sinal de entrada de: (a) 300 Hz, (b) 3,6

KHz e (c) 8250 KHz

..........

._

..

41

LISTA DE TABELAS

Tabela 3.1

-

Ganhos

Tabela 3.2

-

Valores dos componentes do amplificador de ganho programável,

possíveis

para medida da

do amplificador programável

THD

..........................

...............................................................

..

._

X

RESUMO

Neste trabalho são apresentadas algumas aplicações de

uma

rede

MOS

divisora de corrente, baseada na clássica rede "ladder" R-2R. Sua programabilidade

digital é obtida

com

a utilização de transistores. Esta técnica apresenta

principal característica a total compatibilidade

com

a tecnologia

CMOS

como

digital e

com as técnicas de implementação em "sea-of-transistors".

Um conversores D/A e um amplificador de ganho programável são mostrados

como exemplos de utilização

desta técnica.

Finalmente, apresentamos

corrente chaveada.

A

uma metodologia inédita para realização de filtros

utilização

da rede divisora de corrente nestes circuitos

proporciona a implementação de filtros que

digitalmente.

_

a

podem

ser facilmente

programados

xi

ABSTRACT

We present in this work some applications of an MOS transistor-only current

divider based

network

is

on the

classical

R-2R

ladder network. Digital programmability of the

attained through the use of transistors only. This technique presents total

compatibility

with

digital

CMOS

technology and, particularly, with sea-of-

transistors.

A D/A converter and a programmable

_

amplifier have been designed through

the use of this technique.

We propose a new circuit technique to implement switched current filters (SI).

The use of transistor-only

SI filters.

current dividers provides digital programmability for these

»

1

CAPÍTULO 1 - INTRODUÇÃO

O processamento

com O advento da

de

sinais utilizando técnicas digitais sofreu

microeletrônica.

A

facilidade

microeletrônica

[l].

Por outro

digitais

têm

grande desenvolvimento

de projeto proporcionada por métodos quase

totalmente automatizados diminui consideravelmente O tempo

produto no mercado. Circuitos

um

em que

é possível lançar

muito utilizados pela indústria de

sido, então,

lado, todos os sistemas digitais necessitam de

algum tipo de fiinção

realizada por circuitos analógicos, principalmente para realizar o interfaceamento

extemos ao

digitais e evoluiu

tem provado

de transistores

ser a mais

adequada para a implementação de

circuitos

muito nos últimos anos. Circuitos VLSI ("Very Large Scale Integration") têm se

tomado cada vez mais complexos

em um único

ordem de grandeza

"chip".

com dispositivos

"chip".

A tecnologia MOS

do

um

até O

e mais densos, a ponto de serem integrados dezenas de milhões

circuito integrado. Espera-se

ano 2000

[1]. Isto

que este número cresça pelo menos

uma

é devido à redução das dimensões dos componentes

Atualmente são possíveis linhas de interligação

com

largura de 0,5

um e alimentação

V e SV. A partir de 1995 esta dimensão estará em tomo de 0,35 um e a tensão de

alimentação em 3,3 V [2].

A evolução dos processos VLSI tem pennitido a implementação de sistemas completos

mista de 3,3

("mixed analog-digital systems")

aplicação

em um

único "chip". Conseqüentemente, novos campos de

têm surgido, como por exemplo, equipamentos

computadores "notebook" e "palmtop", entre outros

portáteis de áudio e vídeo,

modems,

fax,

[3].

Cinqüenta por cento do mercado de circuitos

VLSI de

aplicação especifica

("ASIC

-

Aplication Specifc Integrated Circuits") são implementados por técnicas denominadas "gate-array"

e "sea-of-gates"

(SOG)

[4].

Isto se

deve principalmente pelo reduzido tempo de projeto e

fabricação e pelo baixo custo proporcionado por estas técnicas.

Projetistas de circuitos analógicos

vêm procurando

apresentem resultados satisfatórios para implementação

em

obter altemativas de projeto que

processos digitais convencionais

e,

2

principalmente, que sejam realizáveis em' técnicas de SoG. Isto, porque a implementação de

circuitos mistos analógico-digitais

aumenta a confiabilidade do sistema e seu

técnicas de implementação de circuitos analógicos

em

custo.

Algumas

processos essencialmente digitais têm sido

reportados na literatura [4-11].

Muitas técnicas de implementação de

adaptam a tecnologia

digital

digitais e

uma rede divisora de corrente que

também pode

ser realizada

proposta é baseada na rede "ladder"

R-2R

capítulo II é apresentada

uma

realiza

digital-analógico.

Os

O

não se

circuitos são:

capítulo

um

A

estrutura

daremos o nome de rede T-2T.

É

uma divisão linear da corrente de entrada.

da rede T-2T.

análise teórica

apresentamos algumas possibilidades de aplicação deste

programabilidade.

dia

é totalmente compatível

com técnicas de SoG.

[17] e a ela

implementada somente com transistores MOS e

No

em

MOS, ou demandam grande área de silício para sua implementação.

Neste trabalho apresentaremos

com processos

circuitos analógicos utilizados hoje

circuito,

No

capítulo III

que tem como caracteristica a

amplificador de ganho programável e

um

conversor

IV apresenta uma nova metodologia de implementação de

filtros

programáveis que utilizam a técnica de corrente chaveada,l onde a programabilidade é obtida

através da utilização da rede T-2T.

No capítulo V são apresentadas as conclusões.

I

3

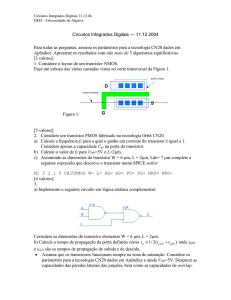

CAPÍTULO II - O DIVISOR DE CORRENTE MOS

2.1

INTRODUÇÃO

-

Técnicas lineares e precisas de divisão de corrente (ou tensão) são utilizadas

tipos de circuitos analógicos. Neste capítulo apresentaremos

linear

da corrente de entrada. Nela são utilizados somente

uma

rede que realiza

transistores

MOS

em

diversos

uma

divisão

e sua precisão

depende principalmente do casamento entre os componentes.

2.2

-

CARACTERÍSTICA ESTÁTICA DO TRANSISTOR MOS

Um transistor MOS retangular apresenta simetria entre fonte e dreno, que fica evidenciada

no equacionamento de suas

local (figura 2.1).

características

quando suas tensões são referenciadas ao substrato

A corrente de dreno pode ser expressa genericamente na forma [12,

1D=-`š[g<vG,vs›-g<vG,vD›1

onde

W e L representam a largura e o comprimento do

fimção que descreve o comportamento

VD

V

V-

|

P+

|

‹z.1›

canal, respectivamente, e

DC do transistor MOS.

B

D

G

S

N+

N+

P

Figura 2.1

-

Estrutura de

um transistor MOS

13, 14]

canal-n

g(VG,V) é uma

4

2.3

-

2.3.1

~

ASSOCIAÇAO DE TRANSISTORES

-

Associação

Na

substrato

em sén`e:

_

ç

figura 2.2 temos dois transistores conectados em

série,

com

comuns a ambos.

as tensões de porta e

_

t

As

correntes de dreno dos transistores¬TD e TS, para

uma dada

tensão de dreno (VD) que

garanta o funcionamento na região triodo, são expressas por

IDD

:

[g(Vc,Vx)"g(VG,VD)]

(2-2)

IDS

=

[g(VG ,Vs) _ g(VG,Vx)]

(2-3)

S

sendo todas as tensões referenciadas ao substrato

local.

Na ligação em série as correntes dos dois transistores são idênticas. Fazendo,

IDD

então,

= IDS

(24)

obtemos

g(VG,VX)i

A

HY

t

t

~

g(V pra V

sg(v(!;/iJ:L{(_)

Háfiã

4

)__

(25)

L

corrente de dreno desta associação de transistores pode ser obtida através das

expressões (2.2) ou (2.3) e

(2.5), resultando

ID

=

em,

[g‹vG,vS›-g‹vG,vD›1

‹2.õ›

ç

5

Jim

Í*

onde

lV_2V_

W

L

L

lrwll

D

Considerando o caso particular

em que

os transistores são idênticos (transistores

unitários),

tâflszeltzelt

~

a razão de aspecto dada pela expressão (2.7) da associação

em

série

de dois transistores unitários

resulta

elrzâia

A

associação

em

série

de dois

transistores unitários é equivalente a

um

possui o dobro do comprimento do canal de

um

transistor unitário. Portanto,

composto conduz uma corrente de dreno que é a metade da corrente de dreno de

unitário polarizado sob as

mesmas

condições.

D

ID

SZSL

*°X

G

TS

B

ML

(L)S

O

S

Figura 2.2

-

Transistores

transistor

MOS conectados em série

que

o transistor

um

transistor

6

2.3.2

-

Associação

em paralelo:

Na associação em

paralelo de dois transistores unitários é simples verificar

que a corrente

de dreno neste transistor equivalente corresponde ao dobro da corrente de dreno de

unitárioe

também pode

ser expressa por (2.6),

um transistor

onde

size),

A associação em paralelo de dois transistores unitários é equivalente a um transistor com o

dobro da largura do canal de um transistor

ID

unitário.

(uh)

~.)__,

300.0

À

.az

_.

*___

2

›--4

,.Ê_

"

_.--_L

.

...

__

_,

paralelo;

_

s__`l

30.00]

/diví

__.,

¬.,.._

4-.....

~

ç

V

¬._.

¿

1

__

í

.,//'í/"71

l

1

'

i

//8

'

1

1

z

iséñel

`

É

__

'à

l

3

__-

/')

l

I

IDR' ".

i

.zsoo/div

vn

-

Características ID

x VD

-

I

Z

_,

-

Figura 2.3

.;

l

il..

.ouso

.oooo

uriitáriol

l

<

l

v>

2.500

l

transistor unitário, associação série

e associação paralelo de dois transistores unitários.

Na

associação

figura 2.3 são apresentadas as

em

série e

da associação

em

características

de saída do transistor

paralelo de dois destes transistores.

Além

unitário,

da

disto, nesta

figura também foram traçadas mais duas curvas, uma correspondendo ao dobro da corrente do

transistor unitário e a outra à metade. Nota-se que na região triodo as características dos

7

transistores

compostos são praticamente

unitário (Tu).

Segundo a teoria, a corrente de dreno que flui em qualquer

sua razão de aspecto; portanto, transistores

polarização apresentam

mesma

característica

com mesma

2.4

-

transistor é escalada por

razão de aspecto e sob

DC na região triodo.

obtidas através do analisador de parâmetros de semicondutores

canal-n do

da característica do transistor

idênticas às curvas obtidas

I-IP

As curvas da figura

4145 B, utilizando

2.3

mesma

foram

transistores

PMU 7, com Wu = 3 um e Lu = 1,2 pm, para uma tensão de porta VG = 5 V.

A REDE "LADDER" T-2T

Como vimos

de resistores lineares

até agora, a associação de transistores obedece a

[15].

Podemos

tirar

mesma

regra da associação

proveito desta característica para implementar

divisora de corrente baseada na já conhecida rede "ladder"

R-2R

[l6], a qual

uma

rede

denominaremos rede

"ladder" T-2T.

.L

.L

A

v‹›-I>-1:1--H:i-›-z--1:»-i›i:1-í

.L v

LV

1v

.L

.L

2n_,v

Znv

I

n

2

n-1

2 2

22

1

22

2

2..

IIIÉÍI

III

IIII

ÍIIÍ

III

47

Figura 2.4 - Topologia da rede "ladder" R-2R.

A

figura 2.4

representa a topologia da rede R-2R,

representados por blocos, que

podem

por ser composta por resistores

quanto da corrente.

ser resistores

lineares,

onde os componentes estão

(R-2R) ou transistores (T-2T).

A rede R-ZIL

proporciona divisão binária sucessiva tanto da tensão

8

Na

figura 2.4 cada bloco pode

mesma tensão de porta e

substratos conectados, constituindo

a figura, vemos que ao nó

injetada neste

unitário.

implementado com transistores unitários

ser

uma rede

MOS, com

a

"ladder" T-2T. Analisando

estão conectados dois ramos idênticos; portanto, a corrente que é

1

nó é dividida por

dois. Estes dois

ramos em paralelo equivalem a

Conseqüentemente, no nó 2 a corrente injetada também é dividida por

linearidade da característica ID x

VD dos

MOS,

transistores

2.

um

transistor

Apesar da não

a cada nó a corrente é dividida

linearmente, de forma binária, e a precisão desta divisão depende principalmente do casamento dos

transistores

como elementos da rede

simultaneamente

"ladder"

palavra

Esta rede apresenta a vantagem

[17].

T-2T de

2-bits,

divisora de corrente.

bit,

corrente de saída ("sum-line", terra virtual de

("dump-lme"). Assim, por exemplo, se bo

.

.

Vrefo-.D

l__i,_l

Iref VB

MOS

chaves'

Na figura 2.5

é mostrada

uma rede

a corrente é direcionada para o ponto de

um

= bl =

1,

soma da

amplificador operacional) ou para o nó de terra

a corrente de saida e

,

,

%

,C

3

+ -If = Zlmf.

_¶_

lTl

T1

VB

VB

.

VB

_

VB

i_o\É

bgilšç

Pvc

.

OH I_°\É

V.zz›;||¬zv<z

.

=

[>

"Dump-line"

"Sum-line"Q

Figura 2.5 - Rede "ladder" T-2T de 2

Em uma

participarem

o<

o<

_?_

as

onde é salientada a programabilidade da corrente de saída através de uma

Dependendoido valor do

digital.

de

implementação integrada

(É) é obtida através de inversores

em

tecnologia

CMOS

bits

programável.

CMOS,

a palavra digital complementar

e seus níveis alto e baixo são

VDD

e VSS,

respectivamente. Portanto, por simplicidade, e por permitir melhor precisão na divisão da

9

corrente[19], a tensão de controle das portas (VC) dos transistores

NMOS da rede deve ser VDD

.

No caso de uma implementação com transistores PMOS a tensão Vc deve ser Vss.

Par qualquer tensão de entrada menor ou igual a VDD, os transistores à

(figura 2.4)

2.5

-

operam na região triodo

do nó

direita

"n"

[l4].

NAO IDEALIDADES DA REDE PROPOSTA

O

equação

(2.1).

Porém, na

de transistores

prática, esta rede

está baseado na validade da

MOS

apresenta descasamento entre

de segunda ordem que interferem na divisão de corrente

transistores, ruído e alguns efeitos

Outra fonte de erro (extema) importante é a existência de

line" e

T-2T

princípio da divisão precisa de corrente na rede

uma

tensão de "offset" entre a "sum-

a "dump-line".

Ao

se polarizar a rede na região triodo, alguns efeitos de segunda

apreciáveis caso os transistores

operem na região de saturação,

shortening", "drain induced barrier lowering"e

"weak avalanche"

tais

[17],

ordem que

como

podem

se

portadores, efeito este que não é levado

linearidade da divisão

da corrente.

nos transistores sujeitos a

O

em consideração

efeito

tornam

"channel-lenght

ser desprezados.

Dentre os efeitos de segunda ordem o mais importante é a velocidade de saturação

critico

[18].

(vd)

dos

na equação (2.1) e que tem influência na

da saturação da velocidade dos portadores é mais

uma maior tensão

VDS, isto

é,

aqueles onde o nível de corrente é

maior.

Um método

responsável pelo

2°

bit

bit

simples e eficaz de reduzir este erro [18] é fazendo a substituição do

mais significativo

mais significativo.

Na

(MSB) por uma

figura 2.6 é mostrada

vemos que os transistores do ramo responsável

pelo

rede equivalente ao ramo responsável pelo

como exemplo uma rede de

dois

bits,

onde

MSB estão sujeitos à mesma queda de tensão

dos transistores do restante da rede.

Na

(idealmente) são representados pela

mesma numeração.

figura, os

ramo

nós que apresentam o

mesmo

valor de tensão

Fica claro que o ramo responsável pelo

MSB está agora sujeito às mesmas não idealidades do restante da rede.

10

o<

o<

__?_.

Fl-_'

Vrefo

_?_

IT]

1

2

VB

VB

VB

VB

|-«vz

-

2

vB

|-«vz

Val*

V”

<=

”B°Êll°“@

I-'if

”a|í22l

V

-3

3

i

El |-°

1:

f\

D

"Dump-line"

"Sum-line"

Figura 2.6 - Rede "ladder" T-2T de 2-bits compensada para minimizar

os efeitos da saturação da velocidade dos portadores.

Este procedimento, se repetido para os demais

perde-se

uma

número de

do

bits,

aumenta a precisão da rede; porém,

das maiores vantagens desta técnica, que é a grande economia de área, pois o

transistores desta rede

compensada

cresceria exponencialmente

com o número

de

bits

circuito.

O descasamento entre os transistores representa uma fonte de erro que afeta a precisão da

rede e pode ser caracterizado pelos desvios da tensão de limiar (AVT) e da transcondutância (AB)

[19].

Algumas precauções podem

ser

descasamento dos componentes da rede

tomadas para minimizar os erros causados pelo

[20],

formato e dimensões, fazer uso de técnicas de

por gradientes no substrato

como por exemplo:

leiaute

silício,

entre outros.

-

componentes de mesmo

que permitam minimizar os

(leiautes simétricos, centróide

dos componentes sempre na mesma direção, para se

utilizar

efeitos causados

comum), manter o fluxo de corrente

evitar efeitos

de anisotropia do substrato de

ll

O ruído térmico

efeitos

é considerado predominante dentre os vários tipos de ruído,

não limitam o desempenho da rede divisora de corrente

A

porém seus

[l8].

rede T-2T apresenta a característica de que sua programabilidade não altera sua

impedância. Para que esta característica seja mantida é necessário que a "sum-line" e a "dumpline"

um

de

si.

possuam a mesma

tensão. Isto é normalmente obtido através da alta impedância de entrada

uma tensão de

Entretanto, sempre existirá

ser

mesma tensão, porém

amplificador operacional, que garante dois pontos de

uma grande

da tensão de

"ofl`set" entre as

duas entradas do

ampop

e esta

pode

fonte de erro presente neste tipo de implementação. Considerando apenas o efeito

"offset" (Inf

=

O),

a rede se comporta

como um

transistor

conectado à "sum-line" e cuja fonte está conectada à "dump-line".

exemplo uma rede de apenas

1-bit.

Quando o

bit bo

=

1,

quatro transistores

em série. Note que,

se bo

=

0,

composto cujo dreno

Na figura 2.7

é mostrada

está

como

são habilitados os transistores ligados à

"sum-line" e desabilitados os ligados à "dump-line" e tem-se

Como

isolados entre

um transistor composto

não há corrente de

formado por

"ofl`set".

a tensão de "ofi`set" é muito pequena, este transistor opera na região triodo e a

corrente de "offset" é dada por [14]

Ion'

onde VP = (VG-VT0)/n

= ID =

%[(VP ' VsB)2 -(VP _ VDB)2j

é atensão de "pinch-off'

do

transistor e n

(211)

o

fator de inclinação

[13] e

[3=uC'o×W/L. Fazendo V°f,= VDB-VSB, temos

z ll Cox

.

Iofr

W

[Vo _ VB _ Vro

eq.

A corrente de

bits,

tem-se

uma

"oñ`set" é

dependente da palavra

'l'

U VB] Voir

digital, pois,

(212)

conforme a combinação dos

razão de aspecto diferente para o transistor composto resultante.

corrente de "offset" ocorre para

a corrente de entrada da rede,

um

código alternado de O-1 da palavra

menor será o

digital [l8].

A

maior

Quanto maior

erro relativo devido à corrente de "offset".

12

ID = 10 ff

bo

"Sum-line"

4

0<

_í_

]l°~<

f_`|

_

o

HE

Iref

“Ml

"Dump-line"

Figura 2.7 - Rede "ladder" T-2T de

2.6

-

l-bit

PROPRIEDADES DA REDE PROPOSTA

Apesar de ser

uma

rede que permite programação da corrente de saida, a impedância de

entrada da estrutura permanece constante

Pelo fato de

e,

portanto, independente

do código da palavra digital.

MOS idênticos, a técnica de divisão de corrente

em tecnologia CMOS digital e também pode se

somente transistores

utilizar

apresentada é adequada para implementação

como a implementação em

beneficiar de algumas de suas potencialidades

"sea-of-gates" (SoG).

Para proporcionar programabilidade à rede "ladder" T-2T é necessária a utilização de

chaves para controlar o caminho da corrente.

Uma das grandes virtudes desta rede reside no fato

de que os próprios transistores que atuam como chaves, atuam também como elementos de

escalamento.

'

»

r

Outra característica importante desta

técnica,

de transistores da rede é proporcional ao número de

em

circuitos

que é inerente à rede R-2R, é que o número

bits (n°

de transistores = 4 n+2). Isto resulta

que ocupam pouca área quando comparadas comoutras redes de escalamento, onde

geralmente o número de componentes cresce exponencialmente

com o número de bits.

'

13

CAPÍTULO III - APLICAÇÃO DA REDE DIVISORA DE CORRENTE EM

UM AMPLIFICADOR DE GANHO PROGRAMÁVEL

3.1

-

INTRODUÇÃO

Neste capítulo serão apresentados

um amplificador de ganho

programável e

um

conversor

digital-analógico nos quais as redes divisoras de corrente são responsáveis pela programabilidade.

Protótipos discretos foram implementados e seus resultados são mostrados para validação da

metodologia de implementação.

3.2

-

O AMPLIFICADOR DE GANHO PROGRAMÁVEL

Um amplificador de ganho programável é facilmente obtido com a utilização da rede T-2T.

Na

figura

lineares

3.1 é

mostrado seu esquema

elétrico,

com

na entrada e saida e duas redes T-2T idênticas

,

amplificadores operacionais, resistores

com fatores de atenuação

ot

e B.

al,

_

R

-

+

v,

_f_

<

Iz

›

›

1-

1

>

-

+

Y°

-

Amplificador de ganho programável

rede divisora de corrente é apresentada na figura 3.2 (a) e sua representação

diagrama de blocos na figura 3.2

estrutura,

É

Blz

=

Figura 3.1

A

|z

Il

uma é complementar da

(b).

outra.

em

Nestas figuras ficam evidenciadas as duas saídas da

A corrente de saída,

representa

uma

fração da corrente

14

uma

de entrada e é controlada por

nó inversor de

ao

terra.

um

palavra digital (bo-›bm,). Esta fração de corrente é

amplificador operacional na

saída,

somada no

enquanto seu complemento é descarregado

Através da variação das dimensões geométricas dos transistores da rede é possível obter

diferentes escalamentos da corrente de entrada.

_L

1

°-D

I"

OH

“ga

w<

Tr

¡¡,<

O<

lagar

o

"sum-line' A

É

O<

°<

'

i

.

z,‹

_í`_

.ag

o<

w<

w<

n<

O<

bflzigâzzzzvigpc

¡§,.

l>

Dump-line"

3.2 (a)

I

Rede Divisora

_

b

.

de Corrente

( 1-

a) I

v

01 I

V

"Sum_¡¡ne"

"Dump-line"

3.2 (b)

Figura 3.2

Os resistores

conversão

linear

-

(a)

rede divisora de corrente e (b) seu símbolo

lineares juntamente

da tensão

com os amplificadores operacionais

são responsáveis pela

em corrente na entrada e da corrente em tensão na saída.

15

Considerando os ampops

ideais,

os resistores idênticos e as redes T-2T casadas entre

si,

obtemos

a.I¡:"%:>I¡:_~

Bizz-%=›1z=-ä

Como

as duas redes divisoras de corrente

De

correntes são idênticas.

(12)

possuem a mesma impedância de entrada suas

obtemos a função de transferência em tensão do

(3.1) e (3.2)

amplificador programável

h_E

-OL

(33)

Vi

onde

ot

e B representam frações da corrente de entrada e são programadas por palavras digitais.

número de

bits

programável.

O número

é o número de

3.3

_

das redes

ot

e B determinará a quantidade de ganhos possíveis

de níveis diferentes de corrente na saída

O

do amplificador

em cada rede é igual

a

2",

onde n

bits.

1M1>LEMENTAÇÃo DE UM PRoTÓT1Po D1scRETo -

RESULTADOS EXPERIMENTAIS

Foi montado

um

circuito amplificador

como na

figura 3.1,

com

transistores canal-n

do

PMU 7, de dimensões W = 3 um e L = 1,2 um. As portas foram polarizadas com VC = 2,5 V e os

substratos dos transistores

+5

e

com VB =

-SV para reduzir a influência da sua não

As

redes

ot

Os ampops

-2,5 V.

linearidade na

e B foram implementadas

divisão binária da corrente.

(741) foram alimentados por tensões de

com

medida da distorção harmônica.

transistores idênticos, realizando, então,

Cada rede tem programação de 2

bits,

uma

proporcionando 16

16

combinações possíveis para o ganho, que são mostradas na tabela

notamos que, apesar de a mesma apresentar 16

diferentes níveis

de

3.1.

Através desta tabela

transferência da entrada para

saida, apenas 11 niveis são distintos.

Como podemos

notar,

ot

e B apresentam valor

entrada é transferida para a saída.

combinações serão iguais a

Quando

K

DIGITAL

I

sem o primeiro

equivalentemente a

discreta e

3.1

um

O0

01

10

quando toda corrente de

1/4

1/2

3/4

-

I

l

1 1

1

I

l

1/4

-1

-1/2

-1/3

-1/4

01

1/2

-2

-1

-2/3

-1/2

10

3/4

-3

-3/2

-1

-3/4

ll

1

-4

-2

-4/3

-1

.

Ganhos possíveis do amplificador programável

foram traçadas as

transistor

1,

e B são iguais, o ganho é unitário e 2" das possíveis

I

oo

Na figura 3.3

igual a

1.

cÓD1Go

Tabela

ot

máximo

caracteristicas estáticas (ID

da entrada. Através desta

transistor unitário,

como

figura,

x VD) das redes

cx

e B de 2

bits,

notamos que a rede T-2T se comporta

na figura 2.3. Apesar de ser

sem o casamento proporcionado por uma versão

uma montagem

integrada, as características das duas

H

redes apresentam

um casamento razoável, principalmente na região triodo.

A figura 3.4

apresenta a característica de transferência (tensão de saída versus tensão de

entrada) do amplificador programável da figura

na

saída.

3.13

com

resistores lineares

de 15

kQ na entrada e

Neste gráfico são exibidas algumas das possibilidades de programação do

circuito: 1/4,

'

1/2, 1,

2, 3, e 4.

As

figuras 3.3 e 3.4

semicondutores

HP 4145 B.

foram obtidas com o

auxilio

do analisador de parâmetros de

-

17

II

(UA)

200.0,

.

_

l

V

O

;

i

l'

I

f

¡

\

_,_,,,\;:

_

›

'

'

1

,

t

z

I

i

i

¡

.

'

I

:

V

-

|

|

100.

oi

/div

Í

-

I

'

‹

.

=

i

!

f

.

I

z'

z

g

l

1

;

i,

Í

I

'

._

|

Q

l

f

Í

Í

Ê

»

1

.

`

_

---_

i

1

Í

V

a

_

:

z

'

i

_'

.

g

ê

Í

i

E

,

¡._L.__-

¡

-i-

_.gÊg_

`

vt

Figura 3.3

vo

C

5.

O

-

.

Características estáticas das redes

IL

Í

i

'

*

U.

1

§Ç¿_

DOO

SOU

-1..

harmônica

4.

auxílio

total

em

2 SOU

.l

V e VB = -2,5 V

VG = 2,5

~

-s

s

~

z

V

íÍ

i

:IX

_

VI

z

›

do analisador de espectros

L

=

.

im

U4

5

š

__,.,

O

.

3000/div

Figura 3.4 - V0 x Vi do amplificador programável. Ganhos

Com o

V)

.,+~'

4

íÁ'/L/'øi::ÉãÊ;,záÉšÉE;___¬_______d

'

¡

-5.

Õ

e B.

<

i

ll

1~,âfl›°â

ot

l

l

5000/div

V)

OOO

l

l

5

1.

500

- 1/4, 1/2,

1, 2,

3 e

4

HP 3588A foram obtidas as curvas da distorção

função da tensão de entrada da rede, para ganhos de corrente B/ot de

1/4, 1

e

Com o intuito de analisar o circuito sob os mesmos níveis de corrente para os diferentes ganhos,

os resistores de entrada e de saída foram variados. As configurações utilizadas têm seus valores

mostrados na tabela 3.2.

Rede

Rede

OL

Ri”

B

Ganho de Ganho de

ROUÍI

bo

bl

a

bo

bl

B

(ko)

1

1

1

o

o

U4

1o

O

O

l/4

O

O

l/4

o

o

1/4

1

1

1

Corrente Tensão

(ko)

|B/a|

|V0/V¡|

1o

U4

U4

40

10

1

1/4

4o

2,5

4

1/4

Tabela 3.2 - Valores dos componentes para medida da THD

THD (às)

-40

I

I

I

I

I

I

-42

-44

//

/

-46

/

//

_

/'

//

_,,.-"'

/

//

/

_

1

'

4

_.

__

________

-48

fu/

-50

.~""

/

/

/

r

-52

-54

-56

/

/

/"_,.T

.

linear

-58

-60

l

I

0

0.4

0.8

I

1.2

I

1.6

I

2.0

I

2.4

2.8

Vz›-z›

Figura 3.5 - Distorção harmônica total - rede com ganho de

A

com

4 e rede

linear

figura 3.5 mostra as curvas de distorção harmônica para os ganhos de corrente

mostrados na tabela

seja,

1/4, 1,

(V)

as redes

originada pelos

3.2.

Também foi

T-2T

ampops

obtida a curva de distorção harmônica para a rede linear, ou

substituídas por resistores lineares. Esta curva representa a distorçao

e pelo gerador de tensão senoidal. Para tensões de dreno pequenas os

19

transistores

operam em uma região

linear

da curva ID x VD. Por

curvas de distorção para tensões de entrada baixas.

isto,

ocorre coincidência entre as

À medida que a tensão de entrada aumenta, o

ponto de operação da rede caminha para regiões cada vez mais não

combinado com o aumento do descasamento das redes

circuito.

A medida

ordem tomamse

distorção do circuito amplificador.

um

Este efeito

no aumento da distorção do

que os pontos de operação das redes se aproximam da região de saturação

alguns efeitos de segunda

espera-se

resulta

lineares.

apreciáveis e contribuem

Em uma implementação

também para o aumento da

totalmente integrada deste circuito,

desempenho sensivelmente melhor do amplificador programável quanto à distorção

harmônica do que o obtido

em nossas medidas, uma vez que as redes ot e B

por nós utilizadas não

tiveram seus leiautes otimizados para a aplicação mostrada.

3.4

-

3.4.1

O AMPLIFICADOR PROGRAMÁVEL ATUANDO COMO CONVERSOR D/A

-

Introdução:

Antes da proliferação dos circuitos integrados, os conversores

basicamente

com

redes "ladder" resistivas.

também

totalmente integrados

tecnologia bipolar [l6].

As

D/A eram implementados

primeiras tentativas de se obter conversores

utilizavam redes de escalamento resistivas, implementadas

em

A fim de melhorar o casamento e atenuar os efeitos da deriva ténnica nos

resistores integrados bipolares, os projetistas

de CIs passaram a procurar novas altemativas de

implementação de conversores integrados. Surgiram outras possibilidades, como conversores

implementados

em tecnologia híbrida (resistores de filme fino) e também na tecnologia bipolar/IZL,

entre outras [22].

Com

tecnologia

o crescimento da utilização de técnicas

digitais

no processamento de

CMOS provou ser a mais adequada para a integração de circuitos digitais.

tomaram-se,

então,

partes

indispensáveis

sinais,

a

Conversores

no projeto de sistemas totalmente integrados.

Conseqüentemente, aumentou-se a necessidade de se obter conversores mais precisos e mais

compactos, deixando assim maior área para o circuito

Desta maneira os circuitos analógicos devem

digital

ter seus requisitos

de processamento de

sinais [l6].

de projeto adequados à tecnologia

20

CMOS»digital

CMOS

área,

e,

de preferência, serem apropriados à implementação

e capacitores lineares são obtidos a custas de

digital, resistores

o que se torna

Nos DACs

crítico

resistivos é necessária a utilização

de escalamento

utilizar a capacitância

como

operar

grande ocupação de

de tecnologias especiais para a obtenção de

não permite a implementação de conversores com

em tecnologia digital. Nas redes

de porta dos transistores

MOS,

capacitivas existe a possibilidade de se

que, se devidamente polarizados

podem

um

Outra metodologia possivel de se implementar conversores capacitivos é

bits.

a de se utilizar duas camadas de

polisilício

na tecnologia

MOS

digital.

Esta opção não é

com a integração em alta escala.

Pode-se também obter conversores através da utilização de transistores

como

circuitos

capacitores quase lineares [2l]; entretanto, esta opção só é possível para

pequeno número de

compatível

uma

tecnologia

quando o número de bits do conversor aumenta.

resistores lineares precisos. Isto

resistivos

em SoG. Na

fontes de corrente [22]. Esta técnica,

inconveniente de ocupar

uma

MOS

atuando

das atualmente mais utilizadas, apresenta o

uma área muito grande quando

a conversão envolve

um elevado número

de bits, pois a área ocupada pelos transistores cresce exponencialmente com o número de bits.

Apresentaremos

uma técnica de

implementação de conversores

rede "ladder" T-2T, apresentada anteriormente. Esta técnica resulta

compactos e totalmente

3.4.2

-

integráveis

em tecnologia CMOS

digital

D/A que tem como

em

base a

conversores simples,

convencional.

Conversor digital-analógico:

Conversores

D/A

são utilizados para transportar dados transmitidos, armazenados ou

resultados de processamento digital de volta para o

mundo

analógico.

A conversão de uma palavra digital em tensão ou corrente analógica envolve. algum tipo de

circuito

digitais

de escalamento, que é utilizado com o objetivo de obter cópias analógicas dos dados

A saída analógica representa uma versão escalada de uma tensão ou corrente

O número de bits que um DAC ("digital-analog converter") pode alcançar é dado

de entrada.

de referência.

pela precisão do circuito de escalamento.

21

A variável de saída pode ser obtida da seguinte expressão:

Ç0U,=CREF(Âf+Ê2i+i:+...+bL¡;')

2

onde n é o número de

do conversor,

bits

e

C pode representar corrente ou

-

"most significant

bit") e

"least significant bit") e

Conversores

tensão.

tem peso

tem peso

D/A

bi

2

2

(3.4)

2

corresponde a

um bit

de entrada (assume valor O ou

1)

O coeficiente bo representa o bit mais significativo (MSB

igual a 24

Cm, O

.

bit

bm, é

o

bit

menos

significativo

(LSB

2`"CREF.

apresentam 2" níveis discretos para o

sinal

analógico de saída, que

variam, no caso da equação (3.4), de zero até (l-2`")CREF ou seja, de O até (Cmf -

1

LSB).

A característica estática ideal de um DAC de 3 bits é mostrada na figura 3.6.

F.s.- -----------------------------------------------------------------------------------------------------

--

1/8- coNvERsÃo D/A IDEAL

3/4 '-

sAiDA

1

5/8 __

ANALÓGICA

1/2

NoRMAuzADA

LsB

-

3/3 ”

SAIDA

ANALÓGICA

IDEAL

l/4 'l/8 "'

0

ooo

ooi

oio

ou

ioo

ioi

cÓD1oo DE ENTRADA

Figura 3.6 - Função de transferência

3.4.3

-

Implementação discreta de

ideal

de

11o

111

Dio¡TA1.

um conversor D/A de 3

bits

um DAC de 4 bits:

Através do circuito do amplificador programável (figura 3.1) é possível implementar

conversor digital-analógico [23].

-

um

22

Na figura 3.7

(a) é

mostrado

um circuito

de escalamento de corrente de

4-bits.

Nas figuras

3.7 (b) e (c) estão representados os circuitos conversores lineares de tensão-corrente da entrada e

corrente-tensão da saída, respectivamente.

Na figura 3.7 (b),

a corrente

a tensão de entrada V, e convertida linearmente

é convertida (não lineamiente)

Ií

em Vw,

transistores iguais, é equivalente à associação série

entrada da rede da figura 3.7 (a) é

palavra

digital,

corrente

da corrente

I

(,<

‹-¡<

_Y_

_'Í_

[-lj

_i_

1

|-J:-|

VB

VH

VB

fiiffli

H

.

"sum-line" é

uma fração,

programável pela

por seu lado, reconverte o

_L

sinal

O<I

q<

_Y_

|T|

3

|-1-|

4

VB

É

VB

vB

i_,vc

~

composta por

de dois transistores. Portanto, a corrente de

O conversor de saída,

2

VB

I_‹,vc

z

A rede divisora de corrente,

.

A corrente Io na

de entrada.

em tensão.

Vdc

I¡.

em I¡=V¡/R. Por sua vez,

.

Pvc

vB

fzaifffii

Io<L "Sum-line"

I

.

VB

|_°vC

i*°VC

la

,,

Dump-line

.

,,

(H)

vc

vc

_?__9_

vz

'JT'

I

I

as

0

I

VB

VB

10

R

í

|,z

é

'

é

+

(b)

Figura 3.7

(a)

-

(C)

D/A de 4

bits

rede de escalamento da corrente

V-I da entrada

conversor linear I-V da saída

V0

éz

-T»

Conversor

(b) conversor linear

(c)

O

Vref

de

23

Um

C4007,

foi

protótipo discreto de 4

bits,

com

implementado segundo o esquema

transistores

elétrico

MOS

da figura

3.7.

canal-n do circuito integrado

A operação do DAC

é muito

simples: a corrente injetada no transistor de entrada é sucessivamente dividida por dois nos nós

2, 3 e 4.

A palavra digital de entrada controla as chaves MOS,

"sum-line" ou na "dump-line".

em tensão

A

1,

que injetam as correntes binárias na

A corrente somada no nó inversor do ampop de saída é convertida

devido ao resistor linear na saída.

característica estática

desta figura

vemos

do protótipo discreto

que, apesar de se tratar de

alcançada pelo conversor

.

está mostrada na figura 3.8 [23]. Através

uma montagem

discreta, a resolução

Em uma versão totalmente integrada o

de 4

bits é

casamento entre os transistores

é muito melhor, possibilitando a implementação de conversores de maior resolução.

Compensação

nos desvios causados pela variação da temperatura pode ser obtida se os transistores do conversor

V-I, a rede de escalamento e os resistores lineares da entrada e da saída forem implementados no

mesmo

"chip".

'Â

Figura 3.8

-

Característica estática

do protótipo discreto de [bits

7

rlz

24

Os

substratos,

terminais de porta de todos os transistores estão ligados

em

em VDD

(+7,5

A palavra digital foi obtida através de um contador binário

Vss (-7,5 V).

o complemento desta palavra

utilizando o circuito integrado 40161, e

foi

obtido

com

V)

e seus

de 4

bits,

inversores

CMOS do CI 4069.

Também foram

projetadas duas redes divisoras integradas de 8

e diferentes geometrias dos transistores,

com o

são mostrados na figura 3.9.

leiautes

intuito

Um

bits,

com

diferentes leiautes

de verificar a precisão das duas versões. Os

dos leiautes seguiu a topologia utilizada na

implementação SoG, como mostrado na figura 3.9

Nesta implementação podemos notar que

(a).

grande parte da área do leiaute é ocupada pelas linhas de interligação. Para a outra rede de

escalamento

um

foi utilizado

leiaute

dedicado (figura 3.9

(b)),

onde

foi

dada atenção ao melhor

uma área de 240 um x 300 um.

casamento entre os transistores (10 um/20 um). Esta rede ocupou

Estes conversores foram implementados através do Projeto Multiusuário Brasileiro de

número 9

(PMUC

009). Entretanto, até o presente

momento, as amostras dos "chips" não foram

enviadas.

3.5

-

coNcLUsÃo

A

técnica de implementação de conversores

divisora de corrente apresenta compatibilidade

D/A

com

por meio de

uma

rede transistorizada

a tendência atual de implementação de

tem gerado estudos sobre este tipo de conversores

[l8, 24, 25].

Sua

precisão depende basicamente do casamento dos transistores e segundo [18] pode alcançar

uma

circuitos integrados e

resolução de 8 bits para

uma implementação em SGG

e de 9 bits

em uma

versão

"full

custom".

Apesar de apresentar resolução da ordem das obtidas por outras técnicas (que não utilizam auto

correção), os conversores gerados por esta técnica são totalmente compatíveis

CMOS

digital

e

podem

ser

implementados em SoG.

com o número de

bits.

Além

qualquer conversor D/A, são realizadas pelos

disto, as chaves,

mesmos

a tecnologia

Também ocupam pequena

principalmente, por utilizar a topologia da rede "ladder" R-ZR, na qual o

cresce linearmente

com

área,

número de componentes

componentes indispensáveis em

transistores

que realizam a função de

25

escalamento, resultando

parasitários

em maior economia

no caminho do

A simplicidade de projeto e de operação representa

de corrente.

sinal

de área e evitando a introdução de elementos

outro ponto positivo desta técnica, onde, para se aumentar o número de bits basta acrescentar

ramos idênticos à rede "ladder" de escalamento.

Nos casos em que a saída do DAC é em

corrente não há a necessidade do uso de

em

na saída e a velocidade de conversão é maior do que a da rede com saída

saída

em tensão

.«‹;#3..

”`

--.

>

-~.--_

.

É

Í

tensão. Pois

›

`

ii*

Â

.›

-.‹-×~=

=

r

i

ÍY

Í.

›

`

l

--=¬

.B

1

_.

"

fl

nz

za

.,›

~

Íf

_*

›

131

__

Í

É

:wa

s

R

<rz°<w

www

*

buunni u

"=°~

inn--z

mas-x

uma

*wa \×â x›

iqaâ pra

fëšš

tz

§¿;2

ק

gm

M

ea

s lã

M

fi

-

‹.‹:-.›,~.›~»-‹››z.-.z‹1›..›z.›z.»

com

a velocidade da conversão fica limitada pelo "slew rate" do amplificador de saída.

`

à

um ampop

‹‹-›.×›w~»‹‹›z›,-‹zø›ôs

š‹

_`

“atsáe

J.

Illn\~z vz

2

xwai sam naun:

.×\*

‹

.aöm

.‹

vz.

_

›

.

~'

ls-.:s.‹››‹:<›â;¢‹¬-wwiwm2;§z-z.<.;‹¢:‹xקR=.z;=ss‹~››:<z›;\›×=»›:‹×,‹z›‹<›››.rse.:.›:õz+›‹›:4z‹.‹,››«-:;.=

'

››››.~,,›s›.=,›z;-:›:,.-‹'z,»›w››zn,»¿;.z.››z:..×'z.z.z.z.z›z››=~››:-z×z.z;,¿;;;é›z›.:z=›z›z-,z.z=.ó--tz.zz.,z:›z›z:›:z.‹:..z=-

|--_í-4

lootzm

3.9 (a)

iooum

cw-v..

H

iii

i

.QI

.

.,›

"ig

A'

...›‹.›..

.

~

I 1.

aiú l'

\::i¡"--‹í»»í;

1:

~

t;_.

êé»

r¡

i

3.9(b)

Figura 3.9

-

Leiautes da rede de escalamento implementadas no

(a)

SoG

e (b) "full-custom"

PMU 9

26

CAPÍTULO IV - FILTROS SI PROGRAMÁVEIS

UMA NOVA

-

METODOLOGIA

4.1 -

INTRODUÇÃO

No

auge

de

sua

popularidade,

"switched-capacitors") foram utilizados

com

em

a

circuitos

chaveados

capacitores

(SC

-

implementações de subsistemas completos. Porém,

a evolução tecnológica, começaram a aparecer novas soluções através do processamento

digital

de

sinais.

A técnica digital

apresenta grande simplicidade de projeto e

menor tempo para

obtenção do produto final, proporcionando soluções mais econômicas para implementação de

sistemas integrados.

O

desenvolvimento da tecnologia possibilitou a integração de sistemas

completos, incluindo circuitos digitais e analógicos,

em um mesmo

"chip".

analógicos restou, então, pouco mais do que a função de condicionamento de

SC passaram

extemo ao

a efetuar a função de interfaceamento entre o sistema

"chip".

Embora já

sabido que circuitos

SC não

digital e

Aos

sinais.

Os

circuitos

circuitos

o mundo analógico

necessitem de capacitores lineares para

sua implementação [35], circuitos a capacitores chaveados têm sido normalmente integrados

através de processos tecnológicos não convencionais, tais

hoje

em dia não mais do que 10-20%

[26] da área total

como duplo

Considerando que

do "chip" é ocupada pela porção analógica

do sistema, é conveniente que a técnica de implementação do

digital,

poli.

circuito anlógico seja a

CMOS

evitando encarecimento do produto final devido ao uso de tecnologia não convencional.

No final

da década passada

foi

"switched-current") [27], que tinha

proposta

como

uma técnica denominada

VLSI

-

objetivo principal reduzir o custo de fabricação de

circuitos integrados digitais/analógicos ("mixed ICs"), através

processos

corrente chaveada (SI

de sua

total compatibilidade

com

convencionais. Alguns circuitos já foram fabricados utilizando a técnica de

corrente chaveada [28]; contudo é

dificil

concluir

com

os resultados já obtidos se os circuitos SI

podem oferecer desempenho adequado em uma larga faixa de operações.

Filtros analógicos

programáveis obtidos através de implementações convencionais já foram

implementados e mostraram ocupar grande

área, tanto

com banco de

capacitores [29],

como com

27

de espelhos de corrente

filtros SI, que

podem

T-2T apresentada

[30].

Neste capítulo será apresentada uma nova metodologia para se obter

ser programáveis [32].

anteriormente, sendo

técnica é totalmente compatível

4.2

-

4.2.1

A programabilidade é obtida através da rede "ladder"

também

utilizados

com a tecnologia CMOS

ampops, chaves e capacitores. Esta

digital.

O INTEGRADOR EM CORRENTE CHAVEADA

-

Circuitos de 1” geração:

O

A

objetivo da técnica de corrente chaveada é de realizar o processamento analógico de

sinais através

de operações elementares

em amostras de corrente. O espelho

de corrente chaveado

é capaz de realizar as quatro operações básicas exigidas no processamento de

sinais: inversão,

soma, escalamento e atraso.

A figura 4.1

nova metodologia.

mostra os espelhos de corrente de

O espelho de corrente proposto

4.1 (a) e é implementado

de

um ampop

com

(terra virtual) e

dois transistores

geração convencional e propostos pela

da figura 4.1 (b) é baseado na célula da figura

MOS, um

entre a saída e a entrada não inversora

o outro entre a saída e o terra (ou terra

seguidor de tensão evita que o capacitor

de

1°

C

virtual

de outro ampop).

O

de memorização descarregue através dos transistores

saída.

O funcionamento

das células das figuras 4.1

a chave S está fechada, o circuito se comporta

correntes de saída

invertidas).

is

e

ic

acompanham

Quando a chave S

(a) e (b) é simples.

como um

Durante o periodo

espelho de corrente contínuo e as

a corrente de entrada i A (são réplicas escaladas e

é aberta, a saida é desconectada da entrada; porém, a capacitância

C mantém uma tensão V dependente da corrente no transistor T-A no semi-ciclo de

e as correntes de saída

e "hold" (fase

(1),)

em que

permanecem

inalteradas.

"clock" anterior

Este circuito realiza a fiinção de "track" (fase ¢,)

cujas saidas correspondem a réplicas escaladas e atrasadas de meio período de

"clock" da corrente de entrada.

28

GW GW»

ea»

Ú

_~

Ú

Y7

'

:blg

S

C

:Élc

::::::§::::::

B

1

Y

4.1 (a)

VC

Vc

_f_

1

IA

›

_

.

}

B

I

VC

ic

Tc

4.1 (b)

vz

_r_

1

1

T^

B

$_/¢,

T

__

TB

C

S

B

¡

i

TB

_

\¢l

Tc

¢;_~

íC

B

_:

=

4.1 (c)

Figura 4.1

-

Espelho de corrente

(l“ geração) - (a) convencional, (b)

e (c) proposto

Uma

proposto

modificado

versão modificada do espelho de corrente proposto, que necessita de apenas

amplificador operacional, é mostrada na figura 4.1

(c).

As chaves são

um

controladas por duas fases

29

de "clock"

(4),

e

controladas por

anterior.

Na

(bz)

d),

não sobrepostas, exibidas na figura

C

estão fechadas, o capacitor

4.2.

é carregado

fase ¢2, a entrada é desconectada e o capacitor

Neste

com

quando as chaves

circuito,

a tensão

C com

V

a tensão

idêntica ao caso

V

memorizada é

ligado à entrada não inversora do ampop, que opera na configuração seguidor, devido à

realimentação unitária da saida para a entrada proporcionada por TA.

espelhos de corrente, na fase

¢2,

i¢(n)=-yiA(n-1/2)

e

meio período de "clock".

figura 4.3 mostra os circuitos de atraso de

No

cascateamento de duas células "track-and-hold".

figura 4.3

(b),

durante a fase

¢2,

Na

fase

cbz,

dos circuitos de atraso da figura

iol

(n-1)

circuito

ciclo

de "clock", obtidos pelo

de atraso proposto, mostrado na

(n-1/2)

Figura 4.2

-

(U)

a tensão no capacitor C2 origina

‹1›,,

idêntica à corrente de entrada, exceto por

durante a fase

um

o capacitor C, é carregado com a tensão V, que depende da

corrente de entrada e do transistor T.

em TB

(4.1)

fatores de escalamento. Nota-se que as correntes de saida durante a fase ¢2 são

réplicas invertidas da entrada atrasadas de

A

correntes de saída destes

são dadas por:

iB(n)=-[3iA(n-1/2)

onde B e y são

As

=B

n

um fator de escalamento. As

uma

corrente

correntes de saída,

4.3 são idênticas e iguais a:

ii

(Ú

_1)

(n+1/2)

Sinais de "clock"

(4-2)

(n+1)

não sobrepostos

30

11

Ê

-IB

-I

Ê

Ílj/¢Í2-lí

MÃE

;JÍl‹ÍÍ+lL;

11

-'I

IB

11

4.3 (a)

1

.L

Vc

Vc

¢7

=

¡

Vlw

T

1

Ci I

¡

C1

¢|

_

ic

1:

T°

iu:

-z

4.3 (b)

Figura 4.3

-

Circuito de atraso (la geração)

Integradores SI de

1”

anteriormente, realimentando

geração

podem

uma fração da

mostrado o integrador SI convencional de

-

(a) convencional e (b)

ser obtidos

com

os circuitos de atraso citados

corrente de saida para a entrada.

1”

proposto

Na figura 4.4

(a) é

geração [26] enquanto o integrador SI proposto

neste trabalho é apresentado na figura 4.4 (b).

Analisando a figura 4.4, fazendo

i¡2

= O e in = O, vemos que na fase ¢2 a corrente de

saída é

dada por:

io(n)='YÍ¡(n`l)+l3Ío(n_1)

(4-3)

14

4

Ê

¢1

.

1»

Ê

S2

ni

§H_J<;+í

Qffizäbfik

fióã

I!

_

A

Q

..í._f\_.D

,

I

\`7

1,3

*1

*1

°

311:

*1

Ç

4.4 (a)

A*

*fi

|›-oÕ<

|--‹›°<

I

I

'-I

T

°<

›

B

4,'

l

C2

ic

Ts

T°=

i°

4.4 (b)

Figura 4.4 - Integrador SI universal de

1”

geração

-

(a)

convencional e (b) proposto

A função de transferência H,(Z) fica

H.(Z>

vz”

=l~=--,

1-sz'

I'*'1(Z)

1:42)

(4.4)

32

Fazendo

in

=Oe

ii,

= 0, obtemos, na fase ¢2

â0(z›)

:

= mn-1)-Y âzz(n~ 1/2)

(45)

O

Hz(Z)=

Considerando apenas a entrada

â.›(n)

is (in

‹4.õ›

ÍÊN

= O e in = 0), obtemos

durante a fase ¢2

:

= rf›â‹,(n-1)~v(â¡z(n-1/2)-âíz(n - 1))

(41)

Portanto, as funções de transferência H;(Z) e Há' (Z) resultam,

,

O

_1ã=(

NN

)__

vz"'”

)- ífiBZ_I

C

_I$1(

,

integrador SI mostrado na figura 4.4 é conhecido

superposição, sua corrente de saída, na fase ¢2

Ig*

(Z)

Se B =

=Y

1,

EI??

Z-l

,

integrador universal. Por

Zé

Z-l/2

Z-l

(Z)" Yí-_[?I¡z'¢ (Z) -Y 1ÍñIÊ'Ê;'(Z)+'Y1___ÊIil'$“(Z)

sem

(4-9)

perdas.

os coeficientes dos integradores SI são determinados pelas razões de aspecto

dos transistores que constituem os espelhos de corrente.

transistores causa distorção

ao,

como

expressa no domínio

Z-I/2

_ vz*

as funções de transferência correspondem às de integradores

Notamos que

freqüência

Q/

NN

em

sua sensibilidade

Na

prática,

o descasamento entre os

relação à função de transferência ideal.

em

relação a B

relação a B, do integrador não inversor, são [31]

,

O

ganho de baixa

a freqüência de corte mo e sua sensibilidade

em

33

a.,=í{í=>s§‹›=ä

(4.1o)

w.=-_2(l_B)=>sg°»=iB

(4.11)

1- B*

T(1+p)

onde T é o período de

dependente do valor de

"clock".

B,

com pouco amortecimento

à variação de

freqüência de

apresentam

B.

Por

"clocl_<"

alto fator

A

resposta

_

em

freqüência do integrador SI é extremamente

por sua vez dependente do casamento entre transistores. Integradores

([3-›l) apresentam o

isto este circuito

ganho

DC e a freqüência de corte muito sensíveis

não é adequado para o projeto de filtros nos quais a

é muito mais alta do que a freqüência de corte do filtro ou para aqueles que

de qualidade (Q).

Circuitos de 2” geração:

4.2.2

-

Uma

nova estrutura a correntes chaveadas, chamada de

implementação de integradores

com

2” geração foi proposta [31] para

baixo fator de amortecimento. Esta estrutura é baseada no

espelho de corrente chaveado da figura 4.5.

ígíi

~

_

Ê--í-vi.

V1

T

1

1-:í::;Í::::::

CG

A

Figura

4.5

-

Espelho de corrente chaveado

(2a

geração)

34

Seu funcionamento é o

seguinte:

na fase ¢2 o transistor

I

e é estabelecida

uma tensão VG no

devido à tensão

VG e,

= J + i¡

capacitor CG.

(4.

Na outra fase (¢,),

esta corrente é mantida

12)

em T

então, a corrente de saída será

io

Na ñgura

T conduz a corrente

= -i¡

(4.l3)

4.6 (a) apresentamos o circuito de atraso de 2” geração convencional enquanto

A análise do circuito

com uma tensão V que é

na figura 4.6 (b) apresentamos o circuito de atraso proposto neste trabalho.

de atraso proposto mostra que, na fase

d›,,

o capacitor C, é carregado

determinada pela corrente de entrada e pelo transistor

desconectada da entrada e a soma das correntes

apresentam,

em ¢2,

em T,

T2.

Na

fase ¢,, a corrente de entrada

é

e T2 é igual a zero. Estes circuitos de atraso

a corrente de saída,

(414)

¡0(n)=vâf(n-1)

Como vimos anteriormente, um integrador

realimentação de

ii

uma

SI é obtido de

um

circuito

de atraso através da

fração da corrente de saída para a entrada. Portanto, resultam os

integradores exibidos na figura 4.7.

A análise destes circuitos mostra que na fase ¢,, a função de tranferência é dada por:

r

que corresponde à funçao de transferência de

na expressão

(4.3).

um integrador não inversor sem perdas,

obtida

como

1

âV

J

n

Q

4

ê

J

ea

-->

VI3

4

1

11

E

_I::ê_\_]

íí'

“

1

>

'1

io

9:-1

;

y

14

4.6 (a)

VC

i

1

l

TlÍ>

1ÍT2|

'Í

f¬

¢›z

/(bl.

\¢1

ÍÍ

1

*Ti

/“W

~

4.6 (b)

Figura 4.6

-

Circuito de atraso (2“ geração)

-

(a)

Y

ši

T3”

convencional e (b) proposto

io

36

V7]

2]

I

-i>

li

-l>'*¢,

T*

T2

VI3

(mk

11

I2

)¢2

IET3

I

i

1

1

to

4.7 (a)

Vc

1

M

1

il

T1

'ÍI

D

/¢2°

vw-

O

IQ

_e,\

,__

1.

\

iz

2

¢,

Q. ci

I

__

Í

V°

-.-

¢1

Y

C2

_f_

io

T3

lí

4.7 (b)

Figura 4.7 - Integrador sem perdas

(23 geração)

-

(a) convencional e (b)

proposto

Se além da realimentação realizada fizermos uma realimentação extra de uma fração da

corrente de saida, é possivel obter

um

integrador SI amortecido, à semelhança do que é feito na

técnica de capacitores chaveados. Este integrador é conhecido

como

integrador SI universal de

37