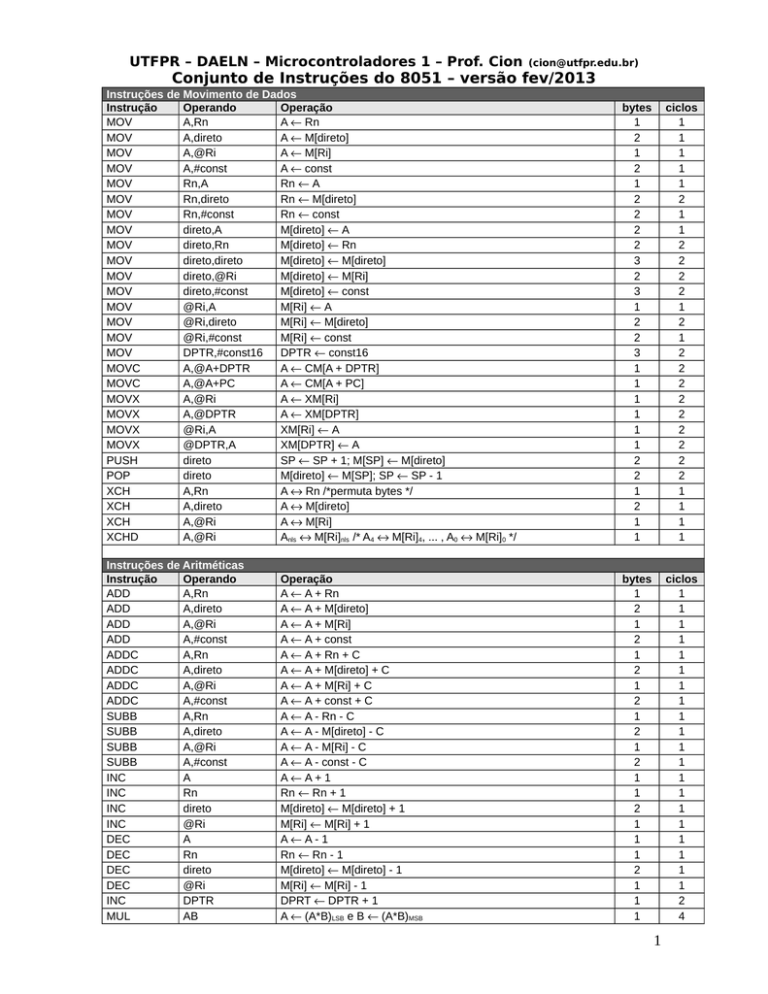

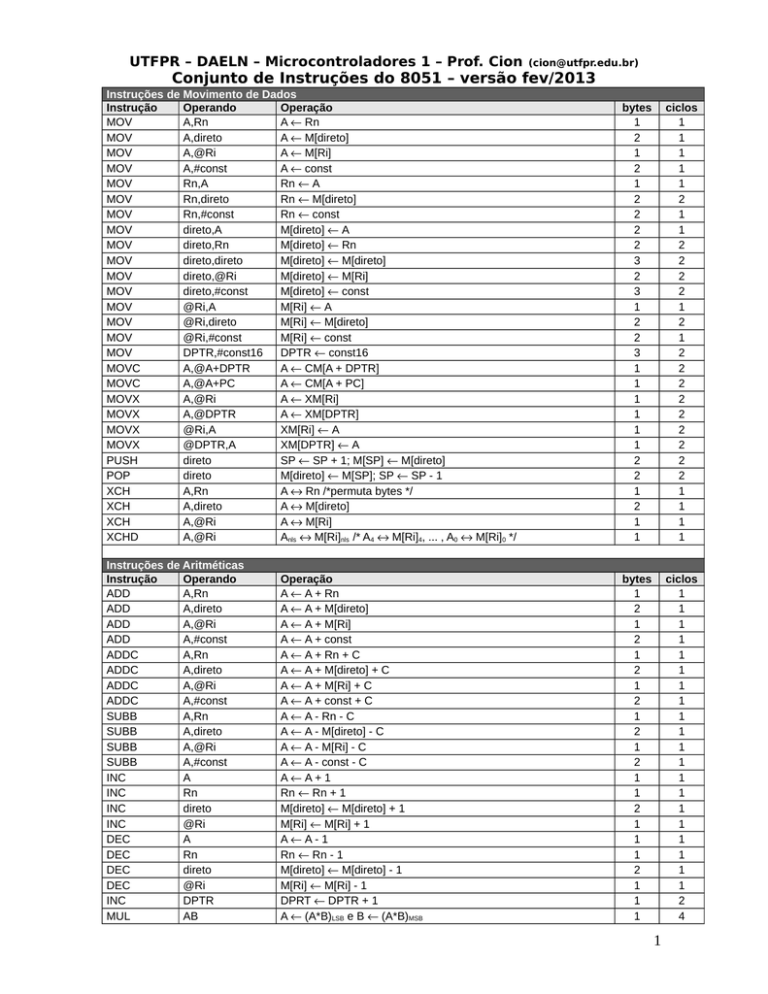

UTFPR – DAELN – Microcontroladores 1 – Prof. Cion

([email protected])

Conjunto de Instruções do 8051 – versão fev/2013

Instruções de Movimento de Dados

Instrução

Operando

Operação

MOV

A,Rn

A Rn

A M[direto]

MOV

A,direto

MOV

A,@Ri

A M[Ri]

A const

MOV

A,#const

MOV

Rn,A

Rn A

Rn M[direto]

MOV

Rn,direto

MOV

Rn,#const

Rn const

M[direto] A

MOV

direto,A

MOV

direto,Rn

M[direto] Rn

M[direto] M[direto]

MOV

direto,direto

MOV

direto,@Ri

M[direto] M[Ri]

M[direto] const

MOV

direto,#const

MOV

@Ri,A

M[Ri] A

M[Ri] M[direto]

MOV

@Ri,direto

MOV

@Ri,#const

M[Ri] const

DPTR const16

MOV

DPTR,#const16

MOVC

A,@A+DPTR

A CM[A + DPTR]

A CM[A + PC]

MOVC

A,@A+PC

MOVX

A,@Ri

A XM[Ri]

A XM[DPTR]

MOVX

A,@DPTR

MOVX

@Ri,A

XM[Ri] A

XM[DPTR] A

MOVX

@DPTR,A

PUSH

direto

SP SP + 1; M[SP] M[direto]

M[direto] M[SP]; SP SP - 1

POP

direto

XCH

A,Rn

A Rn /*permuta bytes */

A M[direto]

XCH

A,direto

XCH

A,@Ri

A M[Ri]

Anls M[Ri]nls /* A4 M[Ri]4, ... , A0 M[Ri]0 */

XCHD

A,@Ri

bytes

1

2

1

2

1

2

2

2

2

3

2

3

1

2

2

3

1

1

1

1

1

1

2

2

1

2

1

1

ciclos

1

1

1

1

1

2

1

1

2

2

2

2

1

2

1

2

2

2

2

2

2

2

2

2

1

1

1

1

Instruções de Aritméticas

Instrução

Operando

ADD

A,Rn

ADD

A,direto

ADD

A,@Ri

ADD

A,#const

ADDC

A,Rn

ADDC

A,direto

ADDC

A,@Ri

ADDC

A,#const

SUBB

A,Rn

SUBB

A,direto

SUBB

A,@Ri

SUBB

A,#const

INC

A

INC

Rn

INC

direto

INC

@Ri

DEC

A

DEC

Rn

DEC

direto

DEC

@Ri

INC

DPTR

MUL

AB

bytes

1

2

1

2

1

2

1

2

1

2

1

2

1

1

2

1

1

1

2

1

1

1

ciclos

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

4

Operação

A A + Rn

A A + M[direto]

A A + M[Ri]

A A + const

A A + Rn + C

A A + M[direto] + C

A A + M[Ri] + C

A A + const + C

A A - Rn - C

A A - M[direto] - C

A A - M[Ri] - C

A A - const - C

AA+1

Rn Rn + 1

M[direto] M[direto] + 1

M[Ri] M[Ri] + 1

AA-1

Rn Rn - 1

M[direto] M[direto] - 1

M[Ri] M[Ri] - 1

DPRT DPTR + 1

A (A*B)LSB e B (A*B)MSB

1

DIV

DA

AB

A

A quociente(A/B) e B resto(A/B)

Ajuste Decimal do Acumulador

Instruções Lógicas e de Rotação

Instrução

Operando

Operação

A A Rn

ANL

A,Rn

ANL

A,direto

A A M[direto]

A A M[Ri]

ANL

A,@Ri

ANL

A,#const

A A const

M[direto] M[direto] A

ANL

direto,A

ANL

direto,#const

M[direto] M[direto] const

A A Rn

ORL

A,Rn

ORL

A,direto

A A M[direto]

A A M[Ri]

ORL

A,@Ri

ORL

A,#const

A A const

M[direto] M[direto] A

ORL

direto,A

ORL

direto,#const

M[direto] M[direto] const

A A Rn

XRL

A,Rn

XRL

A,direto

A A M[direto]

A A M[Ri]

XRL

A,@Ri

XRL

A,#const

A A const

M[direto] M[direto] A

XRL

direto,A

XRL

direto,#const

M[direto] M[direto] const

A0

CLR

A

CPL

A

A /A

1

1

4

1

bytes

1

2

1

2

2

3

1

2

1

2

2

3

1

2

1

2

2

3

1

1

ciclos

1

1

1

1

1

2

1

1

1

1

1

2

1

1

1

1

1

2

1

1

RL

A

1

1

RLC

A

1

1

RR

A

1

1

RRC

A

1

1

SWAP

A

1

1

bytes

1

2

1

2

1

2

2

2

2

2

2

2

ciclos

1

1

1

1

1

1

2

2

2

2

1

2

2

2

2

2

3

2

3

2

3

2

Instruções Booleanas

Instrução

Operando

CLR

C

CLR

bit

SETB

C

SETB

bit

CPL

C

CPL

bit

ANL

C,bit

ANL

C,/bit

ORL

C,bit

ORL

C,/bit

MOV

C,bit

MOV

bit,C

JC

rel

JNC

rel

JB

bit,rel

JNB

bit,rel

JBC

bit,rel

Anms Anls /* A7 A3, ..., A4 A0 */

Operação

C0

BM[bit] 0

C1

BM[bit] 1

C /C

BM[bit] /BM[bit]

C C BM[bit]

C C /BM[bit]

C C BM[bit]

C C /BM[bit]

C BM[bit]

BM[bit] C

Se (C == 1) PC PC rel

Senão PC PC + 2

Se (C == 0) PC PC rel

Senão PC PC + 2

Se (BM[bit] == 1) PC PC rel

Senão PC PC + 2

Se (BM[bit] == 0) PC PC rel

Senão PC PC + 2

Se (BM[bit] == 1) {BM[bit] 0; PC PC rel

Senão PC PC + 2}

2

Instruções de Desvio

Instrução

Operando

ACALL

end16

LCALL

end16

RET

RETI

AJMP

LJMP

SJMP

JMP

end11

end16

rel

@A+DPTR

JZ

rel

JNZ

rel

CJNE

A,direto,rel

CJNE

A,#const,rel

CJNE

Rn,#const,rel

CJNE

@Ri,#const,rel

DJNZ

Rn,rel

DJNZ

direto,rel

NOP

Notação

Rn

direto

@Ri

#const

#const16

end16

end11

rel

bit

M

XM

CM

BM

+

*

/

Operação

SP SP + 1; M[SP] PClsb; SP SP + 1; M[SP] PCmsb;

PC end11

SP SP + 1; M[SP] PClsb; SP SP + 1; M[SP] PCmsb;

PC end16

PCmsb M[SP]; SP SP - 1; PClsb M[SP]; SP SP - 1

PCmsb M[SP]; SP SP - 1; PClsb M[SP]; SP SP - 1

PC end11

PC end16

PC PC rel

PC A + DPTR

Se (A == 0) PC PC rel

Senão PC PC + 2

Se (A != 0) PC PC rel

Senão PC PC + 2

Se (A != M[direto]) PC PC rel

Senão PC PC + 3

Se (A < M[direto]) C 1

Senão C 0

Se (A != const) PC PC rel

Senão PC PC + 3

Se (A < const) C 1

Senão C 0

Se (Rn != const) PC PC rel

Senão PC PC + 3

Se (Rn < const) C 1

Senão C 0

Se (M[Ri] != const) PC PC rel

Senão PC PC + 3

Se (M[Ri] < const) C 1

Senão C 0

Rn Rn –1; Se (Rn != 0) PC PC rel

Senão PC PC + 2

M[direto] M[direto] – 1; Se (M[direto] != 0 ) PC PC rel

Senão PC PC + 2

/* Sem operação */

bytes

ciclos

2

2

3

2

1

1

2

3

2

1

2

2

2

2

2

2

2

2

2

2

3

2

3

2

3

2

3

2

2

2

3

2

1

1

Descrição

Rn = {R0,R1,R2,R3,R4,R5,R6,R7} do banco de registradores selecionado

Endereço de 8 bits da IRAM - direto=00..0FFH (00 .. 7FH área de uso geral e 80H a 0FFH área dos SRF)

Define de forma indireta um endereço da RAM interna. Ri é o registrador R0 ou o registrador R1 (Ri = {R0,R1})

Constante de 8 bits (0 a 255 ou de 0 a 0FFH)

Constante de 16 bits (0 a 65535 ou 0000 a 0FFFFH)

Endereço de 16 bits

Endereço de 11 bits

Endereço relativo de 8 bits (varia de –128 a +127)

Endereço direto do bit (RAM bit endereçável ou registrador bit endereçável)

Memória IRAM – M[00]..M[0FFH] – memória RAM interna

Memória RAM externa

Memória de Código (ou memória de programa)

Memória IRAM bit endereçável (00 a 7FH) ou registradores bit endereçáveis

Atribuição

Soma

Subtração

Multiplicação

Divisão (ou Inversão lógica)

Operação lógica E

Operação lógica OU

3

/

nls

nms

Operação lógica OU Exclusivo

Inversão lógica (ou divisão aritmética)

Permuta

Nibble menos significativo (b3,b2,b1,b0)

Nibble mais significativo (b7,b6,b5,b4)

4