Conjunto de instruções e modos de

endereçamento

aula 4

Profa. Débora Matos

Conjunto de Instruções

A = ((B + C) x D + E –F)/(G x H)

A – H – denotam posições da memória –

endereços

As arquiteturas possuem as seguintes

operações aritméticas:

ADD – para soma

SUB – para subtração

MUL – para multiplicação

DIV - para divisão

Arquitetura de 4 endereços

A = ((B + C) x D + E –F)/(G x H)

OP E1 E2 E3 E4

Endereço

Instrução

Comentário

e1

ADD B C A e2

Soma B com C, salva resultado em A

e2

MUL A D A e3

Multiplica A por D, salva resultado em A

e3

ADD A E A e4

Soma A com E, salva resultado em A

e4

SUB A F A e5

Subtrai F de A, salva resultado em A

e5

DIV A G A e6

Divide A por G, salva resultado em A

e6

DIV A H A e7

Divide A por H, salva resultado em A

e7

HALT

Fim do programa

Arquitetura de 4 endereços

Que tipo de instruções não são

necessárias no modelo de

arquitetura com 4 endereços?

Arquitetura de 3 endereços

Surgiu a necessidade de se utilizar um

registrador específico para controlar

o endereço da próxima instrução:

Arquitetura de 3 endereços

Surgiu a necessidade de se utilizar um

registrador específico para controlar

o endereço da próxima instrução:

PC – program counter

Arquitetura de 3 endereços

A = ((B + C) x D + E –F)/(G x H)

OP E1 E2 E3

Endereço

Instrução

Comentário

e1

ADD B C A

Soma B com C, salva resultado em A,

incrementa PC

e2

MUL A D A

Multiplica A por D, salva resultado em A,

incrementa PC

e3

ADD A E A

Soma A com E, salva resultado em A,

incrementa PC

e4

SUB A F A

Subtrai F de A, salva resultado em A,

incrementa PC

e5

DIV A G A

Divide A por G, salva resultado em A,

incrementa PC

e6

DIV A H A

Divide A por H, salva resultado em A,

incrementa PC

e7

HALT

Fim do programa

Arquitetura de 3 endereços

Quais as vantagens e desvantagens da arquitetura de 3

endereços para a arquitetura de 4 endereços?

Vantagens:

Redução do tamanho da instrução -> redução do tamanho da

memória;

Desvantagens:

Necessidade de instruções explicitas de desvio (como JUMP e

BRANCH);

Não permite mais executar simultaneamente uma

instrução de manipulação de dados e uma instrução

de desvio do fluxo de programa.

Arquitetura de 3 endereços

Quais as vantagens e desvantagens da arquitetura de 3

endereços para a arquitetura de 4 endereços?

Vantagens:

Redução do tamanho da instrução -> redução do tamanho da

memória;

Desvantagens:

Necessidade de instruções explícitas de desvio (como JUMP e

BRANCH);

Não permite mais executar simultaneamente uma instrução

de manipulação de dados e uma instrução de desvio do fluxo

de programa.

Arquitetura de 2 endereços

A economia de memória e a obrigatoriedade de

desenvolvimento de programas sequencias compensam o

grau de liberdade as instruções com 4 endereços;

No entanto, instruções de 3 endereços ainda consomem

muita memória;

Observando-se os programas de 3 instruções, muitas das

vezes, um dos operandos fonte é o mesmo operando

destino. Simplificando-se essa arquitetura, tem-se

arquiteturas de 2 endereços.

Arquitetura de 2 endereços

OP E1 E2

E1 e E2 – indicam a localização dos dois operandos fontes;

E1 – indica também a localização do operando destino;

Não são mais possíveis instruções com 3 operandos

distintos.

O que muda agora?

Arquitetura de 2 endereços

OP E1 E2

Maior redução das instruções;

Pode requerer 2 instruções para apenas 1

instrução da arquitetura com 3 endereços;

Introduz uma restrição: o resultado é armazenado

em um dos operandos fonte, perdendo o dado

anterior deste operando;

Que grupos de instruções foram necessárias

agora?

Arquitetura de 2 endereços

A = ((B + C) x D + E –F)/(G x H)

OP E1 E2

Endereço

Instrução

Comentário

e1

MOV A B

Move B para A

e2

ADD A C

Soma A com C, resultado em A

e3

MUL A D

Multiplica A por D, resultado em A

e4

ADD A E

Soma A com E, resultado em A

e5

SUB A F

Subtrai F de A, resultado em A

e6

DIV A G

Divide A por G, resultado em A

e7

DIV A H

Divide A por H, resultado em A

e8

HALT

Fim do programa

Arquitetura de 1 endereço

Com a criação de registradores especiais, pode-se

reduzir ainda mais o número de endereços,

criando-se as arquiteturas de 1 endereço;

OP E1

E1 indica a localização de um operando de

memória, normalmente 1 dos operandos fontes

da operação;

O outro operando é o acumulador (AC);

O acumulador assume os papéis de um dos

operandos fonte e do operando destino.

Arquitetura de 1 endereço

OP E1

Agora as instruções de movimentação precisam

ser subdivididas de acordo com o sentido da

transferência:

Da memória para o acumulador (LDA – LoaD

acumulator)

Do acumulador para a memória (STA – STore

Acumulator)

Arquitetura de 1 endereço

A = ((B + C) x D + E –F)/(G x H)

OP E1

Endereço

Instrução

Comentário

e1

LDA B

Move B para o acumulador

e2

ADD C

Soma Acumulador com C, resultado no acumulador

e3

MUL D

Multiplica acumulador por D, resultado no acumulador

e4

ADD E

Soma acumulador com E, resultado no acumulador

e5

SUB F

Subtrai F do acumulador, resultado no acumulador

e6

DIV G

Divide acumulador por G, resultado no acumulador

e7

DIV H

Divide acumulador por H, resultado no acumulador

e8

STA A

Armazena acumulador no endereço H

e9

HALT

Fim do programa

Arquitetura de 1 endereço

A grande vantagem deste tipo de arquitetura está

na economia de acessos a memória, realizando

basicamente operações com o acumulador;

Este é o papel dos registradores locais, as

arquiteturas atuais apresentam vários

registradores de uso geral com essa mesma

finalidade.

Arquitetura de zero endereços

OP

Não existe nenhuma referência explícita à

endereços de memória onde estejam localizados

os operandos;

A solução nesse caso é usar uma pilha: os

operandos são sempre retirados do topo da pilha.

Duas instruções manipulam a pilha: PUSH E POP

PUSH – insere um dado no topo da pilha

POP – remove o dado no topo da pilha

Arquitetura de zero endereços

A = ((B + C) x D + E –F)/(G x H)

Endereço

Instrução

Comentário

e1

PUSH H

Coloca H no topo da pilha

e2

PUSH G

Coloca G no topo da pilha

e3

PUSH F

Coloca F no topo da pilha

e4

PUSH E

Coloca E no topo da pilha

e5

PUSH D

Coloca D no topo da pilha

e6

PUSH C

Coloca C no topo da pilha

e7

PUSH B

Coloca B no topo da pilha

e8

ADD

Topo da pilha recebe B + C (B e C são retirados da pilha)

e9

MUL

Topo recebe (B+C) * D

e10

ADD

Topo recebe (B+C) * D + E

e11

SUB

Topo recebe (B+C) * D + E - F

e12

DIV

Topo recebe ((B+C) * D + E – F )/ G

e13

DIV

Topo recebe ((B+C) * D + E – F )/ G * H

e14

POP A

Topo da pilha é armazenado em A

e15

HALT

Fim do programa

Computador Neander

Trata-se de um computador hipotético;

Características:

Largura de dados e endereços de 8 bits;

Dados representados em complemento de 2;

Possui 1 acumulador de 8 bits;

Possui 1 apontador de programas de 8 bits (PC);

1 registrador de estados com 2 códigos de condição:

negativo (N) e zero (Z);

Modos de endereçamento do Neander

O Neander só possui um modo de

endereçamento, o modo direto;

O endereço passado na instrução corresponde o

endereço de memória do operando;

Nas instruções de desvio, o endereço contido na

instrução corresponde à posição de memória onde

está a instrução a ser executada.

Códigos de condição

N (negativo):

1 – resultado é negativo

0 – resultado é positivo (zero é considerado positivo)

Z (zero)

1 – resultado é igual a 0;

0 – resultado é diferente de 0;

As instruções que alteram os códigos de condição

são as instruções lógicas e aritméticas: ADD, NOT,

AND, OR e a instrução LDA.

Conjunto de instruções do Neander

Código

Instrução

Comentário

0000

NOP

Nenhuma operação

0001

STA end

Armazena acumulador – (store)

0010

LDA end

Carrega acumulador – (load)

0011

ADD end

Soma

0100

OR end

“ou” lógico

0101

AND end

“e” lógico

0110

NOT

Inverte (complementa) acumulador

1000

JMP end

Desvio incondicional (jump)

1001

JN end

Desvio condicional (jump on negative)

1010

JZ end

Desvio condicional (jump on zero)

1111

HLT

Término da execução (halt)

Modos de endereçamento do Neander

end – endereço direto

Nas instruções STA, LDA, ADD, OR e AND, end

corresponde ao endereço do operando.

Nas instruções JMP, JN e JZ, end corresponde ao

endereço de desvio.

Conjunto de instruções do Neander

Instrução

Comentário

NOP

Nenhuma operação

STA end

MEM(end) <- AC

LDA end

AC <- MEM(end)

ADD end

AC <- MEM(end) + AC

OR end

AC <- MEM(end) or AC

AND end

AC <- MEM(end) and AC

NOT

AC <- NOT AC

JMP end

PC <- end

JN end

IF N=1 then PC <- end

JZ end

IF Z=1 then PC <- end

HLT

Término da execução (halt)

Formato das instruções

As instruções são formadas por um ou dois bytes,

ou seja, ocupam 1 ou 2 posições da memória;

7

4 3

Código da instruçãoo

0

Não usado

Endereço direto

No Neander as instruções de 2 bytes são aquelas

que fazem referência à memória.

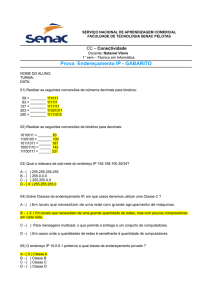

Exercícios sobre o Neander

Para todos os programas considere:

Início do programa – posição 0 (0H)

Início dos dados – posição 128 (80H)

1) Faça um para subtrais duas variáveis de 8 bits

representadas em complemento de 2.

posição 128: minuendo

posição 129: subtraendo

Posição 130: resultado

Exercícios sobre o Neander

2) Determine qual o maior de 3 variáveis positivas

de 8 bits representadas em complemento de 2 e

armazenadas em posições consecutivas de

memória. O resultado (a maior variável) deve

aparecer na posição de memória consecutiva às

ocupadas pelas variáveis na área reservada aos

dados.

Exercícios sobre o Neander

3) Faça um programa que determine a ocorrência de

overflow na soma de duas variáveis. As variáveis

são de 8 bits em complemento de dois e estão

armazenadas em posições consecutivas de

memória (128 e 129). O resultado da soma

também em 8 bits deve aparecer na primeira

posição livre (130) e o overflow deve ser indicado

da seguinte forma:

Posição 131: conteúdo = 0H – não ocorreu overflow

conteúdo = FFH – ocorreu overflow

Modos de

endereçamento

Modos de endereçamento

Imediato

Direto

Indireto

Registrador

Registrador Indireto

Deslocamento (Indexado)

Pilha

Endereçamento Imediato

O operando vem como parte da instrução

Ex. ADD 5

Adiciona 5 ao conteúdo do acumulador

5 é um operando que vem no campo de endereço

da instrução

Nenhum acesso a memória é necessário

Rápido

Intervalo de definição dos operandos é limitado

Endereçamento Imediato

Endereçamento Direto

O campo de endereço contém o endereço do

operando

Ex. ADD A

Procura na posição A da memória pelo operando;

Adiciona o conteúdo da posição A na memória ao

acumulador;

Um único acesso a memória na busca do operando;

Não há necessidade de cálculos adicionais para

encontrar o endereço efetivo;

Espaço de endereçamento limitado pelo campo.

Endereçamento Direto

Endereçamento Indireto

O Campo de endereço aponta para uma posição

de memória que contém o endereço do operando;

Endereço Efetivo EE = Conteúdo da posição (A)

Ex. ADD (A)

Busca em A, encontra o endereço do operando (A)

e busca em (A) pelo operando

Adiciona o conteúdo do endereço efetivo ao

acumulado

Endereçamento Indireto

Endereçamento por registrador

Operando se encontra em um registrador

indicado no campo de endereço da instrução

EE = R

Número de registradores limitado

O campo de endereço não necessita ser grande

Pequenas instruções

Busca da instrução mais rápida

Endereçamento por registrador

Não há acesso a memória

Execução muito rápida

Espaço de endereçamento muito limitado

Mais registradores contribui com o

desempenho

Requer bons compiladores ou boa programação

assembly

Endereçamento por registrador

Endereçamento por registrador indireto

Endereçamento Indireto

EE = (R)

O operando está na posição de memória apontada

pelo do registrador indicado no campo de

endereçamento;

Espaço de endereçamento (2n)

Um acesso a memória

Endereçamento por registrador indireto

Endereçamento por deslocamento

O operando se encontra na memória em uma

posição deslocada com relação ao endereço

fornecido no campo de endereço

EE = A + (R)

O campo de endereço pode ter dois valores

A = Guarda o endereço de base

R = Guarda o conteúdo do deslocamento

ou o contrário

O registrador pode ser um registrador default

(economia de bits na instrução)

Endereçamento por deslocamento

Endereçamento por deslocamento

Endereçamento por deslocamento

Os três usos mais comuns do endereçamento por

deslocamento são:

Endereçamento relativo (PC)

Endereçamento registrador-base

Endereçamento indexado

Endereçamento relativo

Uma versão do endereçamento indexado

R = Contador de programa, PC

EE = A + (PC)

O operando se encontra deslocado do valor

indicado no campo de endereço da instrução, com

relação ao endereço apontado por PC

Endereçamento registrador-base

Idêntico ao endereçamento por deslocamento

A contém o deslocamento

R contem o endereço de base

R pode ser implícito ou explícito

Ex. registradores de segmento no 80x86

Endereçamento indexado

A = Base

R = Deslocamento

EE = A + R

Uso em acesso a arrays

EE = A + R

R++

Indexação indireta

Pós-indexação: indexação feita depois do

endereçamento indireto

EE = (A) + (R)

Pré-indexação: indexação feita antes do

endereçamento indireto

EE = (A+(R)

Endereçamento de pilha

O operando é o topo da pilha

Ex.

ADD - desempilha e adiciona os dois itens do topo

da pilha.

![aula10-EXTRA-Arqs43210Ends [Modo de Compatibilidade]](http://s1.studylibpt.com/store/data/001011244_1-a6aa2e8b625601e12d5149ac51d4d875-300x300.png)