(11) Número de Publicação:

PT 105349

(51) Classificação Internacional:

(12) FASCÍCULO DE PATENTE DE INVENÇÃO

(22) Data de pedido: 2010.10.19

(73) Titular(es):

(30) Prioridade(s):

INESC-ID INSTITUTO DE ENGENHARIA DE

SISTEMAS E COMPUTADORES INVESTIGAÇÃO

E DESENVOLVIMENTO DE LISBOA

RUA ALVES REDOL 9, APARTADO 13069

1000-029 LISBOA

(43) Data de publicação do pedido: 2012.04.19

PT

(72) Inventor(es):

MOISÉS SIMÕES PIEDADE

PT

SARA CRISTINA VICENTE CATALÃO

PT

JORGE MANUEL DOS SANTOS RIBEIRO

FERNANDES

PT

RODRIGO MADRUGO PIEDADE

PT

TIAGO MIGUEL LOPES MARTA DA COSTA

PT

(74) Mandatário:

(54) Epígrafe: MÉTODO DE CONTROLO DA QUEDA DE TENSÃO OU DA RESISTÊNCIA DE INTERRUPTORES

ELECTRÓNICOS

(57) Resumo: A PRESENTE INVENÇÃO CONSISTE EM UM NOVO MÉTODO DE CONTROLO DE INTERRUPTOR E

COMANDADOS DIGITALMENTE, BASEADOS EM DISPOSITIVOS ELECTRÓNICOS (TRANSÍSTORES, VÁLVULAS

ELECTRÓNICAS, ETC.), E NA UTILIZAÇÃO DA TENSÃO DE DESVIO DE UM AMPLIFICADOR DIFERENCIAL PARA

REALIZAR UMA FONTE DE TENSÃO DE REFERÊNCIA FLUTUANTE. O NOVO MÉTODO CONSISTE EM INSERIR

O INTERRUPTOR COMANDADO NUMA MALHA DE REALIMENTAÇÃO CONTROLADA PELO SINAL DE COMANDO

DIGITAL E POR UM SINAL DE ERRO, QUE AJUSTA CONSTANTEMENTE A TENSÃO DE COMANDO DO

DISPOSITIVO ELECTRÓNICO QUE MATERIALIZA O INTERRUPTOR, DE MODO A MANTER A QUEDA DE

TENSÃO CONSTANTE. SEM PERDA DE GENERALIDADE APLICA-SE O NOVO MÉTODO A INTERRUPTORES

MOS (REALIZADOS COM TRANSISTORES MOS DE CANAL N OU DE CANAL P) OU INTERRUPTORES CMOS

(REALIZADOS COM TRANSISTORES MOS DE CANAL N E DE CANAL P).

Resumo

Método de Controlo da Queda de tensão ou da

Resistência de Interruptores Electrónicos

A

presente

invenção

consiste

controlo

de

interruptores

baseados

em

dispositivos

num

novo

electrónicos.

electrónicos

Os

método

de

interruptores

têm

dois

estados:

“ligado” e “desligado”. A resistência no estado de ligado

varia

com

a

intensidade

da

corrente

que

atravessa

o

interruptor e com as tensões de comando entre o terminal de

comando e os outros terminais do interruptor. A variação de

resistência introduz distorção indesejada nos sinais.

O

método

interruptor

aqui

comandado

proposto

numa

consiste

malha

de

em

inserir

o

realimentação

controlada pelo sinal de comando digital e por um sinal de

erro,

que

ajusta

constantemente

a

tensão

de

comando

do

dispositivo electrónico que materializa o interruptor, de

modo a manter a queda de tensão constante.

Descrição

Método de Controlo da Variação da Resistência de

Interruptores Realizados com Dispositivos Electrónicos

Domínio Técnico da Invenção

Engenharia Electrotécnica – Medição e Processamento de

Sinal.

Estado da Arte

Enquadramento da invenção: Nota introdutória

A presente invenção consiste num novo método actuação

de

interruptores

electrónicos

de

modo

a

controlar

e

estabilizar o valor da queda de tensão no interruptor, ou o

valor da sua resistência interna, reduzindo assim os erros

introduzidos pelo interruptor.

Na Figura 1 pode ver-se a situação comum em que um

interruptor electrónico SW, comandado pela tensão VC pode

passar

de

um

estado

desligado

(“OFF”),

com

resistência

infinita (1), para o estado de ligado (“ON”) com uma dada

resistência RSW (2), percorrido pela corrente II.

Em

todas

as

implementações

práticas

conhecidas

do

interruptor electrónico SW, a resistência RSW do dispositivo

quando ligado varia com as tensões aos terminais e com a

intensidade da corrente II que atravessa o interruptor. Na

Figura

2

ilustra-se,

sem

perda

de

generalidade,

uma

implementação típica com um transístor MOS (ou MOSFET Metal Oxide Semiconductor Field Effect Transistor) de canal

N (NMOS)(3), cuja resistência de passagem pode ser quase

infinita

se

o

transístor

funcionar

na

região

de

corte

1

VGS < Vt sendo Vt a tensão de limiar (threshold), ou pode ser

reduzida se funcionar na região de tríodo VDS < VGS - Vt. A

resistência

do

transístor

na

região

de

tríodo

depende

essencialmente da tensão VGS, sendo variável e dependente da

tensão de comando VC, da tensão VI e da corrente II que

atravessa o dispositivo, dependências que introduzem erros

de não linearidade no sinal.

As

duas

utilizações

mais

comuns

deste

tipo

de

interruptor electrónico são: Caso I) Transmissão de sinal

em

tensão

-

o

interruptor

funciona

como

elemento

de

transmissão da tensão VI para o porto VS - ou, Caso II)

Leitura do valor de uma resistência (sensor resistivo, por

exemplo) RS – o interruptor permite aceder a um sensor

resistivo RS, através da aplicação da corrente de excitação

II-.

No

caso

I

obtém-se:

vS=vI×RSW/(RSW+RS)

em

que

há

a

introdução de um erro de não linearidade pelo facto de RSW

não ser constante e variar com o sinal vI, ver Figura 2. No

caso

II,

obtém-se

o

valor

da

resistência

do

sensor

RS

através de VI=II(RS+RSW) que também apresenta um erro de não

linearidade pelo facto de RSW variar com II e com o próprio

valor RS do sensor. Em ambos os casos os erros podem ser

minimizados se o interruptor electrónico for dimensionado

de modo a ter uma resistência desprezável face ao valor da

resistência RS minimiza-se, assim, os efeitos do problema

mas não o resolve.

Os processos conhecidos na literatura para resolver

estes dois problemas são essencialmente desenvolvidos para

a

tecnologia

tecnologias

de

integração

monolítica

ou

(Complementary

MOS

CMOS

de

sistemas

Metal

com

Oxide

Semiconductor Field Effect Transistor), onde não é prático

nem barato sobredimensionar os interruptores electrónicos

(transístores)

circuito

que

integrado

corresponde

e

o

seu

a

custo.

aumentar

É

a

área

conhecido

que

de

a

colocação em paralelo de um transístor MOS de canal N com

2

um transístor MOS canal P, cujas portas são actuadas por

sinais

lógicos

complementares,

conduz

a

um

interruptor

electrónico com resistência equivalente menos variável do

que quando se usa apenas um tipo de transístor. No entanto

a redução da variação só sucede num intervalo restrito de

valores

de

tensão

desemparelhamento

e

dos

não

dois

resolve

problemas

transístores.

Assim,

de

é

de

esperar variações de resistência de 20% a 50% na gama de

utilização do dispositivo que conduzem a erros graves em

aplicações de alta precisão.

As

técnicas

alternativas

desenvolvidas

nos

últimos

anos baseiam-se em circuitos de condensadores comutados, em

que

se

amostra

e

armazena

periodicamente

a

tensão

em

condensadores, que depois são inseridos no circuito como

fontes de tensão para manter constante a tensão VGS, do

interruptor electrónico, mantendo assim a sua resistência

constante. Estas técnicas pressupõem que o interruptor é

comutado

“OFF”

periódica

e

originando,

discreto

no

rapidamente

assim,

tempo

a

um

entre

sistema

trabalhar

com

o

estado

de

“ON”

e

processamento

sinais

analógicos.

Exemplos deste tipo de sistemas podem ser consultados nas

referências

circuito

[1-4]

que

representado

aqui

na

analisamos

Figura 3

sumariamente.

da

referência

O

[1],

conhecido por “bootstrapped switch” tem, durante o estado

“OFF”

do

interruptor,

condensador

S3,

auxiliar

S4

é

e S5

carregado

no

estado “ON”

com

a

e

tensão

o

de

alimentação do circuito, VDD. No estado “ON” do interruptor

SW, S1 e S2 estão “ON” e o condensador, usado como uma

bateria

auxiliar

de

tensão

contínua,

eleva

a

tensão

da

porta do interruptor acima da tensão de alimentação VDD,

ficando

o

interruptor

resistência

RSW

fica

com

apenas

VGS = VDD

constante;

dependente

das

assim

variações

a

da

tensão limiar Vt, que como se sabe depende da tensão do

substrato

do

transístor.

A

dependência

com

a

tensão

de

3

substrato pode ser minimizada pela técnica denominada de

“transistor

replica”

[2]

que

adiciona

um

amplificador

operacional e um transístor auxiliar para gerar a tensão

adicional [2]. Esta técnica exige tensões de controlo do

interruptor superiores à tensão de alimentação do circuito

o

que

introduz

fadiga

no

circuito

reduzindo

a

sua

fiabilidade e longevidade. Em [3] foi proposto um método

que reduz a distorção introduzida pelo interruptor sem que

a tensão de porta do interruptor ultrapasse a tensão máxima

de alimentação. As técnicas anteriormente referidas supõem

que VI ou VS são fontes de tensão ideais (com resistência

interna nula) das quais retiram alguma corrente pelo que

podem conduzir à situação em que II

IS (ver Figura 1).

As técnicas anteriores têm outra limitação quando a

tensão VS é maior do que VI ou seja o transístor, que é

simétrico,

troca

a

fonte

com

o

dreno;

isto

acontece

frequentemente em circuitos de amostragem e retenção. Este

problema pode ser reduzido pelo circuito de [4] em que a

tensão de controlo do interruptor é obtida a partir da

maior das tensões, VI ou VS, determinada por um circuito

comparador de tensão.

Qualquer das propostas conhecidas na literatura para

reduzir

a

variação

electrónicos

ficando

esta

fabrico

ou

não

da

estabiliza

dependente

do

resistência

o

das

dos

valor

desta

variações

do

cancelamento

imperfeito

interruptores

resistência

processo

dos

de

erros

anteriormente referidos. Algumas das técnicas também não

asseguram que II = IS pois os circuitos de controlo requerem

alguma corrente para funcionarem.

A invenção aqui proposta utiliza técnicas de controlo

com realimentação para reduzir as variações da resistência

dos interruptores, podendo ser aplicada, por si só, ou para

complementar as técnicas anteriormente referidas tornandoas mais precisas e controladas.

4

Descrição sumária das figuras

A invenção aqui proposta é descrita sobre um conjunto de

figuras que aqui se referem sumariamente. Na Figura 1 está

representado

um

interruptor

digitalmente,

sendo

na

electrónico

Figura

2

comandado

representado

numa

implementação com um transístor NMOS. A Figura 3 apresenta

um

interruptor

electrónico

com

tensão

constante

aos

terminais e é a figura principal descrita.

A realização prática do bloco de amplificador operacional é

introduzida

com

a

Figura

4

apresentando

o

diagrama

de

amplificador operacional com tensão de desvio e um exemplo

de esquema eléctrico do andar de entrada diferencial.

Na Figura 5 é apresentado um esquema de controlo de tensão

num interruptor CMOS complementar e por último na Figura 6

são apresentados resultados de simulação da variação de

resistência de diferentes exemplos de interruptores CMOS.

Descrição detalhada da invenção

O

circuito

electrónico

fonte

de

SW

da

(4)

tensão

(transístores

Figura 3

de

um

VE

acrescenta

amplificador

(6)

e

passagem)

os

ao

interruptor

operacional

interruptores

auxiliares

S1

(5)

uma

analógicos

e

S2

(7)

controlados pelo sinal lógico VC (8) e o seu complemento

lógico

(9)

obtido

pelo

inversor

lógico

(10).

Quando

VC = ”0” a porta do interruptor SW está ligada à massa e o

transístor SW fica no estado “OFF” (alta resistência) não

permitindo a passagem de VI ou de II para o porto VS. Com

VC = “1”

a

porta

do

transístor

fica

ligada

à

saída

do

amplificador operacional que tenta manter a tensão VSW = VE,

à custa do seu elevado ganho de tensão, da retroacção e da

tensão de referência VE. Obtém-se VSW = RSWII = VE se o ganho

5

de tensão, A, do amplificador operacional for infinito.

Admitindo que o amplificador operacional não tem corrente

de

entrada,

para

um

dado

valor de

II

a

resistência

do

interruptor é ajustada automaticamente ao valor RSW = VE/II.

Para o circuito funcionar com II > 0, deve ter-se VE > 0 e a

corrente

que

atravessa

SW

deve

satisfazer

a

condição:

II < VE / RSW_min. Para o circuito funcionar com II < 0, deve

ter-se VE < 0 e a corrente que atravessa SW deve satisfazer

a condição: II > VE / RSW_min.

A invenção aqui proposta admite as situações de VE ser

constante (positiva ou negativa) ou ser variável com um

dado sinal de controlo. Se VE for constante o circuito da

Figura 3

mantém

interruptor

a

(4)

tensão

constante

independentemente

aos

da

terminais

corrente

que

do

o

atravessa, através da variação automática da resistência do

interruptor

interesse

SW

para

prático

a

o

valor

situação

RSW = VE /II > RSW_min.

em

que

a

tensão

Tem

VE

é

proporcional à própria corrente II, isto é: VE = RD×II, em

que

a

constante

RD > RSW_min.

Neste

caso

obtém-se

RSW = VE /II = RD > RSW_min, que permite estabilizar o valor da

resistência do interruptor num valor constante independente

da corrente que o atravessa. Assim, o circuito da Figura 3

pode

funcionar

tanto

como

estabilizador

da

tensão

aos

terminais do interruptor SW como estabilizador do valor da

resistência do interruptor SW.

Exemplos de Aplicação:

Se a resistência do interruptor SW for constante a

relação

entre

VI

e

VS

é

a

de

um

divisor

de

tensão

potenciométrico entre RSW e RS e desde que RS seja constante

o sinal é transmitido com atenuação mas sem deformação não

linear.

CASO I- Medição do valor de um sensor resistivo.

6

Nesta aplicação força-se em RS, através do interruptor

SW,

uma

corrente

II

constante

ou

com

uma

componente

alternada sobreposta, e obtém-se a tensão de entrada VI que

contém a informação sobre o valor da resistência RS ou da

sua variação

RS (no caso de esta ser um sensor resistivo).

Considerando um sensor RS cuja resistência varia de

acção

de

qualquer

fenómeno

físico,

isto

é:

RS por

RS = RS0+ RS,

obtém-se a equação

VI RSW I I

RS 0 I I

RS I I

VE

RS 0 I I

RS I I

constante

onde a tensão VI, é isenta de erros pois a primeira parcela

é constante e independente do valor da variação quer da

resistência do sensor quer da resistência do interruptor,

RSW, mesmo quando a corrente de leitura tem uma componente

alternada sobreposta a uma componente contínua.

CASO II- Transmissão de um sinal do porto VI ao porto

VS.

Nesta

aplicação

pretende-se

que

interruptor

electrónico permita que o porto VS aceda ao sinal de tensão

do porto VI (situação comum em sistemas de multiplexagem

electrónica de áudio e de vídeo analógicos). Considera-se

que existe uma componente contínua em VS e que se pretende

aceder

à

componente

variável

sobreposta

(áudio,

vídeo,

etc.). Sendo

,

o circuito da Figura 3 mantém a tensão VSW = VE, constante e

independente das variações de RSW, RS, VI e VS. Deste modo a

tensão de saída VS é igual a VI a menos de uma grandeza

constante

VE

reduzindo-se

que

a

pode

distorção

ser

e

arbitrariamente

erros

resultantes

pequena,

quer

de

7

variações de RSW, quer de RS, quer da própria componente

variável de VS.

No

circuito

da

Figura

3

a

tensão

VE

(6)

pode

ser

implementada pela tensão de desvio VOS (11) do amplificador

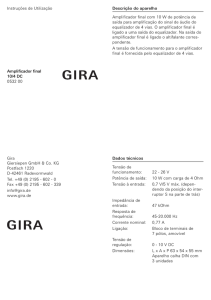

operacional (12) como se representa na Figura 4.

Na

Figura

eléctrico

4

pode

genérico

concretizado

com

um

ainda

de

um

observar-se

um

amplificador

amplificador

esquema

operacional

diferencial

de

entrada

realizado, sem qualquer perda de generalidade, com dois

transístores MOS de canal N, duas resistências de carga RD,

uma fonte de corrente constante ID (13) e um amplificador

de tensão A2 (14).

Com v1 = v2 e M1 = M2 (transístores iguais) ter-se-ia

iD1=iD2 e como consequência vO = 0, isto é, o amplificador

teria VOS = 0.

Para

gerar

uma

tensão

VOS

não

nula

pode

usar-se

qualquer mecanismo que desequilibre o circuito.

A

presente

invenção

é

particularmente

concretizável

usando circuitos com transístores de efeito de campo JFET

(Junction Field Effect Transistor) ou MOSFET (Metal Oxide

Semiconductor Field Effect Transistor) que têm correntes de

porta

(gate)

praticamente

nulas,

garantindo

assim

que

II = IS.

Aplicação do método proposto

A aplicação do amplificador operacional com tensão de

desvio

controlada

VE,

num

circuito

de

estabilização

da

tensão aos terminais de um interruptor analógico pode ser

exemplificada no circuito da Figura 3. A tensão VE (6) pode

ser

realizada

pela

tensão

de

desvio

do

amplificador

8

conforme

foi

já

referido.

A

tensão

de

comando,

VC,

do

interruptor analógico SW, actua como variável lógica sendo

o seu valor lógico complementado pelo inversor. Quando VC

=”1” o interruptor S2 está fechado e o interruptor S1 está

aberto.

O

amplificador

tensão

sobre

o

A

controla

interruptor

o

no

valor

valor

da

VE

queda

de

previamente

definido, usando realimentação negativa. A gama de controlo

e estabilização da tensão VSW depende do valor da corrente

I1

e

da

resistência

(RSW_min)

mínima

do

interruptor

SW

devendo cumprir-se sempre a relação RSW_min×I1<= VE, isto é

deve ter-se I1<= VE/RSW_min.

Quando

VC =”0”

interruptor

S2

o

está

interruptor

aberto.

S1

Neste

está

fechado

caso,

a

e

saída

o

do

amplificador não tem acesso à porta do transístor MOS -que

implementa o SW- que fica ligada à massa colocando-o no

estado “OFF” (alta impedância / desligado).

Na prática sabe-se que os interruptores electrónicos

com

tecnologia

tensão

de

MOS

para

alimentação

ou

comutarem

da

tensões

massa,

próximas

precisam

de

da

ser

constituídos por um par de transístores, um de canal P,

SW P, e outro de canal N, SW N, colocados em paralelo, mas

cujas

portas

complementares.

são

controladas

Como

se

por

representa

tensões

na

lógicas

Figura 5,

para

controlar este tipo de interruptor (16), de acordo com a

presente invenção, é necessário dispor de um amplificador

operacional com entrada e saída diferencial (17). É suposto

usar

um

esquema

de

comutações

das

duas

saídas

do

amplificador operacional, semelhante ao usado na Figura 3,

activadas por um sinal de controlo digital.

O desempenho do método proposto nesta invenção pode

ser observado pelos resultados experimentais apresentados

na

Figura 6

que

dizem

respeito

ao

controlo

de

interruptores, de canal P, de canal N e ainda da associação

9

canal P/canal N em paralelo, com e sem a utilização da

invenção aqui proposta. Apresentam-se resultados ilustrando

a

variação

da

resistência

de

vários

interruptores,

dimensionados para terem uma resistência mínima de cerca de

50 ohms, com a tensão de entrada vIN, para a passagem de

corrente de 1 mA.

A legenda das curvas representadas na Figura 6 é a

seguinte:

(18)

-

Curva

de

variação

da

resistência

de

um

resistência

de

um

transístor canal N, com controlo;

(19)

-

Curva

de

variação

da

transístor canal P, com controlo;

(20) - Curva de variação da resistência de transístor

canal N em paralelo com transístor de canal P, com

controlo;

o A resistência de SW ON varia apenas entre 105,2

ohms e 110,5 ohms;

(21)- Curva de variação da resistência de transístor

canal N em paralelo com transístor de canal P, sem

controlo;

o A

resistência

de

SW

varia

entre

70.97

ohms

e

97.26 ohms;

Referências

[1].

J.

Steensgaard,

”Bootstrapped

low-voltage

analog switches,” IEEE International Symposium

on

Circuits

and

Systems,

Volume

2,

pp.29-

32,May 30 – June 2, 1999.

10

[2].

A. K. Ong, V. I. Prodanov, and M. Tarsia, “A

method

for

reducing

resistance

of

International

a

the

MOS

variation

sampling

Symposium

on

in

“on”

switch,”

IEEE

Circuits

and

Systems, Volume5, pp.437 – 440, May 2000.

[3].

Galhardo,

J.

Linearization

High

Swing

Goes,

N.

Technique

CMOS

Paulino,

for

Switches

“Novel

Low-Distortion

with

improved

Reliability”, IEEE International Symposium on

Circuits

and

Systems

(ISCAS

2006),

pp.2001-

Hung,

“A

2004, May 2006

[4].

Chun-Yueh

Yang,

Chung-Chih

low-

voltage low-distortion MOS sampling switch”,

International

Symposium

on

Circuits

and

Systems (ISCAS 2005), Volume 4, pp.3131-3134,

May 2005

Lisboa, 7 de Julho de 2011

11

Reivindicações

1. Novo método de controlo de interruptores electrónicos

com recurso a uma malha de controlo da queda de tensão

no interruptor caracterizado por:

a) Estabilização do valor da tensão (ou resistência)

no estado de ligado;

b) Manutenção

de

circuito

aberto

no

estado

de

desligado.

Lisboa, 7 de Julho de 2011

1

1

vI

vI

II

SW

vC

II

RSW

vS

IS

vC

vS

IS

RS

2

RS

Figura 1

vI

vC

RS

3

II

RSW

vS

IS

R SW

, se V GS

VC

R SW

VS

1

2 k V GS

VC

Vt

Vt

0

Vt

, se 0

VI

V DS

V GS

Vt

Vt

Figura 2

1

9

10

8

vI

vC

vC

S1

VSW

RSW

S2

vS

IS

RS

5

4

II

+

-A

VE

6

7

Figura 3

VDD

15

14

RD

12

V1

+

-A

V2

RD

+

-A2

VO

VO

V1

VOS

M1

M2

IDC

11

13

VSS

V2

Figura 4

2

16

vI

SW_N

VON

VOS

SW_P

+

-

17

-

A+

VOP

vS

Figura 5

Figura 6

3