Trabalho Prático

Engenharia de Computação I

Prof. Dr. Fabian Vargas

Datas de Apresentação:

Início de julho.

Apresentação: Na data da apresentação, o trabalho deverá ser enviado por email para [email protected]. A

apresentação deverá ser feita por todos os membros do grupo, em sala de aula, com PC e

canhão multimídia.

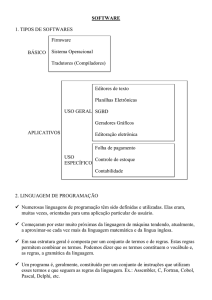

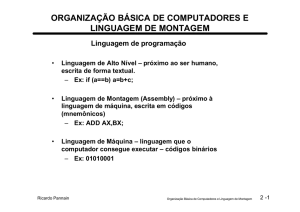

Descrição dos trabalhos:

Implementar em linguagem C a descrição funcional de um Microprocessador

Pipeline e seu Compilador Assembler. Um grupo deverá implementar o

processador, enquanto que o outro grupo implementará o compilador. Abaixo

descrevem-se as características principais do sistema:

a) De arquitetura baseada em 16 bits de dados, 16 bits de endereços, e 21 bits para palavras de

instruções.

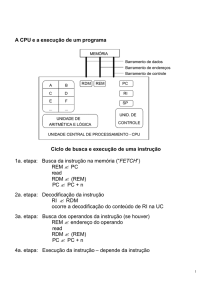

b) Pipeline de 5 estágios. Cada estágio é executado em 1 único ciclo de relógio. Implementar os 4

Registradores do Pipeline (RP): IF/ID, ID/EX, EX/ME, ME/WB.

c) Arquitetura Harvard: memórias de dados e de instruções (2 cachês, cada uma com capacidade

para armazenar 100 dados e 100 instruções, respectivamente). Os controladores destas caches

são independentes.

d) Registradores:

Uso Geral (16 bits): R1, R2, ... , R7.

Registrador Temporário: Rt.

e) Registradores de Controle do processador (16 bits):

Flags: Zero, Números Positivos, Números Negativos, Overflow.

Program Counter: PC.

Instruction Register: IR.

f)

Unidade de Predição de Desvio. Existe uma Tabela de Desvios - TD (100 posições acessadas

por PC contendo um flag que indica se desvio “V” ou “F” e endereço de desvio). Esta tabela é

atualizada dinamicamente pelo processador durante a execução do código.

g) O processador possui HW para verificação em tempo real da ocorrência das seguintes

exceções no código: a) Divisão por zero; b) Decodificação do código de uma instrução

inexistente; c) Acesso a um endereço de memória (de dados ou instruções) inexistente ou

protegido.

h) O compilador executa a análise do código visando a reordenação de suas instruções. O objetivo

é minimizar/eliminar os problemas de dependência de instruções em máquinas pipeline. A

janela considerada pelo compilador para reordenar uma dada instrução i em processamento é

de 3 instruções anteriores e de 3 instruções posteriores à ela, isto é: [i – 3, i, i+ 3]. No caso de

não conseguir eliminar completamente a dependência de instruções no código, o compilador

insere instruções de “Nop”.

i)

O compilador decodifica as instruções Assembler do usuário “Mul” e “Div” e as converte em

uma seqüência de outras instruções, também em Assembler, que executam os Algoritmos de

Booth e o de Divisão, respectivamente. Após esta conversão, o compilador passa a gerar o

código objeto para o processador.

j)

O compilador decodifica as instruções Assembler do usuário “Adm”, “Adr”, “Sum”, e “Sur” e as

converte em uma seqüência de outras instruções, também em Assembler, que executam as

operações de soma e subtração entre um dado contido em memória e outro armazenado no

banco de registradores do processador, respectivamente. Após esta conversão, o compilador

passa a gerar o código objeto para o processador.

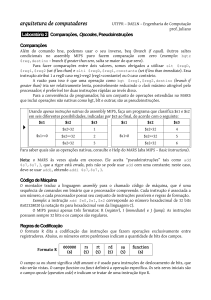

k) São 3 os possíveis formatos das instruções do processador:

De Registrador para Registrador (Tipo R), Formato “00”:

Formato

Primeiro Operando Segundo Operando Destino

Shifts

20

19 18

16 15

13 12

10 9

6

De Acesso à Memória (Tipo M), Formato “01”:

Formato

Registrador

Origem/Destino

20

19 18

16 15

Endereço do dado na memória

19

18

16

15

Tipo de instrução

6

De Desvios Condicionais (Tipo D), Formato “10”:

Formato

Primeiro Operando Segundo Operando

20

Tipo de instrução

5

0

13

“Base” do Endereço

de Desvio

12

6

De Desvios Incondicionais (Tipo J), Formato “11”:

Formato

“Base” para o Endereço de Desvio

20

19

5

0

Tipo de instrução

5

0

0

l)

Linguagem Assembler do processador:

Instrução

Add Reg1, Reg2, RegDst

Sub Reg1, Reg2, RegDst

Sll Reg.Orig, shifts

Srl Reg.Orig, #shifts

Sla Reg.Orig, shifts

Sra Reg.Orig, shifts

And Reg1, Reg2, RegDst

Or Reg1, Reg2, RegDst

Xor Reg1, Reg2, RegDst

Not Reg.Orig.

Inv Reg.Orig

Nop

Cmp Reg1, Reg2, RegDst

Código

“000000”

“000001”

“000010”

“000011”

“000100”

“000101”

“000110”

“000111”

“001000”

“001001”

“001010”

“001011”

“001100”

Formato

15

Ldw Reg.Dest., Mem[end]

Stw Reg.Orig., Mem[end]

16

1

Comentários

R

Atualiza todos os flags.

R

Atualiza todos os flags.

R

Shift left logic (acrescenta 0’s)

R

Shift right logic (acrescenta 0’s)

R

Shift left arithmetic (mantém lsb)

R

Shift right arithmetic (mantém msb)

R

Não atualiza flags.

R

Não atualiza flags.

R

Não atualiza flags.

R

Inverte o conteúdo de Reg.Orig.

R

Complementa de dois o conteúdo de Reg.Org

R

No Operation.

R

Compara os conteúdos de Reg1 e Reg2. Atualiza flags: Zero,

Nos. Positivos, Nos. Negativos

“001101”

“001110”

M

Load Word. Reg.Dst.

M

Store Word. Mem [end]

Beq Reg1, Reg2, EndBase

“001111”

D

17

Bnq Reg1, Reg2, EndBase

“010000”

D

18

Bla Reg1, Reg2, EndBase

“010001”

D

19

Blo Reg1, Reg2, EndBase

“010010”

D

Branch Equal. PC

“PC + EndBase” se Reg1

Atualiza flags: Zero.

Branch Not Equal. PC

“PC + EndBase” se Reg1

Atualiza flags: Zero.

Branch Larger. PC

“PC + EndBase” se Reg1

Atualiza flags: Nos. Positivos.

Branch Lower. PC

“PC + EndBase” se Reg1

Atualiza flags: Nos. Negativos.

20

Jmp EndBase

“010011”

J

PC

21

Mul Reg1, Reg2, RegDst

---

---

22

Div Reg1, Reg2, RegDst

---

---

23

Adm Reg, Mem[end]

---

---

Instrução especial. Utilizada pelo programador Assembler e

manipulada pelo compilador, que a traduz, segundo o

Algoritmo de Booth, em uma seqüência de outras instruções

Assembler..

Instrução especial. Utilizada pelo programador Assembler e

manipulada pelo compilador, que a traduz, segundo o

Algoritmo de Divisão, em uma seqüência de outras instruções

Assembler.

Instrução especial. Utilizada pelo programador Assembler para

somar dois operandos, sendo que um reside na memória e

outro no banco de registradores do processador. O resultado

desta operação volta para o mesmo endereço de memória

(Mem[end]

Reg. + Mem[end]).

Esta instrução Assembler é manipulada pelo compilador, que a

traduz em uma seqüência de outras instruções Assembler..

Instrução especial. Utilizada pelo programador Assembler para

somar dois operandos, sendo que um reside na memória e

outro no banco de registradores do processador. O resultado

desta operação permanece no mesmo registrador de origem

(Reg

Reg + Mem[end]).

Esta instrução Assembler é manipulada pelo compilador, que a

traduz em uma seqüência de outras instruções Assembler..

Instrução especial. Utilizada pelo programador Assembler para

subtrair dois operandos, sendo que um reside na memória e

outro no banco de registradores do processador. O resultado

desta operação volta para o mesmo endereço de memória

(Mem[end]

Reg. - Mem[end]).

Esta instrução Assembler é manipulada pelo compilador, que a

traduz em uma seqüência de outras instruções Assembler..

Instrução especial. Utilizada pelo programador Assembler para

subtrair dois operandos, sendo que um reside na memória e

outro no banco de registradores do processador. O resultado

desta operação permanece no mesmo registrador de origem

(Reg

Reg - Mem[end]).

Esta instrução Assembler é manipulada pelo compilador, que a

traduz em uma seqüência de outras instruções Assembler..

2

3

4

5

6

7

8

9

10

11

12

13

14

Adr Reg, Mem[end]

---

---

25

Sum Reg, Mem[end]

---

---

26

Sur Reg, Mem[end]

---

---

Reg.Orig.

= Reg2.

!= Reg2.

> Reg2.

< Reg2.

“PC + EndBase”, incondicionalmente.

24

Mem [end]

![Aula 06 - Daves - exercicios [Modo de Compatibilidade]](http://s1.studylibpt.com/store/data/001144987_1-66893eaef68e852efe81e8f280104c23-300x300.png)