Arquiteturas de Computadores

Programa de Pós-Graduação

em Ciência da Computação

Norian Marranghello – Março/Junho de 2006

Plano da aula

§

§

§

§

Conceitos de pipelining

Determinação do ciclo

Wave pipelining

Considerações sobre custo

Norian Marranghello – 2006 – Arquiteturas de Computadores

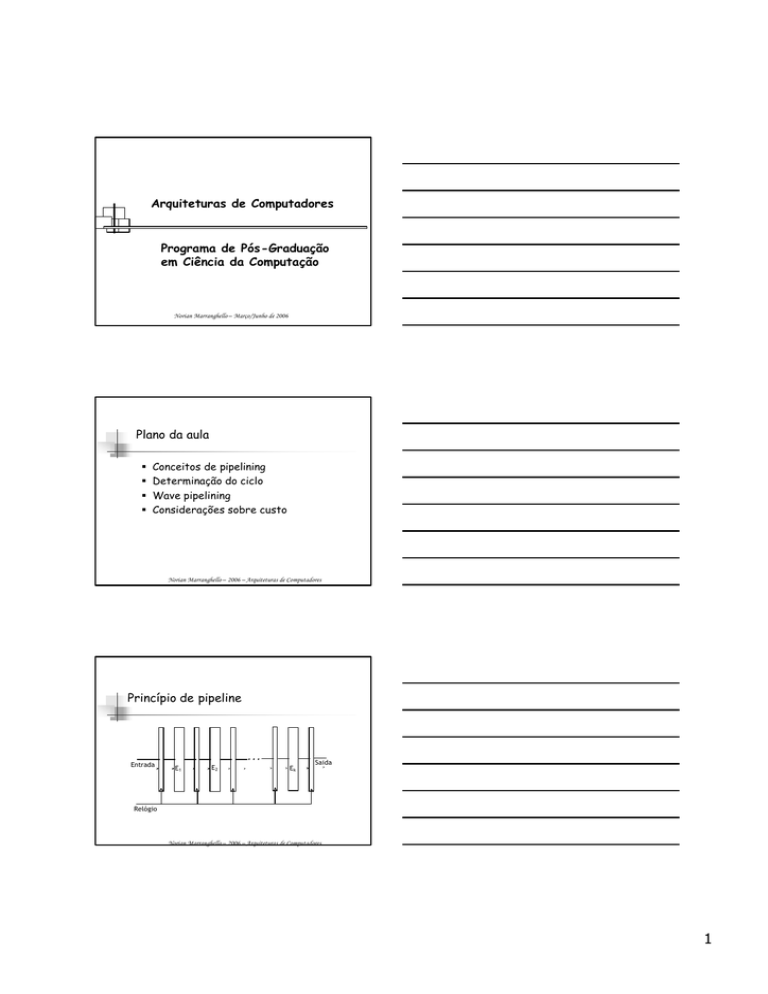

Princípio de pipeline

Entrada

E1

E2

Ek

Saida

Relógio

Norian Marranghello – 2006 – Arquiteturas de Computadores

1

RESULTADO 8

RESULTADO 7

RESULTADO 6

RESULTADO 5

RESULTADO 4

RESULTADO 3

RESULTADO 2

Espaço

RESULTADO 1

Diagrama espaço x tempo

T41 T42 T43 T44 T45 T46 T47 T48

E4

E3

T31 T32 T33 T34 T35 T36 T37 T38

E2

T21 T22 T23 T24 T25 T26 T27 T28

E1 T 1 T 2 T 3 T 4 T 5 T 6 T 7 T 8

1

1

1

1

1

1

1

1

1

2

3

4

5

6

7

8

9

10

Tempo

(ciclos)

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

§ Fases:

§

§

§

§

Busca de instrução

Decodificação de instrução

Busca de dados

Execução de instrução

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

§ Busca de instrução

§

§

§

§

§

REM ß CP

Decodifica REM

RDM ß M[REM]

RI ß RDM

CP ß inc[CP]

Norian Marranghello – 2006 – Arquiteturas de Computadores

2

Determinação do ciclo

§ Decodificação de instrução

§ Identificação do código de operação

§ Geração dos endereços dos dados

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

§ Busca de dados

§

§

§

§

REM ß endereços dos dados

Identificação dos dados desejados

RDM ß M[REM]

Rx ß RDM

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

§ Execução de instrução

§ Ac ß

f {ULA}

§ Ry ß Ac

Norian Marranghello – 2006 – Arquiteturas de Computadores

3

Determinação do ciclo

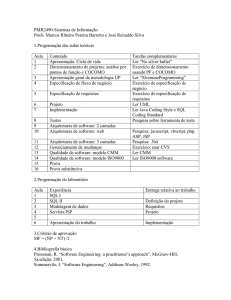

Fase Micro-operação Tempo (ns)

BI

REMßC P

3

Decodifica REM

6

RDMßM[REM]

10

RIßRDM, inc(CP)

3

DI

Id. Cod . Oper.

12

Gera Endereço

9

BD

REMßEnd.Dado

3

Decodifica REM

6

RDMßM[REM]

10

RxßRDM

3

EX

Acßf{ULA}

22

RyßAc

3

Total

90

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

§ κ = 0,05

§ SC = 4

§ i = 0,2

NEot =

NEot =

0,8 (1,05) 90

0,2 x 4

=

(1 - i) (1 + κ) T

i SC

94,5

≈ 9,72

=9

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

§Um relógio à períodos iguais para as fases

§ Nem tudo pode ser dividido

§ Quantização

Norian Marranghello – 2006 – Arquiteturas de Computadores

4

Determinação do ciclo

§

§

§

§

BI à 22ns

DI à 12ns a 21ns

BD à até 22ns

Ex à 25ns

§ T(NEot) = 10ns

§ T min = 10ns x 1,05 + 4ns = 14,5ns

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

§ Eficiência:

§ 90ns à 11MHz

§ 14,5ns à 70MHz

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

Fase

BI

DI

BD

EX

Total

Micro-operação

Tempo (ns)

REMßC P

Decodifica REM

RDMßM[REM]

RIßRDM, inc(CP)

3

6

10

3

Id. Cod . Oper.

Gera Endereço

12

9

REMßEnd.Dado

Decodifica REM

RDMßM[REM]

RxßRDM

3

6

10

3

Acßf{ULA}

RyßAc

22

3

9ns

10ns

6ns

9ns

9ns

10ns

8ns

10ns

10ns

90

Norian Marranghello – 2006 – Arquiteturas de Computadores

5

Determinação do ciclo

Fase

BI

DI

BD

EX

Micro-operação

Tempo (ns)

REMßC P

Decodifica REM

RDMßM[REM]

RIßRDM, inc(CP)

3

6

10

3

Id. Cod . Oper.

Gera Endereço

12

9

REMßEnd.Dado

Decodifica REM

RDMßM[REM]

RxßRDM

3

6

10

3

Acßf{ULA}

RyßAc

22

3

Total

T min = 15ns x 1,05 + 4ns = 19,75ns ≈ 20ns

9ns

15ns

15ns

14ns

15ns

13ns

90

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

Fase

BI

DI

BD

EX

Micro-operação

Tempo (ns)

T min = 22,5ns x 1,05 + 4ns = 27,625ns ≈ 28ns

REMßC P

Decodifica REM

RDMßM[REM]

RIßRDM, inc(CP)

3

6

10

3

Id. Cod . Oper.

Gera Endereço

12

9

REMßEnd.Dado

Decodifica REM

RDMßM[REM]

RxßRDM

3

6

10

3

16ns

Acßf{ULA}

RyßAc

22

3

22ns

Total

22ns

21ns

90

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

Fase

BI

DI

BD

EX

Total

Micro-operação

Tempo (ns)

T min = 25ns x 1,05 + 4ns = 30,25ns

REMßC P

Decodifica REM

RDMßM[REM]

RIßRDM, inc(CP)

3

6

10

3

22ns

Id. Cod . Oper.

Gera Endereço

12

9

12ns

REMßEnd.Dado

Decodifica REM

RDMßM[REM]

RxßRDM

3

6

10

3

22ns

Acßf{ULA}

RyßAc

22

3

25ns

90

Norian Marranghello – 2006 – Arquiteturas de Computadores

6

Determinação do ciclo

14,50

E1

E2

E3

E4

E5

E6

E7

E8

E9

Total

1

0

4

1

1

0

2

0

0

9

-

-

-

37,5

19,75 10,75 4,75

4,75

5,75 4,75 6,75

27,625 5,625 6,625 11,625 5,625

-

-

-

-

-

29,5

30,25

-

-

-

-

-

40

8,25 18,25

8,25

5,25

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

D = {1/[1+(NE-1)i]} {1/[(1+k)T+SC]}

D1 = {1/[1+(9-1)0,2]} {1/[(1+0,05)10+4]} ≈ 26,5MIPS

D2 = {1/[1+(6-1)0,2]} {1/[(1+0,05)15+4]} ≈ 25,3MIPS

D3 = {1/[1+(4-1)0,2]} {1/[(1+0,05)22,5+4]} ≈ 22,6MIPS

D4 = {1/[1+(4-1)0,2]} {1/[(1+0,05)25+4]} ≈ 20,7MIPS

Norian Marranghello – 2006 – Arquiteturas de Computadores

Determinação do ciclo

D = {1/[1+(NE-1)i]} {1/[(1+k)T+SC]}

E1 à 12ns

E2 à 30ns

E3 à 15ns

E4 à 30ns

E5 à 19ns

D14 = {1/[1+(11-1)0,2]} {1/[(1+0,05)14+4]} ≈ 17,8MIPS

D17 = {1/[1+(8-1)0,2]} {1/[(1+0,05)17+4]} ≈ 19,1MIPS

Norian Marranghello – 2006 – Arquiteturas de Computadores

7

Intervalo

n

Voltamos em 20 minutos!

Norian Marranghello – 2006 – Arquiteturas de Computadores

Wave Pipelining

§ Princípio:

§ Trabalhar mais de um conjunto de dados no

mesmo segmento do pipeline.

dm a x

SC

dmin

dmin

Norian Marranghello – 2006 – Arquiteturas de Computadores

Wave Pipelining

d max=10u.t.

SC=2u.t.

d min =7u.t.

d min =8u.t.

∆t1 = 10–7+2 = 5u.t.

L1

d max=13u.t.

SC=2u.t.

∆t

∆t2 = 13–8+2 = 7u.t.

L2

L3

Norian Marranghello – 2006 – Arquiteturas de Computadores

8

Considerações sobre custo

§ Desempenho ⇔ Custo

§ Melhor projeto = menor custo/desempenho

§ Decisão do projetista ⇒ área

Norian Marranghello – 2006 – Arquiteturas de Computadores

Considerações sobre custo

§ Circuitos integrados

§

§

§

§

Defeitos no semicondutor

Rendimento do processo

Perdas na lâmina

Problemas de alinhamento

Norian Marranghello – 2006 – Arquiteturas de Computadores

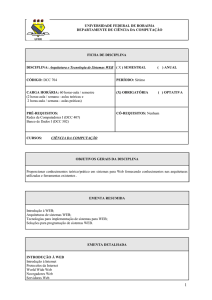

Considerações sobre custo

Chip

Chip

Chip

Chip

Chip

Chip

Chip

Lâmina perdida

Chip

Chip

Circuito perdido

Canais para corte

Defeitos na lâmina

Norian Marranghello – 2006 – Arquiteturas de Computadores

9

Considerações sobre custo

§ Tamanho padrão de referência: λ

λ

Norian Marranghello – 2006 – Arquiteturas de Computadores

Considerações sobre custo

§ rbe ⇒ register bit equivalent

§ registrador equivalente em bits

§ 1 registrador = 6 transistores

§ 1 transistor mínimo = 25 λ2

§ 1 rbe = 2700 λ2

Norian Marranghello – 2006 – Arquiteturas de Computadores

Considerações sobre custo

§ 1 rbe = um bit de registrador

§ 1 célula SRAM = 0,6 rbe

§ 1 célula DRAM = 0,1 rbe

§ 1 célula CAM = 2 rbe

Norian Marranghello – 2006 – Arquiteturas de Computadores

10

Considerações sobre custo

§ Planta baixa (floor plan)

§

§

§

§

§

Planejamento da área ocupada

Cálculo das funcionalidades do sistema

Estimativa da complexidade da lógica

Previsão do sistema de comunicação

Inclusão do overhead de projeto (≈20%)

Norian Marranghello – 2006 – Arquiteturas de Computadores

Considerações sobre custo

37,8 mm2

Processador Registradores

inteiro

e Barramentos

16,1mm2

27 mm2

10,3 mm2

Processador de

ponto flutuante

Lógica adicional

§ Planta baixa

Memória Cache

92,8 mm2

Norian Marranghello – 2006 – Arquiteturas de Computadores

Fim!

n

Grato pela presença e

até a semana que vem.

Norian Marranghello – 2006 – Arquiteturas de Computadores

11