1.

2. Versão

Publicação n9

3. Data

INPE 3049 NI1/202

-

—

tá Interna O Externa

Programa

4. Origem

O Restrita

AUTOM/ETSS

DIL/DRC

6. Palavras chaves

-

selecionadas pelo(s) autor(es)

MEMÓRIA

R.A.M.

B.P.C.D.

EXPANSÃO DE MEWRIA

7. C.D.U.:

5. Distribuição

Abril, 1.984

681.3.067

' 8. Titulo

INPE 3049 NI1/202

-

—

MANUAL DA PLACA DE EXPANSÃO DE MEMOS1A EXPM3

10. Pãginas: 27

11. Oltima pãgina:

12. Revisad

9. Autoria

Mauricio Macedo de Faria

Luiz Antanio dos Reis Bueno

José Teixeira da Matta Bacellar

A.8

por

Satoshi Koshima

13. Autorizada por

\

‘

Assinatura responsãvel

4,- 'á

Á

tia7Y<T4110.--„,

a,t-ta-d-Q-n

Nelson ae Jesus Parada

Diretor Geral

,

14. Resumo/Notas

Este manual descreve a placa de expansão de memdriaEXPM3 com

4k bytes de RAM, desenvolvida para o Barramento Padrão para Circuitos Digi

tais (BPCD) da Divisão de Rastreamento e Comando de Veiculos Espaciais (DRC)

do INPE.

•

15. Observações

ABSTRACT

This manual describes the memory expansion board EXPM3

with 4 kbytes of RAM, deve loped for the Digital Circuits Standard Bus

(BPCD) of the Divisão de Rastreamento e Comando de Veículos Espaciais

(DRC) of INPE.

SUMARIO

Pãg.

LISTA DE FIGURAS

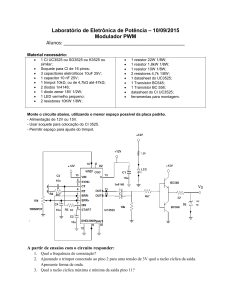

1. INTRODUÇÃO

1

2. DESCRIÇÃO GERAL

1

3. ESPECIFICAÇÕES TÉCNICAS

6

4. OPERAÇÃO E FUNCIONAMENTO

6

4.1 4.2 4.2.1

4.2.2

4.3 -

6

6

6

7

7

Introdução

Funcionamento

- Leitura

- Escrita

Programação

5. CONCLUSÃO

9

BIBLIOGRAFIA

11

APÊNDICE A - FIGURAS E TABELAS

—

—

LISTA DE FIGURAS

Pãg.

1 - Diagrama de blocos da EXPM3

2

2 - Painel frontal

4

3 - Possíveis localizações da EXPM3 na memOria

8

- v -

1. INTRODUCÃO

A placa de expansão de memória EXPM3 tem por finalidade

permitir a um microcomputador, que utilize o barramento BPCD, aumentar

a sua capacidade de mem6ria em incrementos de 4 kbytes.

A EXPM3 é projetada em torno dos circuitos integrados IN

TEL 2114 ou 2148. A placa possui 8 circuitos integrados de um desses ti

pos, perfazendo um total de 4 kbytes.

A RAM INTEL 2148 apresenta duas vantagens sobre a 2114:

menor tempo de acesso e consumo reduzido. Ambos os tipos são compati

veis pino a pino.

O tempo de acesso tipico para o uso da EXPM3 é de 295 ns

quando a placa utilizar a RAM tipo 2114AL-4.

2. DESCRIÇÃO GERAL

A EXPM3 é uma placa de expansão de memória RAM com capa

cidade de 4 kbytes, baseada nos circuitos integrados INTEL 2114 ou IN

TEL 2148. Estes são memórias RAM, organizadas em 1024 palavras de 4 bits,

compativeis pino a pino. A diferença bãsica entre estes dois circui

tos reside no menor tempo de acesso e consumo reduzido do INTEL 2148.

A Figura 1 apresenta o diagrama em blocos da EXPM3. Esta

consiste em um "buffer" de endereço, um "buffer" de dados (bidirecio

nal), um circuito de seleção de placa, um decodificador de endereço e

a memória propriamente dita.

O bloco de memória é composto por 8 circuitos integrados

do tipo 2114 ou 2148, perfazendo um total de 4096 palavras de 8 bits

(4 kbytes).

Os sinais de CHIP SELECT (CS/) para as memórias são gera

dos pelo decodificador de endereço. Este, por sua vez, é acionado pe

lo circuito de seleção de placa.

O circuito de seleção de placa é um circuito 16gico que

habilita o decodificador de endereço e o "buffer" de dados se em suas

quatro entradas estiver presente o endereço que foi programado nos

"jumpers".

O "buffer" de dados é um circuito integrado

bidirecio

nal, que isola do BPCD o barramento de dados interno da EXPM3 para evi

tar conflitos.

A EXPM3 foi montada em uma Placa para Desenvolvimento de

Circuitos Digitais (PDCD) utilizando a técnica de "wire-wrapping".

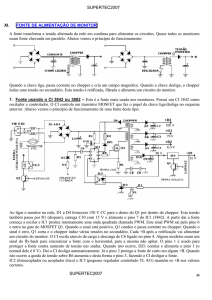

No painel frontal da EXPM3 (Figura 2), têm-se um LED in

dicador de alimentação por bateria, um outro LED que indica a presen

ça da alimentação de +5 V (VCC) do BPCD, uma chave LEIT/LEIT-ESCR que

impede ou não a escrita de dados nas memórias, além de dois bornes pa

ra a ligação da placa da bateria e do circuito de alarme, SBMV,a qual

permite que a alimentação do barramento seja desligada, sem que isso

acarrete a perda dos dados da memória.

A operação da EXPM3 com bateria, quando aquela utiliza os

circuitos integrados 2148, não é confiãvel devido ao fato de a tensão

fornecida pela SBMV não ser elevada o suficiente para aquele tipo de

memória.

A chave LEIT/LEIT-ESCR é uma facilidade destinada a evi

tar "acidentes" do tipo alteração dos dados da RAM, provocados pela

execução de um programa incorreto. Este tipo de acidente é bastante co

mum na fase de desenvolvimento de programas longos. Antes de executar

o programa, deve-se passar a chave para a posição LEIT. Assim garante

-se que aquela placa de mem6ria não poderá ser escrita, mas apenas li

da, salvaguardando o programa.

- 4 -

EXPM 3/1

BATERIA

o

RAM

LEIT.

r

il

LEIT./ESCR.

O

BATERIA

O

VCC

o

Fig. 2 - Painel frontal.

A Tabela 1 apresenta as linhas do BPCD utilizadas

EXPM3.

pela

-5-

TABELA 1

LINHAS DO BPCD USADAS PELA EMPM3

COMPONENTES

PINO N9

+5V

GND

DB4

DB5

DB6

DB7

MEMW

AB4

AB5

AB6

AB7

AB12

AB13

AB14

AB15

GND

GND

+5V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

SOLDA

+5V

GND

DBO

DB1

DB2

DB3

MEMR

ABO

AB1

AB2

AB3

AB8

AB9

AB10

AB11

GND

GND

+5V

-6-

3. ESPECIFICAÇÕES TÉCNICAS

Esta seção apresenta as especificações técnicas da placa

de expansão de mem6ria EXPM3.

Consumo (nominal)

+5V @. 750 mA.

Capacidade

4096 x 8 bits (4 kbytes).

Tempo de acesso (máximo)

95 ns + tempo de acesso da RAM.

Painel

LED BATERIA

LED VCC

Entrada BATERIA

Chave LEIT/ LEIT-ESCR

Endereçamento

Programável através de "jumpers".

4. OPERAÇÃO E FUNCIONAMENTO

4.1 - INTRODUÇÃO

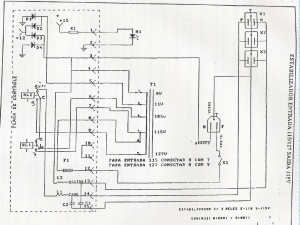

Nesta seção apresenta-se uma descrição sucinta do princi

pio de funcionamento da EXPM3. Sua leitura deverá ser acompanhada no

diagrama esquemático.

4.2 -

FUNCIONAMENTO

4.2.1 - LEITURA

Inicialmente a CPU envia, através do BPCD, o endereço do

dado a ser lido. Este endereço atravessa o "buffer" de endereço, CIO1

e CIO2, e atinge as entradas de endereço de todas as mem6rias, onde

aguarda que os integrados desejados sejam selecionados.

Se as linhas Al2 a A15 da barra de endereços

apresenta

rem o endereço programado nos "jumpers" JO a J3, então o decodificador

de endereço, CI04, será habilitado e decodificará as linhas A10 e A11.

-7-

A decodificação do endereço faz com que uma das quatro linhas de sai

da 00 a 03 do decodificador vã para o nivel baixo, selecionando assim

o par de memórias desejado.

O mesmo sinal que habilita o decodificador, CI04, habili

ta também o "buffer" de dados, CI14, desde o instante em que uma das

linhas MEMR/ ou MEMW/ estiver ativa.

4.2.2 - ESCRITA

A escrita é semelhante "a leitura. O endereço atinge

as

memórias através do "buffer" de endereço e aguarda a seleção do par de

RAMs desejado. Se o endereço presente nas linhas Al2 a A15 for igual

ao programado nos "jumpers" JO a J3, o decodificador de endereço serã

habilitado. Desta forma, uma das suas linhas de saida 00 a 03 ira pa

ra o nivel baixo, selecionando o par de RAMs conectado a ela.

A partir do momento em que a linha MEMW/ fica ativa (ni

vel lógico baixo), o "buffer" de dados, CI14, é habilitado. Uma vez

que a operação é de escrita, a linha MEMR/ permanece em nível alto,

garantindo que a passagem de dados se dê no sentido de A para B (do

BPCD para o barramento interno).

A EXPM3 agora esta preparada para receber da CPU o dado

a ser gravado.

4.3 - PROGRAMAÇÃO

A área de memória onde a EXPM3 será instalada é programa

vel por "hardware". O barramento de endereços do BPCD possui dezesseis

linhas (AO a A15). Isto quer dizer que cada posição de memória pode

ser representada por um endereço hexadecimal de quatro digitos.

Os "jumpers" JO a J3 permitem programar o digito mais

significativo dos endereços da área. Este é o digito que seleciona a

placa.

- 8 -

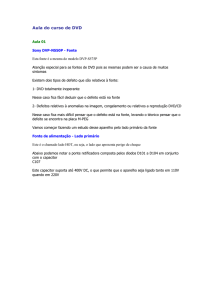

A Figura 3 apresenta as ãreas da mem6ria onde se pode lo

calizar a EXPM3.

E importante lembrar que cada ãrea deve possuir ape

nas uma EXPM3 e que em alguma região da mem6ria estar ã o sistema moni

tor, geralmente em ROM. Nesta região não dever ã ser instalada nenhuma

outra placa.

FFFF

ÁREAF

--

—

F000

E FFF

ÁREA E

.--- -- -- -- — — -- E 000

DFFF

ÁREAD

DOMA

— — — — — —

ÁREAC

CFFF

c000

"

. FF

ÁREA 2

2000

-- 1FFF

-ÁREA 1

1000

-- OFFF

ÁREA 0

0000

Fig. 3 - Possíveis localizações da EXPM3 na mem6ria.

Pode-se ver que cada ãrea de memaria abrange uma faixa de

endereços em que o digito mais significativo é o mesmo para toda a

área. Este digito pode ser escolhido e programado para cada placa que

se queira instalar, lembrando sempre que não é permitido ter mais uma

placa programada para o mesmo digito.

A programação deste digito é efetuada da seguinte forma:

1) Escolhe-se a ãrea de mem6ria onde instalar a EXPM3.

-9-

2) Toma-se o digito mais significativo dos endereços daquela área

de mem6ria e transforma-se este para o sistema binário.

3) Iguala-se o estado lógico das linhas A15 a Al2 com o número bi

nãrio obtido no passo 2, sendo A15 o bit mais significativo e

Al2 o menos significativo.

4) Para cada uma das linhas Al2 a A15: Faz-se o seguinte: se

o

valor desta linha no passo 3 for o binário "1", então instala

-se o "jumper" na outra entrada da mesma porta ou-exclusivo,

do contrário, isto é, se o valor do bit for "0"o "jumper" não

deve ser instalado.

Como exemplo supor-se-á ser necessário instalar uma EXPM3

na área 5 da mem6ria (5000-5FFF). O passo 1 já foi portanto executado.

Transforma-se o hexadecimal 5 em binário obtendo 0101 (passo 2). Igua

la-se (A15 A14 A13 Al2) = (0101) obtendo-se:

A15 = O

A14 = 1

A13 = O

Al2 = 1

e está completado o passo 3. A programação propriamente dita consiste

em instalar ou não os "jumpers" JO a J3, conforme é explicado no pas

so 4.

5. CONCLUSÃO

A EXPM3 já foi montada e testada, estando atualmente em

operação normal no laboratório do grupo AUTOM-DRC.

A capacidade da EXPM3 pode ser facilmente aumentada em in

crementos de 1 kbytes. O decodificador C104 permite selecionar até 8

kbytes de mem6ria tipo 2114 ou 2148. Para tal será necessário utili

BIBLIOGRAFIA

INTEL. MCS 80/85 Family User's Manual.

1979.

A2 desse mesmo integrado, ligando a ela a linha de endereço Al2.

A

porta "a" do C103 deverá- ser desconectada do "wired-and", e, finalmen

te, os outros circuitos integrados de memória deverão ser instalados.

Suas ligações serão em tudo semelhantes ãs dos integrados de memória

jã instalados.

Uma placa de expansão com 8 kbytes, EXPM4, jã foi monta

da e testada e encontra-se funcionando normalmente no laboratõrio do

grupo AUTOM.

Uma modificação que visa diminuir o custo da placa consis

te em substituir os integrados CIO1 e C102 por "buffers" do tipo 74241

que são mais simples e baratos.

APrNIWF A

FIGURAS E TABELAS

Neste apêndice encontram-se algumas figuras e tabelas im

portantes para a correta definição da Placa de Expansão de Memória

EXPM3, tais como: o esquema do circuito, o diagrama para a localização

dos componentes, bem como a relação dos componentes.

-A.1 -

A seguir Figura A.1

-A.5-

TABELA A.1

TABELA DE LIGAÇÕES DA EXPM3

SINAIS

NOME

CONEXÕES

CL PINO

C7-4 1

E4-5 1

02

ABI

C7-6 1

E4-6 1

AB'2

C7-8 1

._ E4-7 1

04

AB'3

C7-10 1

E4-4 1

AB'4

C7-15 1

E4-3 1

C7-17 1

AB'5

06

E4-2 1

07

AB'6

C7-19 1

E4-1 1

AB'7

08

C7-21 1

E4-17 1

09

AB'8

A7-4 1

E4-16 1

Ab'9

10

A7-6 1

F4-15 1

F7-11 1

11_

DI3 1 0

12

F7-12 1

DBI

DB'2

Ti

F7-13 1

14

DB'3

F7-14 1

15

DB'4

F7-15 1

DB'5

16

F7-16 1

DB'6

17

F7-17 1

18

DB 1 7

F7-18_11

19

CS 0

A6-15 1

20

CS 1

A6-14 1

21

CS 2

A6-13 1

22

CS 3 _ A6-12 1]

23

WE

B5-10 1

D4-10 1

24 MD.STB-DS2

1

CLR

C7-14

25 iMD.STB-DS2

CLR

A7-14

26

J1

D7-9 1

27

J2

D7-12 1

28

J3

D7-2 1

29

J4

D7-5 1

30 SFIFCT

A6-6 1

E7-5

31 CHIPSEL 0

A7-8

32 CHIPSEL 1

A7-10 1

33 CI5a-sai4 E7-3 T

01

A13 1 0

CI. PINO

CI. PINO

CI. PINO

CL PINO

C5-5

D4-5

C5-6

D4-6

C5-7

04-7

C5-4

D4-4

C5-3

D4-3

C5-2

D4-2

C5-1

D4-1

C5-17

D4-17

C5-16

D4-16

C5-15

04-15

E5-14

E5-13

E5-12

E5-11

F4-14

F4-13

F4-12

EI-11

B5-8

C5-8

D5-8

E5-8

C5-10

C4-10

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

B5-5 1

C4-5

B5-6 1

C4-6

B5-7 1

C4-7

B5-4 1

C4-4

B5-3 1

C4-3

B5-2 1

C4-2

B5-1 1

C4-1

B5-17 1

C4-17

B5-16 1

C4-16

B5-15 1

C4-15

D5-14 1

D5-13 1

D5-12 1D5-11 1

E4-14 1

E4-13 1

E4-12 1

B5-14 T

B5-13T

B5-12 , T

B5-11 ri

D4-14 ,1

1

D4-I3 'T

D4-I2 1

1

T

T

T

T

T

C4-8 1

D4-8 1

E4-8 1

F4-81

D5-10_1

D6_13 ,I

D6-9

D6-10 .

D6-11 i

D6-12 J

E5-1# T

X1

C7-13

T

C7-11 1

C7-2 T

D6-8

A7-13

D6-6

D6-5

D6-4

D6-3

T A7-11 1

T E6-8(a1'

T E6-9(a2;

TE6-10(a3,

E6-11(a4

A7-2

D6-7

n7 - 1 1

D7-11

n7 - 6

E5-5

1

F4-5

D5-6 T

E5-6

1

F4-6

D5-7 T

E5-7

1

F4-7

D5-4 T

E5-4

1

F5-4

T

D5-3 1

E5-3

1

F5-3

T

D5-2 ,T

E5-2

1

F5-2 T

D5-1 T

E5-1

1

F5-1

T

D5-17 - 1

E5-17

1

F5-17

T

D5-16 : i

E5-16

1

F5-16

D5-15 - T

E5-15

1

F5-15

T-

E4-10

T

.

•

1

CI. PINO

D5-5 T _

:

;

C5-14

C5-13 ___J

C5-12

C5-11

C4-14

C4-13

C4-12

. C4-11

F4-10 1

n7 - s kl

-

D6-2

A6-1

A6-2

E7-4

(continua)

-A.6-

Tabela A.1 - Continuação

N2

NOME

+5V (solda

,no filete A)

35 +5V (solda

no filete C)

36 +5V (solda

no filete E)

_

CI. PINO

CI. PINO

CI. PINO

CI. PINO

CL PINO

CI. PINO

34

37

IGND (solda

,no filete B)

38 ,GND (solda

no filete D)

39

A7-24

A6-16

C7-24

07-14

E6-2

E7-14

E6-4_.

F7-20

06-1

X8

X7

A7-12

B5-9

A7-1

A6-3

A6-4

A6-5

A6-8

C4-9

C7-1

04-9

D7-7

C5-9

05-9

C7-12

E5-9

X5

E6-5(64

F7-10

E6-6033:

E7-7

GND (snlda

no filete F)

BUS +5V

(pino 1)

41 BUS GMD

•

, ( p i -TO-2)

r

- 42 BUS DB4

(pino 5)

43 BUS DB5

(pino 6)

44 BUS DB6

(pino 7)

45 BUS DB7

(pino 8)

46 BUS

(pino 15)

47 BUS AB4

(pino 17)

48 BUS AB5

(pino 18)

49 BUS AB6

(pino 19)

50 BUS AB7

(pino 20)

51 BUS AB12

(pino 23)

52 BUS AB13

E4-9

E6-8(01)

F4-9

E6-7(02)

40

mrmw

(pino

24)

F7-5

F7-4

____

.

F7-3

F7-2

X2

T

E7-1

C7-16

.

C7-18

C7-20 _

C7-22

07-10

_

07-13

53

BUS AB14

(pino 25)

54 BUS AB15

(pino 26)

55 - BUS GND

(pino 32)

D7-1

1

117-4

_

(continua)

- A.7 -

N2

NOME

56

BUS GND

(pino 34)

BUS +5V

57

(pino

58

CI. PINO

CI. PINO

CI. PINO

35)

BUS +5V

((Tino 36)

55 DO 00

,

(pino 37)

60

61

62

63

64

BUS DBO

(pino 40)

BUS DB1

(Pino 41)

BUS DB2

(pino 42)

BUS DB3

(pino 43)

BUS MEMR

(pino SØ)

65

66

67

68

69

70

71

BUS ABO

(pino 52)

BUS AB1

(pino 53)

BUS AB2

(pino 54)

BUS AB3

(pino 55)

BUS AB8

(pinn SR)

BUS AB9

(pino 59)

BUS AB10

(pino 60)

BUS AB11

(pino 61)

BUS GND

(pino 67)

BUS GND

(pino 69)

BUS +5V

(pino 70)

-------

72

73

74

75

_

F7-9

F7-8

F7-7

F7-6

F7-1

T

E7-2

C7-3

C7-5

C7-7

C7-9

A7-3

A7-5

A7-7

A7-9

.

CI. PINO

CL . PINO

CI. PINO

-A.8-

TABELA A.2

RELAÇÃO DE COMPONENTES DA PLACA (PE) EXPANSÃO DE MEMÓRIA EXPM3

N9 CIRCUITO

Cl a C12

C13

CI1 e Cl2

CI3

CI4

CI5

CI6 a CI13

CI14

D1

D2

D3

R1 a R8

R9

R10 e R11

R12 a R15

DESCRIÇÃO

Capacitor Cerâmico de Disco, 100 KpF.

Capacitor de Tântalo, 100 pF, 20 V.

Port de I/O 8 bits, INTEL 8212.

Ou-exclusivo (coletor aberto), 5N74L5136.

Decodificador 8 para 1, INTEL 8205.

Nand 2 entradas, 74L500.

RAM 1024 x 4 bits, INTEL 2114 ou 2148.

"Buffer" 8 bits bidirecional, 5N74L5245.

Diodo de silicio, 1N4004.

Diodo LED verde.

Diodo LED vermelho.

Resistor

Resistor

Resistor

Resistor

de carbono, 1 kohm, 1/4 W, 5%.

de carbono, 1,5 kohm, 1/4 W, 5%.

de carbono, 220 ohm, 1/8 W, 5%.

integrado, 1 kohm.