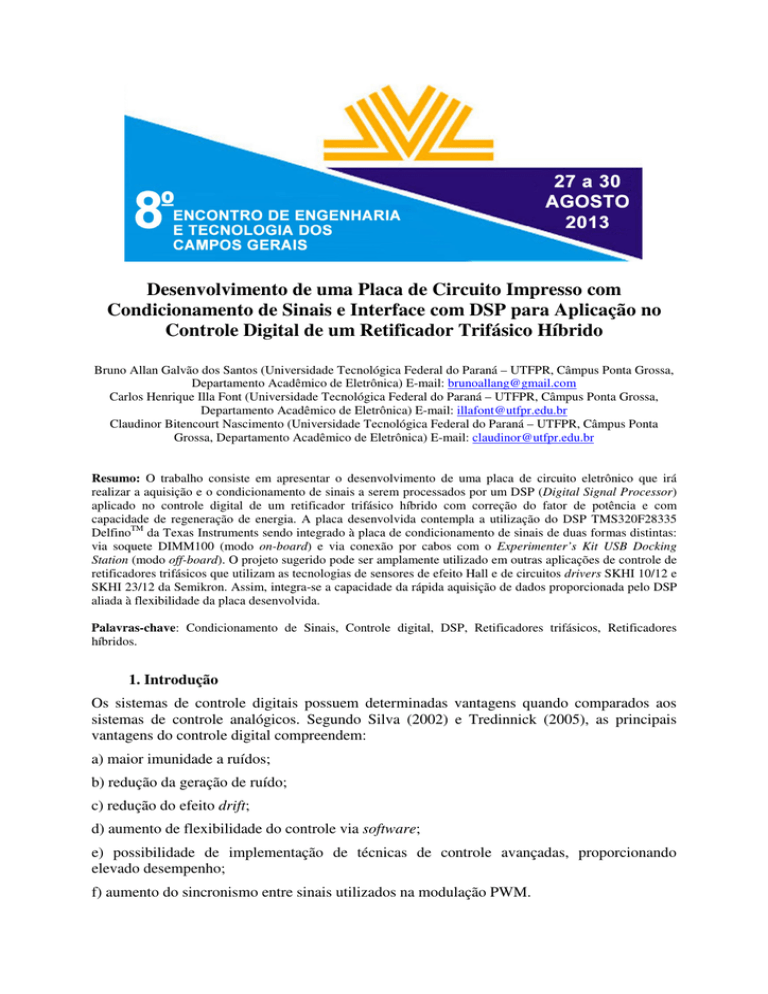

Desenvolvimento de uma Placa de Circuito Impresso com

Condicionamento de Sinais e Interface com DSP para Aplicação no

Controle Digital de um Retificador Trifásico Híbrido

Bruno Allan Galvão dos Santos (Universidade Tecnológica Federal do Paraná – UTFPR, Câmpus Ponta Grossa,

Departamento Acadêmico de Eletrônica) E-mail: [email protected]

Carlos Henrique Illa Font (Universidade Tecnológica Federal do Paraná – UTFPR, Câmpus Ponta Grossa,

Departamento Acadêmico de Eletrônica) E-mail: [email protected]

Claudinor Bitencourt Nascimento (Universidade Tecnológica Federal do Paraná – UTFPR, Câmpus Ponta

Grossa, Departamento Acadêmico de Eletrônica) E-mail: [email protected]

Resumo: O trabalho consiste em apresentar o desenvolvimento de uma placa de circuito eletrônico que irá

realizar a aquisição e o condicionamento de sinais a serem processados por um DSP (Digital Signal Processor)

aplicado no controle digital de um retificador trifásico híbrido com correção do fator de potência e com

capacidade de regeneração de energia. A placa desenvolvida contempla a utilização do DSP TMS320F28335

DelfinoTM da Texas Instruments sendo integrado à placa de condicionamento de sinais de duas formas distintas:

via soquete DIMM100 (modo on-board) e via conexão por cabos com o Experimenter’s Kit USB Docking

Station (modo off-board). O projeto sugerido pode ser amplamente utilizado em outras aplicações de controle de

retificadores trifásicos que utilizam as tecnologias de sensores de efeito Hall e de circuitos drivers SKHI 10/12 e

SKHI 23/12 da Semikron. Assim, integra-se a capacidade da rápida aquisição de dados proporcionada pelo DSP

aliada à flexibilidade da placa desenvolvida.

Palavras-chave: Condicionamento de Sinais, Controle digital, DSP, Retificadores trifásicos, Retificadores

híbridos.

1. Introdução

Os sistemas de controle digitais possuem determinadas vantagens quando comparados aos

sistemas de controle analógicos. Segundo Silva (2002) e Tredinnick (2005), as principais

vantagens do controle digital compreendem:

a) maior imunidade a ruídos;

b) redução da geração de ruído;

c) redução do efeito drift;

d) aumento de flexibilidade do controle via software;

e) possibilidade de implementação de técnicas de controle avançadas, proporcionando

elevado desempenho;

f) aumento do sincronismo entre sinais utilizados na modulação PWM.

Além das vantagens citadas, a utilização de processador digital de sinais (Digital Signal

Processor - DSP) tem se tornado atraente para aplicações que envolvam Eletrônica de

Potência pois as estruturas de controle digital apresentam baixo custo e alto desempenho

(MUSSA, 2003). Faz-se também necessário ressaltar que, para aplicações de elevada

potência, o custo da estrutura de controle é pequeno quando comparado ao custo do estágio de

potência (BATISTA, 2006).

O objetivo deste trabalho consiste no desenvolvimento de uma placa de circuito eletrônico

para condicionamento de sinais e interface com DSP, para utilização em controle digital.

Assim, pretende-se utilizar a placa desenvolvida conectada ao estágio de potência a fim de

lograr dos benefícios que a tecnologia digital pode oferecer.

O foco do trabalho está na substituição de uma estrutura de controle analógico por uma

estrutura de controle digital em um retificador trifásico híbrido proposto em Illa Font (2009).

Trata-se de um retificador que utiliza a estratégia de Controle por Valores Médios

empregando circuitos analógicos. O retificador proposto conta com reduzido número de

interruptores controlados e com as características de elevado fator de potência, controle da

tensão de saída e capacidade de regeneração de energia para a rede de alimentação. O

funcionamento deste retificador foi comprovado através de curvas experimentais que mostram

a correção do fator de potência e o controle da tensão de saída em um protótipo com potência

de saída de 20 kW (ILLA FONT, 2009).

A Figura 1 apresenta o circuito elétrico do retificador proposto por Illa Font (2009) em que

será aplicada a estrutura do controle digital, a Figura 2 apresenta uma foto do protótipo

implementado e a Tabela 1 apresenta as especificações de projeto do retificador.

A placa desenvolvida neste trabalho poderá ser utilizada em outras aplicações em Controle

Digital e Eletrônica de Potência que envolvam a utilização de sensores de efeito Hall e de

circuitos drivers da Semikron (modelos SKHI 10/12 e SKHI 23/12) devido à flexibilidade

fornecida tanto pelo microcontrolador utilizado quanto pela placa de condicionamento de

sinais projetada.

O DSP utilizado foi o TMS320F28335 DelfinoTM com o kit de desenvolvimento

Experimenter’s Kit USB Docking Station, ambos fabricados pela Texas Instruments.

Figura 1 – Retificador trifásico híbrido. Fonte: Illa Font (2009).

Figura 2 – Fotografia do protótipo. Fonte: Illa Font (2009).

Tabela 1 – Especificações de projeto do retificador trifásico híbrido.

Parâmetro

Tensão de Entrada [V]

Tensão de Saída [V]

Potência de Saída [kW]

Frequência da Rede [Hz]

Frequência de Comutação [kHz]

Fonte: Illa Font (2009)

Valor

380

700

20

60

10

A Tabela 2 apresenta as principais características do DSP utilizado. Outras características

deste controlador podem ser encontradas nos manuais Texas Instruments (2011) e Texas

Instruments (2012) disponibilizados pelo fabricante.

Tabela 2 – Principais características do DSP TMS320F28335 DelfinoTM.

Parâmetro

Frequência

Ciclo de instrução

Memória RAM

Memória Flash

EPWM (Enhanced Pulse Width Modulator)

HRPWM (High Resolution Pulse Width Modulator)

ECAP (Enhanced Capture Module and Registers)

ADC (Analog to digital converter)

ADC - Tempo de conversão

Timers de propósito geral

Watchdog Timer

Interrupções externas

GPIO (General Purpose Input/Output)

Fonte: Adaptado de Texas Instruments (2012)

Valor

150 MHz

6,67 ns

68 kB

512 kB

6 canais (16-Bit)

6 canais (24-Bit)

6 canais (32-Bit)

16 canais (12-Bit)

80 ns

3 timers (32-Bit)

1 timer

8

88

Desta forma, justifica-se a implementação das estruturas de controle e de modulação através

da utilização de um processador digital de sinais (Digital Signal Processor - DSP) a fim de

alcançar os objetivos deste trabalho

2. Desenvolvimento

2.1 Requisitos da Placa

Em Santos (2012), foi realizada a etapa inicial do projeto do controle digital do Retificador

Trifásico Híbrido: uma análise comparativa de três técnicas de controle de corrente. São elas:

a) Controle por Valores Médios;

b) Controle Indireto (Autocontrole);

c) Controle por Erro Complementar (Modo Complementar).

De acordo com o estudo desenvolvido, o melhor desempenho nas simulações numéricas se

deu com a utilização do Controle Indireto (Autocontrole) (SANTOS, 2012).

k m2

k m2

k m2

k m1

A Figura 3 apresenta o diagrama de blocos da estratégia de Controle Indireto adaptada ao

circuito objeto de estudo. Na Figura 3, a parte do circuito expressa por linhas mais claras

representa o estágio de potência do retificador, as linhas mais escuras representam o sistema

de controle e a linha tracejada representa a sincronização de frequência entre as ondas

triangular e dente-de-serra, utilizadas na modulação PWM.

Figura 3 – Controle indireto (autocontrole).

Através da Figura 3 pode ser verificado que dentre os principais requisitos para

implementação do controle com melhor desempenho nas simulações numéricas estão:

a) a medição de corrente da entrada das três fases (IsensA, IsensB, IsensC);

b) a medição de corrente no indutor Lb2 (Ilb);

c) a medição da tensão de saída (Vo);

d) a geração de onda triangular e dente-de-serra utilizadas na modulação PWM;

e) a geração de sete pulsos de comando para acionamento dos transistores de potência (S1 à

S6, e Sb).

Como se pretende aplicar e testar não somente o Controle Indireto, mas sim também outros

tipos de controle, torna-se necessário incluir outros requisitos a placa. Técnicas de controle,

tais como o Controle por Valores Médios, exigem a medição das tensões de fase de entrada.

Logo, se torna interessante acrescentar medições de tensão na entrada do retificador.

Torna-se também interessante incluir PLLs (Phase Locked Loop) na placa de

condicionamento de sinais, pois estes possuem grande aplicação na área de controle. PLLs

têm sido vastamente utilizados para aplicações em que se deseja extrair com precisão

informações da tensão fornecida pela rede de energia elétrica, tais como frequência e fase. Tal

característica se torna altamente atrativa para solucionar a questão do sinal de referência

presente no condicionador de tensão em equipamentos que necessitam de circuitos de

sincronismo (GOMES, 2007).

A geração das ondas utilizadas na modulação PWM e na geração dos pulsos de comando foi

realizada por componentes analógicos em Illa Font (2009). Neste trabalho, estes sinais serão

gerados pelo DSP a fim de alcançar maior imunidade a ruídos e aumento do sincronismo

entre os sinais utilizados na modulação PWM.

No quesito proteção, torna-se também interessante adicionar medições para detectar

sobretensão e sobrecorrente.

É interessante também acrescentar conectores na placa de condicionamento para alimentação

de futuros sensores de efeito Hall. Estas fontes extras utilizam a Fonte Auxiliar Linear

desenvolvida em Illa Font (2009). Estes conectores com três terminais deverão fornecer

alimentação tipicamente utilizada por sensores de efeito Hall: 15 V, GND e -15 V.

2.2 Especificações da Placa

Após serem discutidos alguns requisitos no tópico anterior, a Tabela 3 apresenta as

especificações para confecção da placa.

Tabela 3 – Especificações de projeto da placa de condicionamento de sinais

Parâmetro

Amostradores de corrente de entrada (IsensA, IsensB, IsensC)

Amostradores de tensão de entrada para sincronismo (VsincA, VsincB, VsincC)

PLLs (Phase Locked Loop) para tensão de entrada (Vab-PLL, Vbc-PLL, Vca-PLL)

Amostrador de tensão de saída (Voa)

Amostrador de corrente no indutor (Ilb)

Saídas para comando dos transistores (Vg4,Vg1) (Vg5,Vg2) (Vg6,Vg3) (Vgb)

LEDs para indicação de sobretensão

LEDs para indicação de sobrecorrente

LEDs para indicação da atuação de proteção dos circuitos drivers

Quantidade

3

3

3

1

1

7

1

4

4

2.3 Interface entre a Placa de Condicionamento de Sinais e o DSP

A estrutura para condicionamento de sinais e interface com o DSP TMS320F28335 é

apresentada pelo diagrama de conexões da Figura 4. Este diagrama mostra as conexões entre

as partes do sistema e as variáveis de conexão entre as placas do protótipo.

Figura 4 – Diagrama de Conexões.

Pode-se observar na Figura 4 que a placa desenvolvida contempla a utilização do DSP Texas

TMS320F28335 DelfinoTM sendo integrado à placa de condicionamento de sinais de duas

formas distintas: via soquete DIMM100 (modo on-board) e via conexão por cabos com o

Experimenter’s Kit USB Docking Station (modo off-board). O modo off-board servirá para os

primeiros testes com o circuito desenvolvido. No decorrer do desenvolvimento do trabalho,

planeja-se realizar a programação do DSP F28335 controlCARD™ junto ao Experimenter Kit

e depois conectá-lo diretamente na placa desenvolvida para que o sistema funcione de forma

independente (modo on-board).

2.4 Filtros Anti-aliasing

Para evitar o efeito de aliasing na amostragem de correntes, efeito este descrito em Tomaseli

(2001) e Mussa (2003), foram utilizados filtros analógicos anti-aliasing baseados em Batista

(2006). A Figura 5 apresenta a implementação deste filtro com amplificador operacional.

Figura 5 – Filtro anti-aliasing.

2.5 Amostragem das Correntes de Entrada

Os sensores de corrente utilizados em Illa Font (2009) são sensores de efeito Hall LA 55-P,

fabricados pela LEM. O sinal amostrado foi grampeado em um nível da metade de 3,0 V para

que a excursão da amostra de corrente não possua valores negativos e venha a danificar o

DSP. Este sinal atenuado com ganho do amplificador operacional é finalmente limitado pelo

Circuito Integrado (CI) limitador modelo TL7726 da Texas Instruments. Este CI irá limitar a

faixa de variação de tensão do sinal entre 0 a 3,0 V para proteção das entradas do conversor

analógico digital (A/D) do DSP utilizado.

A Figura 6 apresenta a implementação do amostrador das correntes de entrada da fase A. O

mesmo circuito é aplicado para as fases B e C.

Figura 6 – Amostragem das correntes de entrada.

2.6 Amostragem da Tensão de Saída

O sensor de tensão utilizado em Illa Font (2009) é um sensor de efeito Hall LV 25-P SP8,

fabricado pela LEM. A amostragem da tensão de saída utiliza um filtro anti-aliasing seguido

também do CI limitador TL7726. A Figura 7 apresenta a implementação do amostrador da

tensão de saída do retificador.

Figura 7 – Amostragem da tensão de saída.

2.7 Amostragem da Corrente do Indutor

Para esta amostragem é utilizada a mesma configuração do filtro anti-aliasing sugerido na

Figura 7.

2.8 Sincronismo

Para a amostragem dos sinais de sincronismo das três fases, em Illa Font (2009) foram

utilizados três transformadores monofásicos conectados em ∆-∆, e com relação de

transformação igual a 0,019. A Figura 8 demonstra os transformadores de sincronismo

implementados em Illa Font (2009).

Figura 8 – Transformadores de sincronismo. Fonte: Illa Font (2009).

O sinal amostrado é obtido através de filtros passivos sugeridos em Batista (2006). Desta

forma, obtêm-se três sinais senoidais em fase com as tensões da rede. Os pulsos de

sincronismo são gerados a partir da comparação deste sinal com zero, utilizando um

comparador com histerese. A Figura 9 apresenta a geração do pulso de sincronismo para a

fase A. O mesmo circuito é aplicado para as fases B e C.

Figura 9 – Geração do pulso de sincronismo para fase A.

2.9 PLLs (Phase Locked Loop) para Tensão de Entrada

Para esta amostragem é utilizada a mesma configuração do filtro anti-aliasing sugerido na

Figura 6, com a diferença de que os sinais de entrada passam a ser a combinação duas a duas

das tensões trifásicas provenientes dos transformadores de sincronismo (Figura 8).

2.10 Interface com Drivers para Comando dos Transistores

Para o comando dos transistores IGBTs foram utilizados os circuitos de comando (drivers)

SKHI10/12 e SKHI23/12, fabricados pela Semikron.

O driver SKHI10/12 é projetado para acionamento de um interruptor e será utilizado para o

acionamento do interruptor Sb.

Os drivers SKHI23/12 são projetados para o acionamento de dois IGBTs, conectados na

configuração de braço ou independentes. Desta forma, utilizam-se três dispositivos

SKHI23/12 para acionamento de seis interruptores IGBTs (S1 à S6).

Entre as principais características dos drivers estão: comando de IGBTs com VCE de até

1200 V; isolação por foto-acoplador; saída do sinal de erro com lógica em nível alto ou baixo;

proteção contra curto-circuito através do monitoramento da tensão VCE do IGBT;

desligamento suave na condição de curto-circuito.

Como o nível dos sinais de saída dos moduladores PWM do DSP é 0,0 V ou 3,0 V, faz-se

necessário adaptar estes sinais ao nível de tensão dos circuitos lógicos e a entrada dos

circuitos de comando. Para isto, são utilizados buffers e inverting buffers com a saída em

coletor aberto conectada a 15 V. A utilização dos CIs do tipo inverting buffers se faz

necessário para gerar o sinal complementar do PWM de um mesmo braço do retificador

trifásico. A Figura 10 apresenta a implementação do circuito para geração de pulsos

complementares de gatilho (Vg1 e Vg4) em um dos braços e o ajuste do sinal a ser entregue

ao circuito driver.

Figura 10 – Geração de pulsos complementares para driver.

2.11 Proteções do Circuito

Para se implementar a proteção do retificador, foi realizada a amostra das seguintes

grandezas:

− Correntes de entrada (IsensA, IsensB, IsensC);

− Corrente no indutor Boost (Ilb);

− Tensão de saída (Voa).

A Figura 11 apresenta a implementação do comparador com histerese sugerido em Illa Font

(2009), circuito este que foi utilizado para detecção de sobrecorrente no indutor Lb2. O mesmo

circuito é utilizado para proteção das outras quatro grandezas acima citadas. Cada um dos

circuitos possui um LED vermelho para indicação de anormalidade.

Figura 11 – Circuito de proteção sobrecorrente no indutor Lb2.

As saídas dos cinco circuitos de proteção presentes na placa de condicionamento são

interconectadas gerando uma saída única de erro. Esta saída de erro é conectada a um

transistor que opera como chave eletrônica (região de corte e saturação), comutando para 3 V

na ocorrência de sobretensão ou sobrecorrente em qualquer um dos cinco circuitos de

proteção. Esta saída de erro é conectada a uma entrada do DSP para que este atue na proteção

do circuito em casos de anormalidade.

Para proteção das entradas do DSP, todas as entradas de sinais do DSP foram protegidas com

a utilização do CI limitador TL7726 da Texas Instruments. Sua função é limitar a faixa de

tensão das entradas de sinais do DSP entre 0,0 e 3,0 V.

A placa desenvolvida também conta com a utilização do sinal de erro dos circuitos drivers.

Na ocorrência deste tipo de erro, este sinal é encaminhado ao DSP para atuar na proteção do

circuito. Além disso, um LED vermelho acende na placa de condicionamento indicando falha

no circuito driver correspondente.

2.12 Interface com DSP

No modo on-board, conecta-se o F28335 controlCARD™ à placa de condicionamento através

do soquete DIMM100, conforme apresentado na Figura 12.

Figura 12 – Interface DSP e placa de condicionamento – Modo on-board.

No modo off-board, primeiramente conecta-se o Experimenter’s Kit USB e o F28335

controlCARD™ via soquete incluso no kit. Na sequência, o kit se comunica com a placa de

condicionamento via cabos.

2.13 Fonte de Alimentação

A placa de condicionamento de sinais é alimentada por uma Fonte Auxiliar Linear

desenvolvida em Illa Font (2009). Esta fonte fornece cinco fontes isoladas de 15 V, uma fonte

isolada de – 15 V e uma fonte isolada de 5 V. Para ser obtida a tensão de 3 V é utilizado um

CI regulador de tensão ajustável que foi incluído na placa de condicionamento de sinais.

2.14 Desenvolvimento da Placa de Circuito Eletrônico

O desenvolvimento do esquema elétrico e layout da placa foram realizados em software. O

roteamento das trilhas foi realizado por completo de forma manual devido a este ser o único

método que oferece controle total sobre as prioridades no posicionamento das trilhas. A placa

desenvolvida necessita de dois layers devido a sua complexidade e quantidade de

componentes.

2.15 Desenvolvimento da Programação para Aplicação do Controle

O programa para o controle do retificador será realizado no ambiente de programação Code

Composer Studio v5 fornecido pelo fabricante do kit de desenvolvimento. Entre as principais

características, este programa permite: criação de projetos com a construção dos programas

em linguagem assembly e linguagem C; compilação e depuração do programa; e visualização

de variáveis internas do DSP.

3. Resultados

A Figura 13 apresenta a placa desenvolvida. As dimensões finais da placa são 145,5 mm x

214,7 mm. As Figuras 14, 15 e 16 apresentam os principais resultados práticos do

funcionamento do conjunto. Em azul estão sinais de entrada na placa de condicionamento

(ISENSA1, VSINCA1) e em vermelho estão sinais submetidos ao DSP (ISENSA2, VSINCA2, DSC-PT).

Figura 13 – Placa desenvolvida.

VSINCA2

ISENSA2

ISENSA1

Figura 14 – Amostragem da corrente de entrada

IsensA.

VSINCA1

Figura 15 – Amostragem da tensão de entrada para

sincronismo VsincA.

DSC-PT

ISENSA1

Figura 16 – Atuação da proteção devido a uma sobrecorrente em IsensA.

4. Considerações Finais

O trabalho apresentou o desenvolvimento de uma placa de circuito eletrônico com

condicionamento de sinais e interface com DSP para aplicação de controle digital, sobretudo

em retificadores trifásico híbridos. O projeto sugerido possui como principais características:

flexibilidade para projetos de controle digital para retificadores trifásicos; capacidade da

rápida aquisição de dados; vasta capacidade de realização de cálculos e funções complexas; e

rápido tempo de resposta do controle à planta.

Destaca-se que a Eletrônica de Potência e as estruturas de controle digital possuem papel

fundamental no desenvolvimento de dispositivos na busca por melhoria da qualidade da

energia elétrica. É evidente que a implementação de circuitos de alta tecnologia como os

propostos neste trabalho são importantes, essencialmente quando se trata do aumento da

eficiência energética.

Com relação às contribuições do trabalho, espera-se que a placa desenvolvida possa ser

aplicada, não somente nos propósitos aqui explanados, mas sim que seja também utilizada em

outros retificadores trifásicos e estudos científicos que justifiquem o uso do controle digital.

Referências

BATISTA, F. A. B. Modulação Vetorial Aplicada a Retificadores Trifásicos PWM Unidirecionais. Teste

(Doutorado em Engenharia Elétrica). Programa de Pós-Graduação em Engenharia Elétrica, Universidade Federal

de Santa Catarina, Florianópolis, 2006.

ILLA FONT, C. H. Retificadores Trifásicos Híbridos Bidirecionais com Fator de Potência Unitário. 2009. 225

f. Tese (Doutorado) – Curso de Engenharia Elétrica, Universidade Federal de Santa Catarina – UFSC,

Florianópolis, 2009.

MUSSA, S. A. Controle de um Conversor CA-CC Trifásico de Três Níveis com Fator de Potência Unitário

Utilizando DSP. Florianópolis, 2003. Tese de Doutorado em Engenharia Elétrica – INEP, UFSC.

SANTOS, B. A. G. ; FONT, C. H. I. ; NASCIMENTO, C. B. Uma Análise Comparativa de Técnicas de

Controle de Corrente em um Retificador Trifásico Híbrido com Elevado Fator de Potência e Regeneração de

Energia. XVII Seminário de Iniciação Científica e Tecnológica da UTFPR – SICITE 2012, 2012.

SILVA, A. Fundamentos de Controle Clássico. Apostila. Instituto de Eletrônica de Potência, Departamento de

Engenharia Elétrica, Universidade Federal de Santa Catarina, Florianópolis, 2002.

TEXAS INSTRUMENTS. TMS320C2000TM Experimenter Kit Overview. Quick Start Guide. Literature

Number: SPRUFR5E. Disponível em <<www.ti.com>>, 2011.

TEXAS INSTRUMENTS. TMS320F28335, TMS320F28334, TMS320F28332, TMS320F28235,

TMS320F28234, TMS320F28232. Digital Signal Controllers (DSCs). Literature Number: SPRS439L.

Disponível em <<www.ti.com>>, 2012.

TOMASELI, L. C. Controle de um Pré-Regulador com Alto Fator de Potência o Controlador DSP

TMS320F243. Florianópolis, 2001. Dissertação de Mestrado em Engenharia Elétrica – INEP, UFSC.

TREDINNICK, M. R. A. da C. Modelagem e Simulação Discreta no Tempo de Sistemas Dinâmicos Contínuos

no Tempo. 2005. 36 f. Exame de Qualificação (Doutorado) – Instituto Nacional de Pesquisas Espaciais – INPE,

São José Dos Campos, 2005.