Disciplina de Microprocessadores

Curso de Engenharia Elétrica - UEL

José Alexandre de França

Londrina, 22 de outubro de 2001

1

2

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Índice Geral

CAPÍTULO 1 - VISÃO GERAL................................................................................................ 8

1.1

Um Pouco de História ............................................................................. 8

1.2

Componentes do Sistema.........................................................................10

1.3

Execução de Instruções..........................................................................13

1.4

Mais um Pouco Sobre a Arquitetura de von Neumann .........................................14

1.5

1.5.1.

Microprocessadores e a Memória Principal .....................................................15

Ordem dos Bytes ............................................................................................................................................ 15

1.6

Controladores de Dispositivos ...................................................................16

1.7

1.7.1.

Compartilhando as Informações .................................................................18

Pinagem e Encapsulamento............................................................................................................................ 18

1.8

Comentários .......................................................................................20

CAPÍTULO 2 - MICROPROGRAMAÇÃO ............................................................................. 21

2.1

Um Exemplo de Microarquitetura ...............................................................21

2.1.1.

Componentes Básicos .....................................................................................................................................22

2.1.1.1.

ALU e Deslocador .................................................................................................................................22

2.1.1.2.

Relógio (clock)........................................................................................................................................22

2.1.1.3.

Memória Principal..................................................................................................................................23

2.1.2. As Vias de Dados ............................................................................................................................................24

2.1.3. Microinstruções ..............................................................................................................................................26

2.1.4. Temporização de Microinstruções..............................................................................................................27

2.1.5. Seqüenciamento de Microinstruções .........................................................................................................29

2.2

2.2.1.

2.2.2.

Um Exemplo de Macroarquitetura...............................................................30

Pilhas .................................................................................................................................................................30

O Conjunto de Macroinstruções............................................................................................................. 31

2.3

Um Exemplo de Microprograma..................................................................33

2.3.1. A Microlinguagem de Montagem .................................................................................................................33

2.3.2.

Um Exemplo de Microprograma..............................................................................................................34

2.3.2.1.

3.3.2.1. Comentários sobre o Microprograma .................................................................................35

2.4

2.4.1.

2.4.2.

2.4.3.

2.4.4.

2.4.5.

Mais um Pouco Sobre Endereçamento...........................................................36

Endereçamento Imediato .............................................................................................................................36

Endereçamento Direto .............................................................................................................................36

Endereçamento de Registrador..............................................................................................................36

Endereçamento Indireto..........................................................................................................................37

Indexação ....................................................................................................................................................38

1

2.5

Nossa Macroarquitetura Real ................................................................... 38

2.5.1. Conjunto de Registradores .......................................................................................................................... 38

2.5.2.

Pinagem e Sinais de Barramento ............................................................................................................ 40

2.5.3.

Modos de Endereçamento ....................................................................................................................... 40

2.5.3.1.

Endereçamento Imediato (IMM) ...................................................................................................... 40

2.5.3.2.

Endereçamento Estendido (EXT).......................................................................................................41

2.5.3.3.

Endereçamento Direto (DIR)..............................................................................................................41

2.5.3.4.

Endereçamento Indexado (IND)........................................................................................................41

2.5.3.5.

Endereçamento Inerente (INH) ........................................................................................................41

2.5.3.6.

Endereçamento Relativo (REL) ...........................................................................................................41

2.5.4.

Conjunto de Instruções ........................................................................................................................... 42

2.6

Comentários ...................................................................................... 43

CAPÍTULO 3 - ENTRADA E SAÍDA......................................................................................50

3.1

E/S Programada ................................................................................. 50

3.2

Interrupção ...................................................................................... 51

3.2.1. Modo de Operação ......................................................................................................................................... 52

3.2.1.1.

Vetor de Interrupção .......................................................................................................................... 52

3.2.1.2.

Tempo de Latência ............................................................................................................................... 53

3.2.1.3.

Prioridade ............................................................................................................................................... 54

3.2.1.4.

Interrupções Mascaráveis e Não-Mascaráveis.............................................................................. 55

3.2.2.

O Controlador 8259A............................................................................................................................... 56

3.2.2.1.

Diagrama de Blocos .............................................................................................................................. 56

3.2.2.2.

Seqüência de Interrupção .................................................................................................................. 57

3.2.2.3.

Interfaceamento .................................................................................................................................. 58

3.2.2.4.

Programação........................................................................................................................................... 59

3.2.3.

Interrupções no 68HC11.......................................................................................................................... 59

3.2.3.1.

O vetor de interrupção ....................................................................................................................... 59

3.2.3.2.

Interrupção IRQ e XIRQ ................................................................................................................ 60

3.2.3.3.

Interrupção do Timer Overflow (TOI) ............................................................................................61

3.2.3.4.

Interrupções na placa EVB ................................................................................................................. 62

3.2.4.

Interrupções no IBM PC AT ................................................................................................................... 63

3.2.4.1.

O Vetor de Interrupção do IBM PC AT .......................................................................................... 63

3.2.4.2.

Trabalhando com Interrupção na Linguagem C .............................................................................. 64

3.3

3.3.1.

3.3.2.

3.3.3.

3.3.4.

3.3.5.

3.3.6.

E/S via DMA ..................................................................................... 67

Como o DMA funciona ................................................................................................................................... 68

Tipos e modos de transferências........................................................................................................... 68

Operação do controlador ......................................................................................................................... 69

Implementação de DMA no IBM PC e no PC/XT ................................................................................ 69

Implementação de DMA no PC AT......................................................................................................... 69

Gerenciando o controlador de DMA ...................................................................................................... 70

3.4

Interface de Comunicação Serial............................................................... 70

3.4.1. Especificações ................................................................................................................................................ 70

3.4.1.1.

Características Elétricas.................................................................................................................... 70

3.4.1.2.

Sinais de Controle e Handshake ........................................................................................................ 70

2

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

3.4.1.3.

Características Mecânicas.................................................................................................................. 71

CAPÍTULO 4 - CONVERSORES A/D E D/A......................................................................... 72

4.1

Discretização .....................................................................................72

4.2

Teorema da Amostragem ........................................................................72

4.3

Quantização.......................................................................................75

4.4

Codificação........................................................................................77

4.5

Recuperação do Sinal Codificado ................................................................78

4.6

4.6.1.

4.6.2.

4.6.3.

Critérios de Performance ........................................................................79

Resolução ..........................................................................................................................................................79

Velocidade ...................................................................................................................................................79

Linearidade..................................................................................................................................................80

4.7

4.7.1.

4.7.2.

Tipos de Conversores D/A .......................................................................80

Conversor D/A à Resistores Ponderados ..................................................................................................80

Conversor D/A à Rede R-2R....................................................................................................................82

4.8

4.8.1.

4.8.2.

Tipos de Conversores A/D .......................................................................83

Paralelo ou Flash .............................................................................................................................................83

Aproximações Sucessivas ........................................................................................................................84

CAPÍTULO 5 - PROJETO DE SISTEMAS MICROCONTROLADOS ................................... 86

5.1

5.1.1.

5.1.2.

5.1.3.

Principais Componentes de um Sistema Microprocessado ......................................86

Memória RAM ..................................................................................................................................................86

Memória EPROM .............................................................................................................................................87

Microcontrolador 68HC11.............................................................................................................................88

5.2

Interface entre o 68HC11 com Outros Dispositivos ..........................................88

5.3

Cristal Oscilador .................................................................................94

5.4

RESET.............................................................................................95

5.5

Projetos com o 80C31. ..........................................................................96

3

Índice de Figuras

Figura 1 – Uma pequena fração do ENIAC......................................................................................................................8

Figura 2 - A máquina original de von Neumann. .............................................................................................................9

Figura 3 - Diagrama de blocos de um sistema microprocessado. ............................................................................ 11

Figura 4 – Fluxo de dados de uma máquina de von Neumann típica.........................................................................15

Figura 5 – (a) Memória big endian. (b) Memória little endian. .................................................................................16

Figura 6 – Esquema de ligação de um dispositivo de E/S e um CPU, através de um controlador de

dispositivo. ...................................................................................................................................................................17

Figura 7 – Pinagem lógica de um MCU bastante simples (hipotético).....................................................................19

Figura 8 – (a) encapsulamento DIP, (b) encapsulamento PLCC, (c) encapsulamento PGA, (d) encapsulamento

SMD...............................................................................................................................................................................19

Figura 9 – Encaixe de um circuito integrado DIP em seu respectivo soquete. ................................................... 20

Figura 10 –(a) ALU e (b) deslocador utilizados no exemplo..................................................................................... 22

Figura 11 – (a) Relógio com 4 saídas em atraso. (b) O diagrama de temporização das saídas. ........................ 23

Figura 12 – Os registradores utilizados para acionar os barramentos de endereço e dados. ......................... 24

Figura 13 – As vias de dados da microarquitetura exemplo. ................................................................................... 25

Figura 14 – O layout e a descrição de alguns dos campos da microinstrução que controla as vias de dados

da Figura 13. ............................................................................................................................................................... 27

Figura 15 – O diagrama de blocos completo de nossa microarquitetura exemplo. ............................................. 28

Figura 16 – (a) Uma pilha. (b) A mesma pilha após o armazenamento da constante 5. .......................................31

Figura 18 – Comparações entre os endereçamentos direto e indireto. (a) Endereçamento direto. (b)

Endereçamento indireto. ......................................................................................................................................... 37

Figura 19 – Conjunto de registradores do 68HC11. ................................................................................................... 39

Figura 20 – Notação utilizada pela Tabela 4............................................................................................................... 42

Figura 21 – Esquema de compartilhamento de um pino de IRQ por até oito dispositivos. ............................... 53

Figura 22 – Seqüência temporal de um exemplo de múltiplas interrupções. (RSI = Rotina de Serviço de

Interrupção.).............................................................................................................................................................. 55

Figura 23 – Diagrama de blocos do 8259A.................................................................................................................. 56

Figura 24 – Interface padrão do 8259A com o barramento................................................................................... 58

Figura 25 – O 8259A utilizado em cascata. ................................................................................................................ 59

Figura 26 – Registrador OPTION. .................................................................................................................................61

Figura 27 – Registrador TFLG2. .................................................................................................................................... 62

Figura 28 – Registrador TMSK2.................................................................................................................................... 62

Figura 29 - (a) representação de um discretizador, (b) representação gráfica de um discretizador e (c)

sinal analógico (linha contínua) e sinal discreto (pontos grossos) . ................................................................ 73

Figura 30 – (a) sinal analógico f(t), (b) Transformada de Fourier de f(t), F(ω), (c) representação gráfica de

um discretizador de Nyquist, (d) Transformada de Fourier do discretizador de Nyquist, (e) sinal

discreto no tempo e em amplitude e (f) Transformada de Fourier do sinal discreto no tempo e em

amplitude..................................................................................................................................................................... 74

Figura 31 – (a) sinal discretizado, f(n), (b) Transformada de Fourier de f(n), (c) gráfico da função sinc, (d)

Transformada de Fourier da função sinc, (e) sinal analógico f(t) e (f) Transformada de f(t). .............. 75

Figura 32 – Diversos exemplos da Transformada de Fourier de um sinal amostrado a uma freqüência

inferior a de Nyquist................................................................................................................................................ 76

Figura 33 – Esboço da função de transferência de um filtro passa-baixas real (apenas as componentes de

freqüência positivas). ............................................................................................................................................... 76

Figura 34 – Quantização da temperatura em sete níveis de quantização. ........................................................... 77

Figura 35 – Processo de quantização e o erro intrínseco ao processo.................................................................. 78

4

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Figura 36 – Processo de quantização e codificação. ..................................................................................................78

Figura 37 – (a) sinal digitalizado, quantizado e codificado, (b) sinal na saída do conversor D/A e (c) sinal na

saída do filtro "suavizador".....................................................................................................................................79

Figura 38 – Conversão A/D com 4 bits de resolução.................................................................................................80

Figura 39 – Linha reta aparente adquirida com um conversor A/D e o gráfico do desvio dos postos

digitalizados em relação a linha reta real. ........................................................................................................... 81

Figura 40 – Característica ideal de um conversor A/D e característica de um A/D com uma linearidade

diferencial pobre (com um código faltando em 120 µs). ................................................................................... 81

Figura 41 – Conversor D/A à resistores ponderados.................................................................................................82

Figura 42 – (a) Conversor R-2R de 3 bits e (b) conversor R-2R com saída amplificada....................................82

Figura 43 – Diagrama de blocos de um conversor A/D Flash. .................................................................................84

Figura 44 - Conversor A/D de 16 bits baseado em dois conversores de 8 bits..................................................84

Figura 45 – Diagrama de blocos de um conversor A/D baseado em aproximações sucessivas. .......................85

Figura 46 – Pinagem física de uma chip de memória 6264. ......................................................................................86

Figura 47 – Gravador para a família de microcontroladores da Microchip. .........................................................87

Figura 48 – Pinagem do EPROM 2764. ..........................................................................................................................88

Figura 49 –(a) Todos os 52 pinos do 68HC11, (b) Os pinos mais importantes quando deseja-se interfacea-lo

com dispositivos externos, e (c) Configuração sugerida para alguns desses pinos.....................................89

Figura 50 – (a) Diagrama de tempo de um ciclo de escrita típico no 68HC11; (b) Diagrama de tempo de um

ciclo de leitura típico no 68HC11............................................................................................................................90

Figura 51 – Barramento de um sistema baseado no 68HC11. O 74HC373 é utilizado para “separar” as linhas

de endereço das linhas de dados............................................................................................................................90

Figura 52 – Interface entre o 68HC11 e uma memória 6264.................................................................................. 91

Figura 53 - Interface entre o 68HC11 e uma memória 6264. Neste caso, a memória possui endereço base

$0000...........................................................................................................................................................................92

Figura 54 – Interface entre o 68HC11 e uma memória 6264 (base $0000) e uma memória EPROM 2764

($E000)........................................................................................................................................................................92

Figura 55 - Interface entre o 68HC11 e uma memória 6264 (base $4000) e uma memória EPROM 2764

($E000). Neste caso, foi utilizado o 74HC138 para atribuir os endereços base. ......................................93

Figura 56 – Mapa de memória do 68HC11. ...................................................................................................................94

Figura 57 – (a) esquema de ligação do cristal oscilador no 68HC11. (b) sugestão para confecção da placa de

circuito impresso. ......................................................................................................................................................95

Figura 58 – Diversas configurações para RESET. ......................................................................................................96

Figura 59 – Pinagem do microcontrolador 80C31. ......................................................................................................96

Figura 60 – Sistema microprocessado baseado no 80C31. .......................................................................................96

Figura 61 - Sistema microprocessado baseado no 80C31 com espaços de endereçamentos diferentes para

dados e instruções.....................................................................................................................................................97

5

6

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 1 - Visão Geral

Índice de Tabelas

Tabela 1 – Exemplos dispositivos de E/S e a maneira de como eles representam as informações................. 17

Tabela 2 – O Conjunto de instruções do Mac-1. .........................................................................................................32

Tabela 3 – Significado dos bits do registrador CCR. ................................................................................................39

Tabela 4 – Conjunto de macroinstruções do 68HC11.................................................................................................44

Tabela 5 – Descrição dos pinos do 8259A. ..................................................................................................................57

Tabela 6 - Fonte de interrupção, vetor de interrupção e a sua máscara. ............................................................60

Tabela 7 – Conteúdo do vetor de interrupção da placa EVB....................................................................................63

Tabela 8 – Canais de interrupção dos dois controladores 8259A do PC AT e suas posições no vetor de

interrupção..................................................................................................................................................................64

Tabela 9 – Descrição de cada uma das posições do vetor de interrupção do PC AT..........................................67

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

7

Curso de Microprocessadores

Capítulo 1 - Visão Geral

1.1

Um Pouco de História1

O estímulo para o computador eletrônico foi a Segunda Guerra Mundial. O exército americano

precisava de tabelas de alcance para calibragem de mira de sua artilharia pesada, e achava que calculá-las

manualmente consumia muito tempo e era sujeito a erros.

John Mauchley, um desconhecido professor de física da Universidade da Pennsylvania, sabia que o

exército estava interessado em calculadoras mecânicas. Da mesma maneira que muitos cientistas da

computação que vieram depois dele, Mauchley apresentou um pedido de auxílio ao exército para

financiamento da construção de um computador eletrônico. A proposta foi aceita em 1943, e Mauchley e

seu aluno de pós-graduação, J. Presper Eckert, construíram um computador eletrônico que eles

denominaram ENIAC (Electronic Numerical, Integrator And Computer, ou seja, Computador e Integrador

Numérico Eletrônico). Ele era constituído de 18.000 válvulas e 1.500 relés. O ENIAC pesava 30 toneladas

e consumia 140 KW de potência. Arquiteturalmente, a máquina possuía 20 registradores, cada um capaz de

armazenar um número decimal de 10 dígitos. Sua programação era feita através de cerca de 6.000 chaves

multiposicionais e da interconexão de um grande número de soquetes através de um verdadeiro

emaranhado de cabos.

Figura 1 – Uma pequena fração do ENIAC.

A máquina só ficou pronta em 1946, quando já era muito tarde para ter qualquer uso em seus

objetivos originais. Entretanto, logo que a guerra acabou, Mauchley e Eckert obtiveram permissão para

organizar um curso de verão para descrever o trabalho deles para seus colegas cientistas. Aquele curso de

verão deu início a uma explosão de interesse na construção de grandes computadores digitais.

Após esse histórico curso de verão, muitos outros pesquisadores começaram a construir

computadores eletrônicos. O primeiro computador operacional foi o EDSAC (1949), construído na

Universidade de Cambridge, na Inglaterra, por Maurice Wilkes. Dentre outros, temos o JOHNIAC, na

Rand Corporation, o ILLIAC, na University of Illinois, o MANIAC, no Los Alamos Laboratory, e o WEIZAC,

no Weizmann Institute, em Israel.

Eckert e Mauchley começaram a construir uma nova máquina, o EDVAC (Electronic Discrete Variable

Automatic Computer, ou seja, Computador Automático Eletrônico de Variáveis Discretas), mas este

projeto foi seriamente afetado quando eles deixaram a Universidade da Pennsylvania para criar uma

companhia, a Eckert-Mauchley Computer Corporation, em Philadelphia (o Vale do Silício não existia ainda).

Após uma série de fusões, esta companhia tornou-se a atual Unisys Corporation.

1

A maior parte desta seção foi retirada do livro Organização Estruturada de Computadores, de Tanenbaun, ed. Prentice/Hall.

8

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 1- Visão Geral

Enquanto isso, uma das pessoas envolvidas no projeto ENIAC, John von Neumann, foi para o

Instituto de Estudos Avançados de Princeton, para construir sua própria versão do EDVAC, a máquina

IAS. Von Neumann era um gênio do tipo Leonardo da Vinci. Falava muitas línguas, era um especialista em

ciências físicas e matemáticas, e tinha total lembrança de tudo que ouvia, via ou lia. Era capaz de citar de

cor, literalmente, o texto de livros que ele havia lido anos antes. Quando ele se interessou por

computadores, já era o mais eminente matemático do mundo.

Uma das coisas óbvias para ele era que a programação de computadores com um grande número de

chaves e cabos era lenta, tediosa e inflexível. Ele começou a perceber que o programa poderia ser

representado em forma digital na memória do computador, juntamente com os dados.

Observou também que a desajeitada aritmética decimal utilizada pelo ENIAC, em que cada dígito

era representado por 10 válvulas (uma ligada e nove desligadas), poderia ser substituída por uma

aritmética binária paralela (válvula ligada ou desligada).

Seu projeto básico, agora conhecido como máquina de von Neumann, foi utilizado no EDSAC, o

primeiro computador com programa armazenado, e‚ ainda é a base de quase todos os computadores

digitais, até mesmo hoje, mais de meio século depois. Este projeto, e a máquina IAS, construída em

colaboração com Herman Goldstine, tem tido tanta influência que vale uma breve descrição. Um esboço da

arquitetura é dado na Figura 2.

Figura 2 - A máquina original de von Neumann.

A máquina de von Neuman possuía cinco partes básicas: a memória, a unidade lógica-aritmética, a

unidade de controle de programa e os equipamentos de entrada e saída. A memória consistia de 4.096

palavras, cada palavra possuindo 40 bits (0 ou 1). Cada palavra armazenava duas instruções de 20 bits ou

um inteiro de 39 bits com sinal. As instruções possuíam 8 bits dedicados a dizer o tipo da instrução, e 12

bits para especificar uma dentre 4.096 palavras de memória. Dentro da unidade lógico-aritmética, a

precursora da atual CPU (Central Processing Unit, ou seja, Unidade Central de Processamento), havia um

registrador interno especial de 40 bits denominado acumulador. Uma instrução típica adicionava uma

palavra de memória ao acumulador ou armazenava o acumulador na memória. A máquina não possuía

aritmética de ponto-flutuante, pois von Neumann achava que qualquer matemático competente deveria ser

capaz de acompanhar de cabeça a posição do ponto decimal (na realidade, ponto binário).

Em 1948, o transistor foi inventado no Bell Labs por John Bardeen, Walter Brattain e William

Shockley, pelo qual foram agraciados com o Prêmio Nobel de Física de 1956. Nos 10 anos seguintes, o

transistor revolucionou os computadores, e no final dos anos 50 os computadores a válvula estavam

obsoletos. O primeiro computador transistorizado foi construído no Lincoln Laboratory do MIT, uma

máquina de 16 bits baseada no Whirlwind I. Foi denominada TX-0 (Transistorized eXperimental computer

0, ou seja, computador transistorizado experimental 0), que visava meramente a ser um protótipo para

testar o TX-2, uma versão melhorada.

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

9

Curso de Microprocessadores

O primeiro circuito integrado comercial foi inventado por Jack Kilby da Texas Instruments

(http://www.ti.com) em 1958. Esta invenção foi tão significativa que Jack Kilby recebeu o maior prêmio da

área tecnológica dos EUA, a National Medal of Science. O circuito integrado possibilitou que dezenas de

transistores fossem colocados em uma única pastilha. Este encapsulamento tornou possível construir

computadores menores, mais rápidos e mais baratos que seus predecessores transistorizados.

Em 1968, a Intel Corporation (http://www.intel.com/) foi criada para fabricar pastilhas de memória.

Logo depois, ela foi contactada por um fabricante de calculadoras que queria uma CPU em uma única

pastilha para a sua calculadora, e por um fabricante de terminais que queria um controlador em uma única

pastilha para o seu terminal. A Intel produziu ambas as pastilhas, o 4004, uma CPU de 4 bits, e o 8008,

uma CPU de 8 bits. Estas foram as primeiras CPUs numa única pastilha do mundo.

A lntel não esperava outros interessados além dos clientes originais, de maneira que estabeleceu

uma linha de produção de baixo volume. Estavam errados. Houve um interesse tremendo, por isto

começaram a projetar uma pastilha de CPU de uso geral, que resolvesse o problema do limite de 16K de

memória do 8008 (imposto pelo número de pinos da pastilha). Este projeto resultou no 8080, uma pequena

CPU de uso geral. Este produto tomou a indústria de assalto, e instantaneamente tornou-se um item de

venda em massa. Porém, ao invés de vender milhares de unidades, como outros fabricantes, a Intel vendeu

milhões.

Dois anos mais tarde, em 1976, a Intel lançou o 8085, um 8080 encapsulado com alguns detalhes

extras de entrada/saída. Depois surgiu o 8086, uma verdadeira CPU de 16 bits numa única pastilha. O

8086 foi projetado para ter uma certa semelhança com o 8080, mas não era completamente compatível

com o 8080. O 8086 foi seguido pelo 8088, que possuía a mesma arquitetura que o 8086 e executava os

mesmos programas, mas possuía um barramento de 8 bits, ao invés de um barramento de 16 bits, o que o

tornava mais lento, porém mais barato que o 8086. Quando a IBM escolheu o 8088 para CPU do IBM PC

original, esta pastilha tornou-se rapidamente o padrão da indústria de computadores pessoais.

Nos anos seguintes, a Intel lançou o 80186 e o 80188, essencialmente novas versões do 8086 e

8088, respectivamente, mas contendo também uma grande quantidade de circuitaria de entrada/saída.

Nunca foram amplamente utilizados.

Com o passar dos anos, tornou-se possível colocar dezenas de milhares, depois centenas de milhares,

e finalmente milhões de transistores em uma única pastilha. Este avanço tornou os microprocessadores

mais rápidos e principalmente mais baratos. Deste modo, eles passaram a ser muito utilizados em sistemas

baratos, para implementar soluções poderosas, para problemas simples. Isto atraiu dezenas de fabricantes

a desenvolver centenas de famílias de microprocessadores, para milhares de consumidores. Cada

fabricante necessitava atrair a atenção dos consumidores. Evidentemente, isto poderia ser conseguido

desenvolvendo-se CPUs com características especiais que facilitassem o desenvolvimento de sistemas

microprocessados. Em busca disto, vários fabricantes começaram a dotar suas CPUs com dispositivos

extras. Por exemplo, uma pastilha com uma CPU e um conversor A/D2 poupa o projetista de adquirir e

interfacear um A/D externo, ou seja, o sistema fica mais barato e mais simples. Com o passar dos anos,

isto tornou-se comum e fez nascer uma nova classe de dispositivos: a dos microcontroladores (MCU's).

1.2

Componentes do Sistema

Sozinho, um computador não faz absolutamente nada. É tão inútil quanto um guarda-chuva em dia de

sol. Para fazer algo útil, precisamos programa-lo ou comprar (piratear) um programa para ele. Acredito que

você tenha uma noção de como um computador funciona e de como ele é programado. Neste curso, este

conhecimento será algo bastante positivo. Pois um computador nada mais é do que um sistema

microprocessado bastante complexo. Desse modo, não será difícil acreditar que, assim como um

computador, um sistema microprocessado geral é composto por uma CPU, memórias e dispositivos de

entrada e saída (E/S). Na Seção 1.1, vimos que na maioria dos sistemas estes blocos básicos relacionam-se

2

Um conversor A/D converte uma grandeza analógica em um número digital

10

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 1- Visão Geral

segundo uma arquitetura baseada no esquema da Figura 2. Esta arquitetura recebe o nome de Arquitetura

de von Neumann e é ilustrada na Figura 3.

Para entender a função de cada componente da Figura 3, temos que nos perguntar qual a função

primária de um sistema microprocessado. Como todo sistema, um sistema microprocessado

constantemente recebe dados e realiza um conjunto de operações sobre eles. Estas operações podem ser

operações lógicas (deslocamentos, operações booleanas, etc) ou aritméticas (somar, multiplicar, etc). Para

suportar tais instruções, um sistema microprocessado necessita de um bloco funcional que as execute.

Este bloco existe e é denominado de ALU (unidade lógica e aritmética). Você já deve saber que uma ALU

é um dispositivo digital que recebe dois operandos e realiza uma operação (escolhida dentre um conjunto

de possíveis) entre eles.

Os operandos recebidos pela ALU devem vir de algum lugar. Da mesma forma, o resultado da

operação deve também ser armazenado em algum lugar. Este “lugar” é um conjunto de registradores. Ou

seja, os registradores provêem operandos para a ALU e podem armazenar o resultado da operação.

Agora que temos um local para armazenar nossos operandos e podemos realizar operações,

necessitamos de um local para armazenar as instruções que definirão as operações realizadas pela ALU.

Note que, ao contrário dos dados armazenados nos registradores, estas instruções são utilizadas durante

todo o tempo no qual o sistema estiver ativo. Isto sugere a criação de um novo local para armazenar as

instruções. Este novo local, geralmente com uma capacidade de armazenamento muito maior que os

registradores, é chamado de memória principal. Eventualmente, podemos ter um conjunto de dados

(operandos) que é utilizado durante toda a execução de um programa (como uma tabela de conversão).

Além disso, podemos necessitar armazenar mais operandos que nossos registradores permitem. Por isto, a

memória principal também é utilizada para armazenar dados, porém dados mais significativos. É por esta

razão, que o conjunto de registradores de um sistema microprocessado é chamado de memória de

rascunho.

CPU

Unidade

de

Controle

Unidade

Lógica e

Aritmética

(ALU)

Dispositivos de entrada e saída

Registradores

Memória

Principal

Teclado

Display de

Cristal Líquido

Barramento

Figura 3 - Diagrama de blocos de um sistema microprocessado.

Na realidade, a característica mais marcante da arquitetura de von Neumann é a forma como a CPU

acessa os dados e as instruções. Nesta arquitetura, as instruções e os dados são buscados em tempos

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

11

Curso de Microprocessadores

distintos. Em oposição, arquiteturas como a de Harvard possibilitam que a CPU busque as instruções e os

dados ao mesmo tempo. Isto provoca um ganho substancial de performance. Contudo, provoca também um

aumento significativo nos custos de produção. Por esta razão, a Arquitetura de Harvard é muito pouco

utilizada.

Evidentemente, em um sistema microprocessado deve haver uma fonte externa que provenha dados

ao sistema. Além disso, após processar estes dados o sistema precisa apresentar um resultado ao mundo

exterior. Por exemplo, em um sistema de controle de temperatura em uma estufa, precisamos alimentar o

sistema de controle com dados sobre a temperatura dentro da estufa, para que este possa calcular uma

ação de controle e manter a temperatura constante. Dispositivos que desempenham estas tarefas são

chamados de dispositivos de entrada e saída, ou simplesmente, dispositivos de E/S. Exemplos são:

conversores A/D e D/A, teclado (keypad), visores de cristal líquido, push-button, porta serial, PIO, etc.

(Não se preocupe com os nomes, até o final do curso você ficará bastante íntimo deles.)

Registradores, memórias, operandos, instruções, dispositivos de E/S, todos estes itens fazem parte

do mesmo sistema. Logo, eles devem interagir entre si. Ou seja, durante a execução de um programa,

dados e instruções vêm (e vão) de (e para) todos os componentes do sistemas. Para que isto aconteça, eles

devem estar interligados por uma estrutura (caminho) comum. Este caminho é denominado barramento.

Acredito que o conceito de barramento já esteja bem definido em sua mente desde o curso

anterior. Contudo, quero reforçar o conceito comparando o barramento às estradas de uma cidade. Por

estas estradas, veículos de todos os tipos vão (e vem) de (e para) todos os lugares de uma cidade, de uma

forma bastante ordenada (pelo menos em tese), controlados por regras e sinais de controle bem

determinados. É exatamente assim que se comporta um barramento em um sistema microprocessado.

Neste ponto, pode parecer que todos os componentes do sistema estejam trabalhando em harmonia

e em perfeito sincronismo. Contudo, para que isto realmente aconteça é necessário a inclusão de mais um

componente. Este componente deve controlar todos os outros, deve sincronizar as operações e tomar

decisões baseadas em seus resultados. Este bloco é denominado unidade de controle.

Deve-se notar que, pelo que está escrito nos parágrafos anteriores, apenas a ALU, os registradores

e a Unidade de Controle estão diretamente envolvidas no processamento dos dados. Desse modo, estes

três blocos são agrupados para formar uma unidade maior e mais poderosa. É esta unidade que chamamos

de Unidade Central de Processamento (CPU).

Não se preocupe se a idéia de um circuito digital cuja função é determinada por um conjunto de

instruções, que contenha operandos trafegando como veículos em uma cidade, e de unidade funcionais

tomando decisões baseadas em acontecimentos anteriores, parecer abstrato a você. Na verdade, só quero

passar a visão do todo. As partes menores ficarão bem mais claras quando forem abordadas

individualmente de forma mais detalhada.

A seguir, vamos agora definir formalmente a função dos blocos funcionais da Figura 3.

Unidade de Lógica e Aritmética: como o próprio nome informa, realiza todas as operações lógicas e

aritméticas da CPU. Em tese, a complexidade das operações da ALU define o poder de processamento da

CPU, ou seja, uma CPU que contém uma ALU que execute um conjunto de operações fraco e irrelevante,

torna-se uma CPU muito pouco poderosa.

Registradores: são utilizados pela CPU como uma memória temporária que armazena os dados que

estão sendo (ou vão ser) utilizados pela a ALU, e os resultados intermediários das operações.

Memória Principal: armazena as instruções que serão executadas pela CPU e os dados mais

permanentes (aqueles que serão utilizados durante toda a execução do programa ou representem dados

importantes).

Dispositivos de E/S: fazem a interface entre o sistema e o mundo exterior. São eles que provêem os

dados utilizados pelo sistema e é através deles que os resultados são apresentados externamente.

Barramento: é um meio elétrico que provê um caminho para o tráfego de informações e os sinais de

controles necessários ao funcionamento do sistema. Toda a comunicação entre os componentes do sistema

microprocessado é realizada através deste dispositivo.

12

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 1- Visão Geral

Unidade Central de Processamento: formada pela unidade de controle, a ALU e o conjunto de

registradores, é responsável pela coordenação de todas as ações do sistema microprocessado.

1.3

Execução de Instruções3

Na Seção 1.2, soubemos que, para um sistema microprocessado desempenhar uma função útil,

precisamos fornecer um conjunto de instruções que devem ser executadas pela CPU. Estas instruções são

armazenadas na memória principal do sistema e são analisadas pela Unidade de Controle. Contudo, para que

a Unidade de Controle possa analisar a instrução, ela deve ser trazida da memória para dentro da CPU.

Sabendo que a unidade de controle precisará desta instrução apenas por um intervalo de tempo muito

curto, não é difícil aceitar que esta instrução fica armazenada em um registrador especial chamado

registrador de instrução (IR). Além disso, a Unidade de Controle precisa saber qual será a próxima

instrução a ser executada, ou seja, a UC tem que seguir a lógica de execução do programa. Para isto,

existe um outro registrador especial chamado de contador de programa (PC). Na verdade, o PC não conta

absolutamente nada, ele apenas aponta para a posição na memória principal, na qual localiza-se a próxima

instrução a ser executada. Podemos resumir as operações realizadas pela CPU durante a execução de uma

instrução em 8 passos:

1. Busca a próxima instrução da memória para o registrador de instrução.

2. Atualiza o contador de programa para que ele aponte para a instrução seguinte.

3. Determina o tipo da instrução.

4. Se a instrução usa dados da memória, determina onde eles estão.

5. Busca os dados, se houver algum, para registradores internos da CPU.

6. Executa a instrução.

7. Armazena os resultados em locais apropriados.

8. Volta ao passo 1 para iniciar a execução da próxima instrução.

Esta seqüência de passos é freqüentemente referida como o “ciclo busca-decodifica-executa". Ela

é o centro da operação de todos os microprocessadores.

Esta descrição de como uma CPU funciona pode facilmente ser representada por um algoritmo na

forma de um programa, por exemplo, em linguagem C ou assembler.

O fato de ser possível escrever um programa que pode imitar a função de uma CPU mostra que um

programa não precisa ser executado diretamente pelo hardware de uma CPU, constituído por um

emaranhado de circuitos elétricos. Em vez disso, um programa pode ser executado tendo-se um outro

programa que busca, analisa e executa suas instruções. Um programa que busca, analisa e executa as

instruções de outro programa é chamado de interpretador.

Esta equivalência entre processadores em hardware e interpretadores tem implicações importantes.

Após ter sido especificada a linguagem de máquina L para uma nova CPU (linguagem com a qual os

programadores poderão programa-la), o grupo projetista pode decidir se eles querem construir um

processador (uma ALU) para executar instruções em L diretamente ou se eles querem escrever um

interpretador. Se escolherem escrever um interpretador, também, precisam prover uma máquina para

executá-lo. Como um interpretador quebra a instrução de sua máquina-alvo (instruções em L) em pequenos

passos, a máquina na qual o interpretador é executado pode freqüentemente ser muito mais simples que o

processador para a máquina-alvo (CPU que, para o programador, parece poder executar as instruções em L

diretamente pelo hardware). Devido a razões econômicas, entre outras, os programas no nível de máquina

convencional da maioria das CPUs modernas são executados por um interpretador em execução em uma

máquina de nível 1 completamente diferente e muito mais primitiva, que chamamos nível de

microprogramação.

Acredito que o parágrafo anterior tenha parecido muito confuso para você. Por isso, observe um

exemplo bastante simples. Uma operação de subtração A-B pode ser representada por A-B = A+1+ B . Ou

Boa parte desta seção foi retirada do livro Organização Estruturada de Computadores, de Tanenbaun, ed. Prentice/Hall.

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

3

13

Curso de Microprocessadores

seja, conseguimos emular uma operação de subtração através de duas operações de soma e uma negação. O

mesmo pode ser aplicado a operações mais complexas, por exemplo, podemos simular uma multiplicação

com uma seqüência de somas e deslocamentos. Qual a vantagem disto? Simular uma operação a partir de

outras (geralmente mais simples), diminui a complexidade da CPU. Esta diminuição de complexidade

reflete-se em um projeto mais simples (do ponto de vista do projetista da CPU), um custo menor, e até um

consumo mais baixo. Contudo, não se pode querer que todas as vezes que um programador tenha de

executar uma simples multiplicação, ele inclua um algoritmo para emula-la. Por isto, a CPU tem que ter este

algoritmo já pronto para que ele possa ser utilizado sempre que o programador necessite. O conjunto de

algoritmos internos à CPU que emulam operações complexas a partir de operações mais simples é chamado

de microprograma.

O microprograma é escrito a partir de um conjunto de instruções que podem ser executadas

diretamente pelo hardware (através da ALU), chamadas de instruções de nível 1. Na verdade, este

conjunto de instruções não é acessível ao programador. Ele é utilizado apenas pelo projetista da CPU para

escrever o microprograma. Uma vez escrito, ninguém, nem mesmo o projetista, tem acesso ao

microprograma. Os programadores de microprocessadores, utilizam um conjunto de instruções,

geralmente chamado de linguagem assembler (ou linguagem de nível 2), que, como dito anteriormente, é

emulado pelo microprograma.

A coleção de todas as instruções disponíveis ao programador em um nível é chamada conjunto de

instruções daquele nível. O número de instruções de um conjunto de instruções varia de máquina para

máquina e de nível para nível. Para o nível de máquina convencional, por exemplo, o tamanho do conjunto de

instruções está tipicamente na faixa de 20 a 300. Um conjunto de instruções numeroso não é

necessariamente melhor que um pequeno. De fato, o oposto tende a ser verdade. Um conjunto de

instruções numeroso muitas vezes significa que as instruções não são muito gerais. Os compiladores para

linguagens de alto nível, como Ada, Modula 2 e Pascal, geralmente atuam melhor em máquinas com

conjuntos de instruções pequenos e bem escolhidos do que em máquinas com conjuntos de instruções

grandes e desajeitados. Máquinas com conjunto de instruções muito pequeno, chamadas máquinas RISC,

serão discutidas em breve. Estas máquinas não usam microprogramação e são extremamente rápidas.

Certifique-se de compreender que o conjunto de instruções e a organização do nível de

microprogramação são, de fato, o conjunto de instruções e a organização do hardware (CPU). O conjunto

de instruções e a organização do nível de máquina convencional são, em contraste, determinados pelo

microprograma, e não pelo hardware.

1.4

Mais um Pouco Sobre a Arquitetura de von Neumann4

A organização interna de parte de uma CPU von Neumann clássica é mostrada na Figura 4 em mais

detalhe. Esta parte é chamada de fluxo de dados e consiste em registradores (tipicamente 1 a 16) e da

ALU (unidade lógica e aritmética). Os registradores alimentam os dois registradores de entrada da ALU,

chamados de A e B na figura. Esses registradores mantêm as entradas da ALU enquanto ela está

executando a operação.

A própria ALU executa adição, subtração e outras operações simples com suas entradas, produzindo

um resultado no seu registrador de saída. Este resultado pode ser armazenado de volta em um registrador

e, de lá, de volta à memória, se desejado. O exemplo ilustra a adição.

As instruções podem ser divididas em três categorias: registrador-memória, registradorregistrador e memória-memória (muito raras). Instruções registrador-memória permitem que palavras

sejam buscadas da memória para registradores, onde podem ser usadas como entradas para a ALU em

instruções seguintes, por exemplo. Uma instrução típica registrador-registrador busca dois operandos dos

registradores, os traz para os registradores de entrada da ALU, executa alguma operação com eles e

armazena o resultado de volta em um registrador. A operação do fluxo de dados é o coração da maioria

4

Todo o conteúdo desta seção foi retirada do livro Organização Estruturada de Computadores, de Tanenbaun, ed. Prentice/Hall.

14

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 1- Visão Geral

dos sistemas. Extrapolando, ela define o que a máquina pode fazer. Voltaremos a este importante tópico

em breve.

Figura 4 – Fluxo de dados de uma máquina de von Neumann típica.

1.5

Microprocessadores e a Memória Principal

Não vou perder meu tempo explicando como funciona um chip de memória ou falando de bits e bytes.

Tenho certeza que estes conceitos estão bem claros para você. No entanto, gostaria de reforçar o

conceito de nibble.

No ínicio da era dos microprocessadores, surgiram várias pastilhas de 4 bits que eram usadas em

calculadoras e outros aparelhos digitais. Quando refiro-me a microprocessadores de 4 bits, quero dizer

que os operandos manipulados pela CPU eram de apenas de 4 bits. Em vista disto, a memória era

endereçada em grupos de 4 bits chamados de nibbles. Nos dias atuais, poucos são os fabricantes, como a

National Semiconductor (http://www.national.com/), que comercializam tais CPUs. Contudo, o termo nibble

ainda é muito utilizado. Principalmente, porque quando se programa um microprocessador é bem mais fácil

lidar com números em binário e em hexadecimal (você descobrirá isto com o tempo).

Mesmo com as CPUs de 8, 16, 32 ou 64 bits, ainda podemos pensar em termo de nibble. Assim, um

byte é composto de dois nibbles: o mais e o menos significativo. Além disso, como você deve saber, para

converter-se um número binário em hexadecimal, pode-se operar sobre os nibbles de um byte. Por

exemplo, o número 10101101b pode ser convertido para hexadecimal convertendo-se 1010b = Ah e 1101b =

Eh, ou seja, 10101101b = AEh. De forma semelhante, podemos converter números em hexadecimal para

binário.

1.5.1.

Ordem dos Bytes

Os bytes em uma palavra podem ser numerados da esquerda para a direita ou da direita para a

esquerda. A princípio, parece que esta escolha não é importante, mas, como veremos brevemente, tem

maiores implicações. Considere que desejamos armazenar na memória do sistema dois números de 16 bits

(A037h e 1224h) e uma string de 4 bytes (“ALEX”). Duas possibilidades são apresentadas na Figura 5. Na

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

15

Curso de Microprocessadores

Figura 5(a), os números e a string são armazenados da esquerda para a direita (como estamos

acostumados), como na família Motorola (http://www.mot.com/). Já na Figura 5(b), a parte mais

significativa de um operando de 16 bits é armazenada no endereço de memória mais alto (o que também

parece lógico), porém a string continua sendo armazenada da esquerda para a direita, como na família

Intel.

O primeiro sistema, onde primeiro é armazenado a parte mais significativa ("big"), é chamado de

sistema "big endian", em contraste com o "little endian" da Figura 5(b). Estes termos são devidos a

Jonathan Swift, cujo livro “Aventuras de Gulliver” satirizou políticos que fizeram guerra por causa da

disputa sobre se os ovos deviam ser quebrados do lado largo (big end) ou do lado estreito (little end). O

termo foi usado pela primeira vez no encantador artigo “On Holy Wars and a Plea for Peace" de Danny

Cohen (1980).

Os problemas com estas duas representações começam a ocorrer quando queremos trocar dados

entre duas CPUs diferentes. Por exemplo, suponha que um sistema big endian esteja conectado a um little

endian por um meio que permita a transferência de um byte por vez. Para realizar a conexão, poderíamos

transmitir os bytes começando no byte 0 e terminado no 3 (0, 1, 2, 3, 4, 5, 6, 7). Neste caso, as posições

de memória do little endian seriam idênticas as do big endian. Com isto, a string ficaria na ordem correta,

mas os números não. Caso trocássemos a ordem de envio dos dados (1, 0, 3, 2, 5, 4, 7, 6) teríamos os

números corretos, mas a string não.

Endereço

Big endian

Endereço

Little endian

0

A0h

37h

0

37h

A0h

2

12h

24h

2

24h

12h

4

‘A’

‘L'

4

‘A’

‘L'

6

‘E’

‘X’

6

‘E’

‘X’

(a)

(b)

Figura 5 – (a) Memória big endian. (b) Memória little endian.

Quero que você termine esta seção com a idéia clara de que a falta de um padrão para a ordem dos

bytes é um grande problema na troca de dados entre CPUs diferentes.

1.6

Controladores de Dispositivos

Como dito na Seção 1.2, a CPU precisa receber dados e enviar resultados para o “mundo exterior”.

Você já sabe que isto é feito pelos dispositivos de E/S. Contudo, os tipos de dispositivos que podem ser

utilizados dependem da aplicação e são infinitos. Além disso, a maneira como os diversos tipos de

dispositivos representam uma informação também é infinita. A título de exemplo, são apresentados na

Tabela 1 alguns dispositivos de E/S e a maneira que eles representam as informações.

Evidentemente, seria muito difícil para o projetista realizar a interface entre o microprocessador e

todos esses dispositivos, em vista das diferentes formas de representar a informação. Por isto, centenas

de fabricantes comercializam dispositivos que realizam a interface entre a CPU e os dispositivos de E/S.

Estes dispositivos são chamados de Controladores de Dispositivos.

Um controlador de dispositivo faz com que a operação de E/S seja realizada (quase) como uma

leitura/escrita na memória. De um lado, os controladores de dispositivos são conectados ao dispositivo de

E/S da maneira adequada. Do outro, os controladores de dispositivos são conectados ao barramento do

sistema. Desse modo, a CPU pode usar as linhas de endereço e os sinais de controle (WR/ RD , CS , etc)

para receber e enviar as informações aos dispositivos de E/S.

Na verdade, isto só é completamente correto se a CPU utilizar E/S mapeada em memória, ou seja, as

mesmas instruções usadas para acessar a memória lêem/escrevem dados nos controladores de dispositivos

(CD). Em outras CPUs, como as da família Intel, existem instruções próprias para trabalhar com E/S.

Estas instruções podem desativar um pino de saída da CPU [algumas vezes chamado de MREQ

16

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 1- Visão Geral

(REQuisição de Memória)] para avisar que trata-se de uma leitura/escrita em um CD. O sinal deste pino

deve então ser incluído na lógica de seleção dos chips de memória e dos controladores de dispositivos.

Tipo de Dispositivo

Representação da Informação

Serial

Representa uma palavra binária de n bits através de uma saída (ou entrada)

digital de um único pino, um bit por vez. A palavra é identificada observando-se

o estado do pino em n instantes de tempo.

Paralelo

Representa uma palavra binária de n bits através de uma saída (ou entrada)

digital de n pinos, n bits por vez. A palavra é identificada observando-se o

estado dos n pinos em um único instante de tempo.

Transdutores Analógicos Representam uma grandeza física qualquer, através de uma grandeza elétrica

(tensão, corrente, resistência, potência, etc), geralmente na forma analógica.

Teclado

Representam uma tecla através da sua localização linha-coluna em uma matriz

de teclas.

Visor de Caracteres

Representa um caractere através de um conjunto de pontos em uma matriz de

pontos.

Tabela 1 – Exemplos dispositivos de E/S e a maneira de como eles representam as

informações.

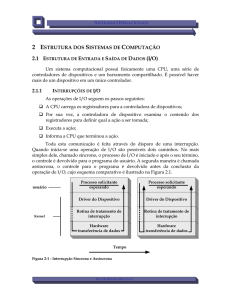

A CPU interage com um controlador de dispositivos através de um conjunto de registradores

internos ao controlador. Estes registradores são divididos em três categorias: registradores de

configuração, registradores de status e registradores de dados, como é ilustrado na Figura 6.

É através dos registradores de configuração que a CPU diz ao controlador como quer que o

dispositivo de E/S trabalhe. Ela pode definir, por exemplo, que os caracteres de um display de cristal

líquido tenham uma dimensão de 5x7 pontos.

Figura 6 – Esquema de ligação de um dispositivo de E/S e um CPU, através de um

controlador de dispositivo.

Os registradores de status são utilizados pela CPU para saber o andamento da operação de E/S ou a

sua configuração. Em um dispositivo serial, por exemplo, tem-se que verificar se o dado anterior já foi

enviado com sucesso antes de enviar o próximo dado. Além disso, através desses registradores a CPU pode

saber se existe um dado novo em um dispositivo de entrada.

É através dos registradores de dados que a CPU envia e recebe os dados de um dispositivo. Uma

leitura em um desses registradores é equivalente a receber um dado do dispositivo, já uma escrita,

corresponde ao envio de um dado.

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

17

Curso de Microprocessadores

Por último, devemos saber que quando utilizamos dispositivos de E/S, como regra geral, primeiro a

CPU deve acessar os registradores de controle para configurar o dispositivo de E/S. Em seguida, caso

quisermos enviar ou receber dados, a CPU precisa ler as informações contidas nos registradores de status.

Só assim, ela poderá receber ou enviar os dados desejados, através do registrador de dados.

Preste atenção! No parágrafo anterior, falei que sempre que desejarmos receber um dado de um

dispositivo de E/S, a CPU precisa verificar o registrador de status. Agora, imagine um sistema que

contenha uma infinidade de dispositivos de E/S. Neste caso, a CPU gastaria a maior parte do tempo de

processamento verificando se existe dados novos em seus dispositivos. Na maior parte das vezes, a

resposta seria negativa. Isto significa que a maior parte do tempo de processamento seria perdida. Para

evitar esta tragédia, em alguns casos, o próprio controlador de dispositivo avisa a CPU quando existe um

dado novo no dispositivo de E/S. Quando recebe este aviso, a CPU para o que está fazendo e realiza a

operação de E/S. Este aviso é feito através da ativação de um sinal de controle do barramento chamado

de sinal de interrupção. No Capítulo 3, estudaremos está técnica de E/S em mais detalhes.

1.7

Compartilhando as Informações

Vimos até aqui a maioria dos componentes de um sistema microprocessado. Contudo, para que eles

realmente façam parte de um sistema, é necessário que estejam interligados através de um caminho

comum (trilhas em uma placa de circuito impresso, fios elétricos, fibra ótica, ou qualquer outra coisa que

inventaram ou venham a inventar). Como você deve estar imaginando, este caminho comum é o barramento.

Podem estar conectados a um barramento os pinos de saída de diversos dispositivos elétricos. Por

isto, o barramento é dito um recurso compartilhado. Além disso, para que um dispositivo possa ser

conectado ao barramento (sem “torrar” os pinos de saída de todos os outros), é necessário que o mesmo

tenha saídas tri-state (por favor, tente lembrar-se disto). Isto também significa que, em um mesmo

instante de tempo, apenas os pinos de saída de um dispositivo podem estar conectados ao barramento, ou

seja, o barramento suporta apenas um mestre por vez. Chama-se mestre o dispositivo que está escrevendo

dados no barramento. Já o dispositivo a que se destina os dados, chama-se escravo. Observe que esta

limitação não se aplica aos escravos, isto é, podem haver mais de um escravo por vez.

Você já sabe como realizar operações de Leitura/Escrita em um chip de memória. Um chip deste

tipo contém pinos de endereço, dados e controle (WR/ RD , CS , etc). Estes pinos também são comuns aos

outros componentes de um sistema microprocessado. Logo, os sinais que fazem parte de um barramento

também podem ser divididos nestes três grupos: endereço, dados e controle. Na Seção 1.6, vimos que um

controlador de dispositivo pode enviar um sinal de interrupção para a CPU. Este sinal também é

transmitido pelo barramento. Isto que dizer que neste curso você verá outros sinais, além dos quais você

já está acostumado (da sua experiência com chips de memória).

1.7.1.

Pinagem e Encapsulamento

A pinagem lógica de uma CPU geral pode parecer-se com a da Figura 7. A pinagem real pode ser

diferente. Por exemplo, em 99,99% (100% é um valor muito perigoso) das CPUs, os pinos de dados são

multiplexados com os de endereço. Isto acontece porque os pinos de dados e os pinos de endereço nunca

são necessários em um mesmo instante (basta usarmos alguns 74373s para sustentar o endereço enquanto

recebe/envia o dado). Além disso, uma CPU com menos pinos é uma CPU mais barata.

Muito pode ser dito sobre um MCU observando-se apenas a sua pinagem. Principalmente com relação

aos pinos de dados e endereço. Pois o poder de processamento de uma CPU é intimamente ligado com a

quantidade de pinos de endereço e de dados que ela possui. Quanto maior o número de pinos de dados,

maior será a velocidade da CPU, a sua complexidade e o seu custo final. Além disso, o número de bits dos

registradores de uma CPU, geralmente, é igual ao número de pinos de dados. Evidentemente, quanto maior

a capacidade dos registradores maior o poder de processamento (velocidade) da CPU. Em muitas

aplicações, a velocidade é uma fator importantíssimo.

Sistemas que trabalham com grande quantidade de dados exigem grande quantidade de memória.

Desde que, para endereçar 2n bytes uma CPU necessita de n pinos de endereço, o número de linhas de

18

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 1- Visão Geral

endereço também é um fator limitante. Contudo, quando trabalha com endereços uma CPU precisa realizar

operações de soma, subtração, deslocamentos, etc. Por isso, aumentando-se o número de bits dos

endereços com os quais a CPU trabalha, aumenta-se também a complexidade dessas operações. Por isso,

uma CPU com um grande número de linhas (pinos) de endereço, geralmente, é muito poderosa e altamente

complexa.

Figura 7 – Pinagem lógica de um MCU bastante simples (hipotético).

Apesar da multifunção de alguns pinos, algumas CPUs apresentam uma quantidade enorme de pinos.

(Isto deixa os fabricantes realmente malucos na hora de encapsular o circuito integrado.) Por isso, com o

passar dos anos (e o aumento dos pinos), foram surgido vários tipos de encapsulamento. Alguns, são

apresentados na Figura 8.

(a)

(b)

(c)

(d)

Figura 8 – (a) encapsulamento DIP, (b) encapsulamento PLCC, (c)

encapsulamento PGA, (d) encapsulamento SMD.

A maior parte dos pinos de uma CPU são compostos pelos pinos de endereço. As CPUs mais simples

possuem no máximo 20 linhas de endereço. Essas CPUs podem facilmente ser enc1apsuladas em um

encapsulamento DIP (Dual in Parallel) de 40 pinos, Figura 8(a). A CPU mais conhecida que utiliza este

encapsulamento talvez seja a Intel 8088.

É importante lembrar que as CPUs nem sempre são soldadas sobre a placa de circuito impresso.

Solda-se primeiro um soquete na placa e encaixa-se o circuito integrado neste soquete, Figura 9.

Como dito na Seção 1.1, os microcontroladores possuem diversos dispositivos de E/S encapsulados

em um único chip. De fato, os microcontroladores (MCUs) são, por si só, um sistema microprocessado. Os

MCUs precisam de um encapsulamento que suporte mais pinos, por isto, muitos deles utilizam o

encapsulamento PLCC (Plastic Leadless Chip Carrier), um encapsulamento plástico barato que tem

terminais saindo pelos quatro lados do CI, na maioria das vezes dobrado para baixo, de modo a encaixar-se

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

19

Curso de Microprocessadores

perfeitamente em um soquete apropriado, Figura 8(b). Este encapsulamento torna a retirada do chip deste

soquete uma tarefa muito delicada.

Figura 9 – Encaixe de um circuito integrado DIP em seu respectivo soquete.

Nos encapsulamento da Figura 8(a) e da Figura 8(b), cada terminal do chip recebe um número de

identificação próprio. Por exemplo, chamamos "pino 20" ao vigésimo terminal contando a partir do

primeiro.

O terceiro tipo de padrão de pinagem que existe para circuitos integrados é o PGA (Pin Grid Array),

em que os terminais saem por baixo do circuito integrado (Figura 8(c)), formando linhas e colunas que são

referidas não mais por uma numeração seqüencial, mas sim por uma numeração baseada em linhas e

colunas, como em uma batalha naval (por exemplo, chamamos de C3 o terminal localizado na interseção da

terceira linha com a terceira coluna), pois agora a quantidade de terminais é imensa.

Existe ainda um quarto tipo de invólucro, chamado PQFP (Piastic Quad Fiat Packa,ge), em que os

terminais saem lateralmente pelos quatro cantos do invólucro (Figura 8(d)). Diferentemente do PLCC, que

é projetado para ser encaixado em soquetes apropriados, o PQFP é projetado para ser soldado

diretamente sobre a placa de circuito impresso com uma técnica especial, chamada SMD (Surface

Mountage Devices - Dispositivos em Montagma de Superfície). Por isso, o encapsulamento PQFP é mais

conhecido como encapsulamento SMD.

A técnica SMD também está relacionada com a disposição dos terminais de um circuito integrado e

permitiu a diminuição do circuito como um todo em uma placa de circuito impresso. Esta técnica consiste

em soldar diretamente um circuito integrado sobre a placa de circuito impresso através de calor indireto

utilizando, para isso, modernos equipamentos de automação e robótica. Isto faz com que os circuitos

sejam menores por um simples motivo: são os terminais e o encapsulamento que são os responsáveis pela

maior parte do tamanho de um CI. Com esta técnica, o tamanho do encapsulamento é reduzido

consideravelmente, bem como os terminais. Em uma grande linha de montagem, tais circuitos são soldados

automaticamente por máquinas autômatas após a confecção da placa de circuito impresso. A grande

maioria dos circuitos integrados possuem versões em SMD, mesmo os circuitos integrados mais antigos em

MSI e LSI. Com isto, temos aparelhos e circuitos cada vez menores – leia-se aí qualquer tipo de circuito

eletrônico como aparelhos de videocassete, aparelhos de controle remoto, etc.

1.8

Comentários

Pronto! Você já sabe o que é um sistema microprocessado. Mais ainda, você sabe as partes que o

compõem e com elas relacionam-se. Os capítulos que seguem, simplesmente, descrevem bem mais

detalhadamente este relacionamento. Além disso, nos ensina como projetar nosso próprio sistema

microprocessado. Para isto, procurei fornecer a maior quantidade de informação possível. No entanto,

devido a grande variedade de microprocessadores e microcontroladores existentes no mercado, tenho

certeza que não será tudo (se é que “tudo” realmente existe). Como já disse, um fato está do nosso lado: a

filosofia de todas as CPUs é a mesma, o que muda entre uma família e outra é a maneira de fazer a mesma

coisa. Algumas dessas maneiras serão discutidas quando falarmos sobre arquiteturas avançadas de

microprocessadores.

20

Universidade Estadual de Londrina – Professor José Alexandre de França - http://www.josealexandre.rg3.net/

Capítulo 2- Microprogramação

Capítulo 2 - Microprogramação5

O limite entre hardware e software não é bem definido e, além disso, está constantemente se

alterando. Os primeiros computadores tinham instruções para operações aritméticas, booleanas,

deslocamentos, comparações, entre outras, que eram executadas diretamente pelo hardware. Para cada

instrução, um circuito especifico de hardware estava presente para executá-la. Poder-se-ia, pelo menos

em princípio, desparafusar o painel traseiro e apontar os componentes eletrônicos usados pela instrução

de divisão.

Nas CPUs de hoje, não é mais possível isolar os circuitos de divisão, porque não existem circuitos de

divisão. Todas as instruções disponíveis no nível de máquina convencional (por exemplo, instruções

aritméticas, booleanas, deslocamentos, comparações e MCUs) são executadas passo a passo por um

interpretador executado no nível de microprogramação. O equivalente atual de olhar para os circuitos de

divisão é obter uma listagem do microprograma e procurar pela parte que interpreta as instruções de

divisão.

Embora programas em qualquer nível possam ser executados por um software interpretador, e

embora este interpretador possa, também, ser executado por outro interpretador, essa hierarquia não

pode prosseguir indefinidamente. No nível mais baixo, deve existir fisicamente uma máquina em hardware,

com circuitos integrados e objetos "sólidos" similares. Neste capítulo, iremos estudar como os

componentes eletrônicos são controlados pelo microprograma e como este interpreta o nível de máquina

convencional. Em breve, estudaremos uma classe de máquinas que não são microprogramadas (máquinas

RISC6).