CEFET-RS

Curso de Eletrônica

3.1 - Memória DRAM

Organização de Computadores

Profs. Roberta Nobre & Sandro Silva

[email protected] e [email protected]

Estrutura básica da DRAM

LSB

CAS

Endereço

Real

Controlador

de

Memória

MSB

Decodificador

de

Linhas

RAS

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.2

Decodificador de

Colunas

Matriz

de

Células

MSB - Most Significant Bits

LSB - Least Significant Bits

CAS - Column Address Select

RAS - Row Address Select

Prof. Roberta Nobre & Sandro Silva

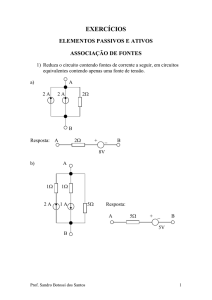

Leitura da DRAM

Tempo de acesso típico: 60ns a 70ns

RAS

CAS

Address

end

linha

end

coluna

WE

Data

dado

1º O controlador de endereços gera os bits mais significativos do endereço;

2º O controlador de endereços gera o sinal RAS;

3º O controlador de endereços gera os bits menos significativos do endereço;

4º O controlador de endereços gera o sinal CAS;

5º A memória libera o dado.

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.3

Prof. Roberta Nobre & Sandro Silva

Escrita da DRAM

Tempo de acesso típico: 60ns a 70ns

RAS

CAS

Address

end

linha

end

coluna

WE

Data

dado

1º O controlador de endereços gera os bits mais significativos do endereço;

2º O controlador de endereços gera o sinal RAS;

3º O controlador de endereços gera os bits menos significativos do endereço;

4º O controlador de endereços gera o sinal CAS;

5º O dado é enviado para a memória;

6ºCEFETRS

O controlador

de endereços gera o sinal WE.

- Eletrônica

Organização de Computadores

unidade 03.1.4

Prof. Roberta Nobre & Sandro Silva

Refresh da DRAM

RAS

CAS

Address

end

linha

end

coluna

WE

Data

dado

Sempre que ocorre um

endereçamento de memória,

ocorre refresh em toda linha

acessada.

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.5

RAS

CAS

Address

end

linha

Prof. Roberta Nobre & Sandro Silva

FPM DRAM

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.6

Prof. Roberta Nobre & Sandro Silva

FPM DRAM

RAS

CAS

Address

end

linha

Data

end

coluna

end

coluna

end

coluna

dado

dado

end

coluna

dado

dado

O endereço de linha e o sinal RAS é mantido e o endereço de

coluna e o sinal CAS é alterado a cada acesso à memória.

Ciclo: 7-3-3-3 (70ns) ou 6-3-3-3 (60ns)

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.7

Prof. Roberta Nobre & Sandro Silva

VRAM

http://en.wikipedia.org/wiki/Video_RAM#Video_DRAM_.28VRAM.29

•Memória DRAM específica para utilização na placa de vídeo.

•Criada em 1980 (F. Dill and R. Matick )

•Variação da DRAM com porta de acesso DUAL

•pode ser acessada pela CPU e pelo processador de vídeo simultaneamente

•Porta de leitura e escrita para acesso da CPU

•Porta de leitura para acesso pelo processador de vídeo

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.8

Prof. Roberta Nobre & Sandro Silva

EDO DRAM

RAS

CAS

Address

end

linha

Data

end

coluna

end

coluna

dado

end

coluna

dado

end

coluna

dado

dado

A saída de dados é bufferizada, assim o tempo que o dado

fica disponível é maior permitindo a redução do tempo entre

os acessos.

Ciclo: 7-2-2-2 (70ns) ou 6-2-2-2 (60ns)

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.9

Prof. Roberta Nobre & Sandro Silva

FPM DRAM

SIMM – Single In line Memory Module

Barramento de 8 bits

30 pinos

72 pinos

Barramento de 32 bits

SIMM – Single In line Memory Module

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.10

Prof. Roberta Nobre & Sandro Silva

FPM DRAM

SDRAM

DIMM

168 pinos

DDR SDRAM

DIMM

184 pinos

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.11

Prof. Roberta Nobre & Sandro Silva

BEDO DRAM

Address

end

linha

Data

end

coluna

dado

dado

dado

dado

Possui um um contador interno que permite operação em

modo rajada de 4 ciclos.

Ciclo: 6-1-1-1 (60ns)

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.12

Prof. Roberta Nobre & Sandro Silva

SDRAM

• Circuito interno reprojetado para obter os dados disponíveis a cada ciclo

de clock;

• Pipeline interno para realizar novo acesso antes do primeiro ser

processado pelo sistema externo;

• Sincronismo pelo clock do sistema;

• Contador interno para a geração de endereços consecutivos;

• Tempo de acesso: 7,5ns a 15ns;

• Ciclo de operação: 5-1-1-1;

Decodificador

de

Linhas

Decodificador

de comandos

Matriz

de

Células

Decodificador

de colunas

Contador

Dados

clock

endereço

Controlador

de memória

CEFETRS - Eletrônica

Organização de Computadores

Decodificador

de

Linhas

unidade 03.1.13

Matriz

de

Células

Prof. Roberta Nobre & Sandro Silva

DDR SDRAM

• É uma SDRAM que realiza um acesso na subida do clock

e outro acesso na descida do clock;

• Era utilizada somente em PCs não baseados em

processadores Intel;

• Barramento de 64bits

•Ex: PC-1600 Æ CLK: 100MHz Æ 1600MB/s

PC-2100 Æ CLK: 133MHz Æ 2100MB/s

• DDR2 Î 3200MB/s a 8500MB/s

• DDR3 Î 6,4GB/s a 12,8GB/s

CEFETRS - Eletrônica

Organização de Computadores

http://en.wikipedia.org/wiki/DDR_SDRAM

unidade 03.1.14

Prof. Roberta Nobre & Sandro Silva

DDR2

Standard

name

Memory

clock

Cycle

time

I/O Bus

clock

Data transfers per

second

Module

name

Peak transfer

rate

DDR-200

100 MHz

10 ns

100 MHz

200 Million

PC-1600

1600 MB/s

DDR-266

133 MHz

7.5 ns

133 MHz

266 Million

PC-2100

2100 MB/s

DDR-300

150 MHz

6.67 ns

150 MHz

300 Million

PC-2400

2400 MB/s

DDR-333

166 MHz

6 ns

166 MHz

333 Million

PC-2700

2700 MB/s

DDR-400

200 MHz

5 ns

200 MHz

400 Million

PC-3200

3200 MB/s

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.15

Prof. Roberta Nobre & Sandro Silva

DDR2

Standard

name

Memory

clock

Cycle

time

I/O Bus

clock

Data transfers per

second

Module

name

Peak transfer

rate

DDR2-400

100 MHz

10 ns

200 MHz

400 Million

PC2-3200

3200 MB/s

DDR2-533

133 MHz

7.5 ns

266 MHz

533 Million

DDR2-667

166 MHz

6 ns

333 MHz

667 Million

DDR2-800

200 MHz

5 ns

400 MHz

800 Million

DDR2-1066

266 MHz

3.75 ns

533 MHz

1066 Million

DDR2-1300

325 MHz

3.1 ns

650 MHz

1300 Million

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.16

PC2-4200

PC2-4300

PC2-5300

PC2-5400

PC2-6400

PC2-8500

PC2-8600

PC2-10400

4266 MB/s

5333 MB/s

6400 MB/s

8533 MB/s

10400 MB/s

Prof. Roberta Nobre & Sandro Silva

DDR3

Standard

name

Memory

clock

Cycle

time

I/O Bus

clock

Data transfers per

second

Module

name

Peak transfer

rate

DDR3-800

100 MHz

10 ns

400 MHz

800 Million

PC3-6400

6400 MB/s

DDR3-1066

133 MHz

7.5 ns

533 MHz

1066 Million

PC3-8500

8533 MB/s

DDR3-1333

166 MHz

6 ns

667 MHz

1333 Million

PC3-10600

10667 MB/s

DDR3-1600

200 MHz

5 ns

800 MHz

1600 Million

PC3-12800

12800 MB/s

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.17

Prof. Roberta Nobre & Sandro Silva

PC2-6400 com dissipador de calor

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.18

Prof. Roberta Nobre & Sandro Silva

Rambus DRAM

• Era utilizada nos PCs com processadores Intel (1999 a 2002);

• N64 (Nintendo), PlayStation2 e PlayStation3 (Sony)

• Operam com canal estreito: 16 bits

• Clock: 400MHz (1x);

• Duas transferências por ciclo (acessos de até 1,6GB/s);

http://en.wikipedia.org/wiki/RDRAM

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.19

Prof. Roberta Nobre & Sandro Silva

RAMBUS

Module Name

DataBus

Memory clock

transfer data rate

PC600

16-bit, single channel

300 MHz

1200 MB/s

PC700

16-bit, single channel

355 MHz

1420 MB/s

PC800

16-bit, single channel

400 MHz

1600 MB/s

PC1066 (RIMM 2100)

16-bit, single channel

533 MHz

2133 MB/s

PC1200 (RIMM 2400)

16-bit, single channel

600 MHz

2400 MB/s

RIMM 3200

32-bit, dual channel

400 MHz

3200 MB/s

RIMM 4200

32-bit, dual channel

533 MHz

4200 MB/s

RIMM 4800

32-bit, dual channel

600 MHz

4800 MB/s

RIMM 6400

32-bit, dual channel

800 MHz

6400 MB/s

CEFETRS - Eletrônica

Organização de Computadores

unidade 03.1.20

Prof. Roberta Nobre & Sandro Silva