Repescagem do 1º Teste

PROJECTO, TESTE E FIABILIDADE DE SISTEMAS ELECTRÓNICOS

Mestrado em Engenharia Electrónica (MEE)

10 de Julho de 2008

Duração: 1:30 horas

Secção I

Nesta secção, por cada resposta errada será descontado 1/3 da cotação da pergunta.

Pergunta

Cotação

1.1

1.1

1

1.2

1

1.3

0,5

1.4

0,5

1.5

0,5

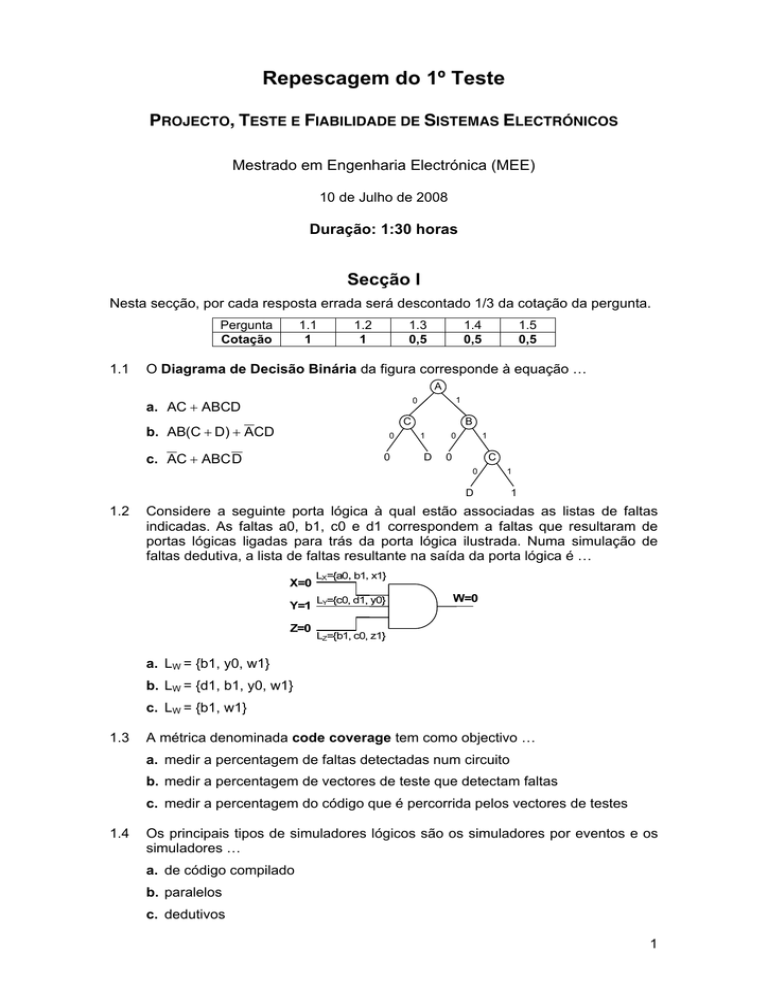

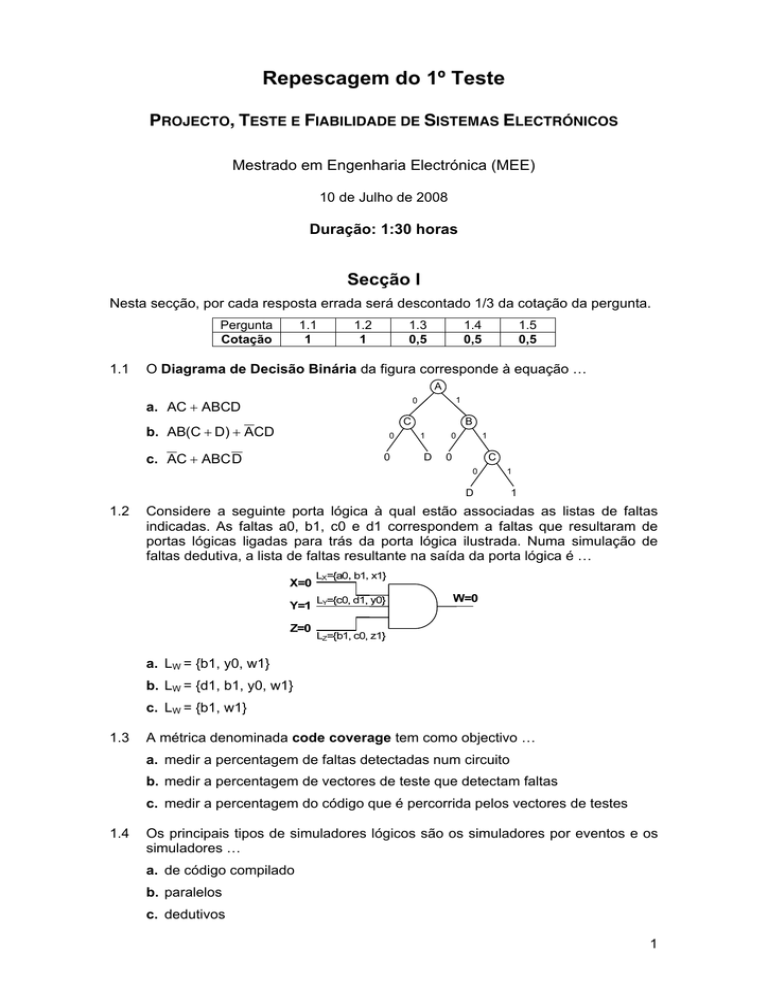

O Diagrama de Decisão Binária da figura corresponde à equação …

A

a. AC + ABCD

b. AB(C + D) + ACD

c. AC + ABC D

1

0

B

C

0

0

1

D

1

0

C

0

0

1

D

1.2

1

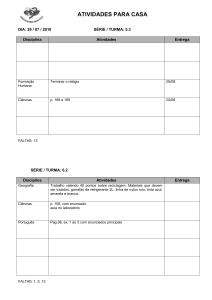

Considere a seguinte porta lógica à qual estão associadas as listas de faltas

indicadas. As faltas a0, b1, c0 e d1 correspondem a faltas que resultaram de

portas lógicas ligadas para trás da porta lógica ilustrada. Numa simulação de

faltas dedutiva, a lista de faltas resultante na saída da porta lógica é …

a. LW = {b1, y0, w1}

b. LW = {d1, b1, y0, w1}

c. LW = {b1, w1}

1.3

A métrica denominada code coverage tem como objectivo …

a. medir a percentagem de faltas detectadas num circuito

b. medir a percentagem de vectores de teste que detectam faltas

c. medir a percentagem do código que é percorrida pelos vectores de testes

1.4

Os principais tipos de simuladores lógicos são os simuladores por eventos e os

simuladores …

a. de código compilado

b. paralelos

c. dedutivos

1

1.5

Num circuito com redundância …

a. a testabilidade diminui

b. a cobertura de faltas aumenta

c. há menos faltas

Secção II

Problema

Cotação

1

4

2

3

3 a)

2

3 b)

1,5

4

3

5

3

Problema 1

Simule o circuito da Figura 1 (a) para a sequência de entrada apresentada na Figura

1 (b). Considere que no instante inicial (t=0), todos os nós do circuito têm o valor ´U´.

Simule o circuito durante 10 unidades de tempo. Assuma que as portas lógicas

apresentam atraso unitário (D=1). Apresente as formas de onda para todos os nós do

circuito.

A

H

K

B

C

F

J

I

L

D

E

G

Q

D

CK

Clock

Figura 1 (a)

Figura 1 (b)

Problema 2

Realize o nivelamento da parte combinatória do circuito da Figura 1 (a), indicando o

nível atribuído a cada porta lógica.

2

Problema 3

Considere o circuito da Figura 2. Para cada uma das alíneas seguintes, indique os

vectores de teste que distinguem entre os pares de faltas indicados.

a)

F-SA0 e E-SA0

b)

F-SA0 e E-SA1

Figura 2

Problema 4

Após aplicação da Análise Nodal Modificada, obteve-se o sistema de equações

representado na Figura 3. Desenhe o circuito correspondente a este sistema de

equações.

⎡G1 + G3

⎢

⎢ − G3

⎢

0

⎢

0

⎣

− G3

0

G3

0

0

G2

1

0

0⎤ ⎡ V1 ⎤ ⎡ 0 ⎤

⎥ ⎢

⎥

⎥⎢

1⎥ ⎢ V2 ⎥ ⎢ IS1 ⎥

=

0⎥ ⎢ V3 ⎥ ⎢− IS1⎥

⎥ ⎢

⎥

⎥⎢

0⎦ ⎣IVS1⎦ ⎣ VS1 ⎦

Figura 3

Problema 5

Considere o circuito da Figura 4, em que os valores das entradas primárias são

ABCDE = 11001. Recorrendo ao algoritmo do Caminho Crítico, indique as faltas que

são detectadas por este vector de teste.

A

H

F1

B

C

K

F

I1

F2

I

D1

D

E

J

I2

D2

L

G

Figura 4

3