ESPECIFICAÇÃO DO CIRCUITO RESSONANTE

UTILIZADO NA COMUTAÇÃO FORÇADA DE TIRISTORES

Kazuo Nakashima

Valberto F. da Silva

Luiz E.B. da Silva

Escola Federal de Engenharia de Itajubá

Departamento de Eletrônica

Resumo: Este artigo apresenta um roteiro

simples e rápido para especificação do circuito ressonante utilizado na comutação

forçada de tiristores considerando:

•

•

•

•

Tempo de recuperação reversa do tiristor tQ.

Tensão máxima no capacitor VCpmax

Todo processo de comutação ocorre

num intervalo muito pequeno (50 a 200µs)

quando comparado com o intervalo de

chaveamento dos tiristores (2 a 10ms).

Podemos considerar a corrente na carga

(Ia) praticamente constante neste intervalo

de comutação.

Q1

Corrente máxima de comutação IQmax

Variação na tensão de alimentação.

D22

D1

I - INTRODUÇÃO

O procedimento de cálculo apresentado

neste artigo considera a variação na tensão de alimentação além de predeterminar

a tensão máxima no capacitor, VCpmax, e

a corrente máxima de comutação, ICpmax.

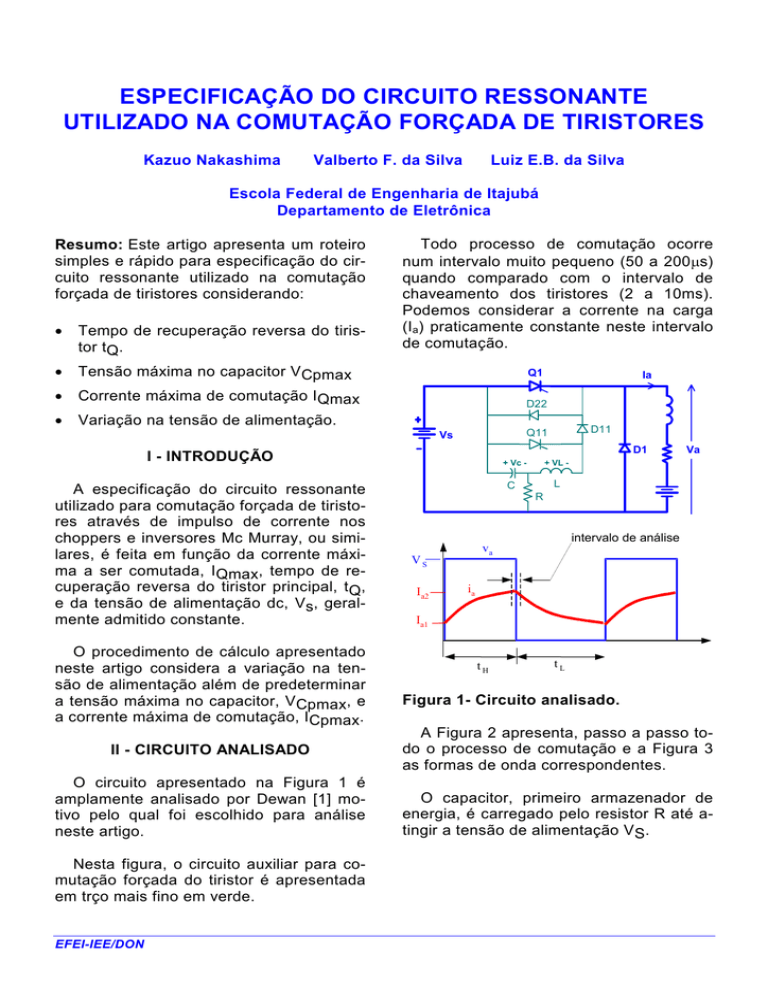

II - CIRCUITO ANALISADO

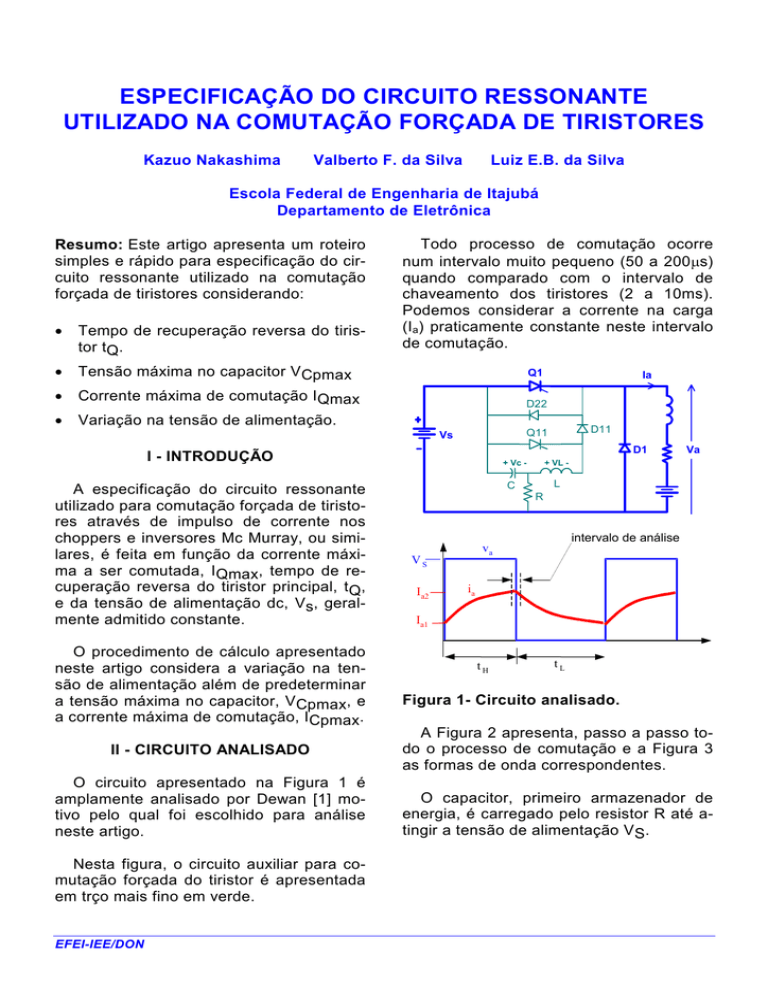

O circuito apresentado na Figura 1 é

amplamente analisado por Dewan [1] motivo pelo qual foi escolhido para análise

neste artigo.

Nesta figura, o circuito auxiliar para comutação forçada do tiristor é apresentada

em trço mais fino em verde.

EFEI-IEE/DON

D11

Q11

Vs

A especificação do circuito ressonante

utilizado para comutação forçada de tiristores através de impulso de corrente nos

choppers e inversores Mc Murray, ou similares, é feita em função da corrente máxima a ser comutada, IQmax, tempo de recuperação reversa do tiristor principal, tQ,

e da tensão de alimentação dc, Vs, geralmente admitido constante.

Ia

+ Vc -

Va

+ VL -

L

C

R

VS

Ia2

intervalo de análise

va

ia

Ia1

tH

tL

Figura 1- Circuito analisado.

A Figura 2 apresenta, passo a passo todo o processo de comutação e a Figura 3

as formas de onda correspondentes.

O capacitor, primeiro armazenador de

energia, é carregado pelo resistor R até atingir a tensão de alimentação VS.

especificação do circuito ressonante utilizado na comutação forçada de tiristores

Intervalo I - O tiristor é disparado fechando-se um curto circuito no circuito

ressonante LC série. A energia armazenada no capacitor é transferida para o indutor e em seguida devolvida ao capacitor. O

objetivo deste processo é inverter a polaridade da tensão no capacitor e prepará-lo

efetivamente para comutação do tiristor

principal.

Intervalo II - Tem início a comutação

efetiva do tiristor. O circuito ressonante

desvia a corrente do tiristor principal até

zerar. O circuito ressonante é curtocircuitado via D11 e Q1. Observe ainda

que o circuito ressonante injeta uma corrente no sentido inverso de condução do

tiristor principal Q1.

Intervalo III - Como o circuito ressonante deve ser projetado para produzir pico de

corrente maior que a corrente a ser comutada,ICp>IQmáximo, o excesso de corrente circula pelo diodo D22. Este intervalo é

de suma importância pois é o intervalo no

qual o tiristor principal recupera o estado

de bloqueio. O circuito ressonante é curtocircuitado via D11 e D22.

Intervalo IV - Neste intervalo a corrente

que circula no circuito ressonante é praticamente constante. É o intervalo para que

o capacitor atinja a tensão VS.

Intervalo V - No instante que a tensão

no capacitor atinge o valor VS, a tensão na

carga atinge zero e o diodo freewheeling

D1 inicia a condução. O circuito ressonante é curto-circuitado via VS e D1 continuando o comportamento senoidal. A diminuição da corrente no circuito ressonante

provoca aumento da corrente no diodo

free-wheeling D1.

Intervalo VI - A corrente de carga circula "livremente" pelo diodo D1. O capacitor

se descarrega até atingir o valor VS via resistor R.

EFEI-IEE/DON

2

A Figura 4 apresenta com mais detalhes

a corrente de comutação e um formulário

completo.

III - PROCEDIMENTO DE CÁLCULO

A ideia básica deste procedimento de

cálculo consiste em transferir todos os resultados de análise apresentado no formulário da Figura 4 para tensão de alimentação nominal (N).

1. Determinar a faixa de XN (nominal)

submetido as três condições.

2. Escolher, quando possível, XN. Máximo

XN para menor tensão de pico no capacitor ou mínimo XN para menor corrente

de comutação (menor corrente de pico

no tiristor auxiliar Q11. Se não for possível, devemos abandonar um dos critérios de projeto.

3. Escolhido XN, calcular C e L do circuito

ressonante para pior condição, ou seja,

VSmin (mínimo). Menor tensão de alimentação implica em menor tempo de

polarização reversa do tiristor a ser comutado. Observe a função:

V

G ( X N . Smin ) = G ( X min )

VSN

4. Para conferir os resultados de VCpmax

e ICpmax, utilizar o valor máximo de

VS, Vsmax.

5. Para conferir o tempo mínimo de bloqueio reverso do tiristor principal, intervalo tIIImin, utilizar o valor mínimo de

VS, Vsmin. Este é o principal item a ser

observado, uma vez que é o responsavel pela garantia do sucesso do bloqueio do tiristor principal.

especificação do circuito ressonante utilizado na comutação forçada de tiristores

Q1

Ia

D22

D11

Q11

Vs

D1

Va

+ VL -

+ Vc -

L

C

R

intervalo I

Q1

Ia

D22

D11

Q11

Vs

D1

+ Vc -

Va

+ VL -

L

C

R

intervalo II

Q1

Ia

D22

D11

Q11

Vs

D1

+ Vc -

Va

+ VL -

L

C

R

intervalo III

Q1

Ia

D22

D11

Q11

Vs

D1

+ Vc -

Va

+ VL -

L

C

R

intervalo IV

Q1

Ia

D22

D11

Q11

Vs

D1

+ Vc -

Va

+ VL -

L

C

intervalo V

R

Q1

Ia

D22

D11

Q11

Vs

D1

+ Vc -

Va

+ VL -

L

C

R

Figura 2- Paso a passo da comutação.

EFEI-IEE/DON

Figura 3- Formas de onda.

3

especificação do circuito ressonante utilizado na comutação forçada de tiristores

ICP

IQ

I

II

d

i(t ) [ V]

dt

1

vC ( t ) = ∫ i(t ) dt [ V]

C

1

E L = LI 2 [J ]

2

1

E C = C V 2 [J ]

2

C

. VS [A ]

I Cp =

L

vL ( t ) = L

X=

I Cp

IQ

(1)

(2)

(3)

(6)

(5)

IV

t II = LC .sen −1 (1 / X ) [S]

[

t III = LC π − 2 .sen −1 (1 / X )

[

(

]

(8)

)]

[S]

t IV = LC 1 − cos sen −1 (1 / X )

π

2

EFEI-IEE/DON

(10)

(11)

G ( X) = π − 2 . sen − 1 (1 / X) [ rad ]

VC = VS (1 + (1 / X ))

(9)

[V ]

(12)

(13)

(14)

VSN

.X min

VS min

VSN

XN >

VCmax − VSmax

I Cpmax

V

X N < SN .

VSmax I Qmax

L=

(7)

VI

XN >

(6)

t I = LC . π [S]

V

XN

V

= SN

Xi

VSi

C=

=1,4 ... 3,0

t V = LC

III

4

X N . I Qmax . t Q

V

VSN . G( X N . Smin )

VSN

VSN . t Q

V

X N . I Qmax . G( X N . Smin )

VSN

(15)

(16)

(17)

[F]

(18)

[H] (19)

C

[A]

VSmax

L

I Qmax

. VSmax =

VCpmax = 1 +

I

Cpmax

I Cpmax =

= VSmax +

[

(20)

(21)

L

I Qmax

C

]

t II Im in = LC π − 2 sen −1 (1 / X min )

(22)

especificação do circuito ressonante utilizado na comutação forçada de tiristores

Conferindo: IQmax=200 [A]

IV - EXEMPLO

Especificar o circuito ressonante para

IQmax=200[A], tQ=30[µS], Vs=120[V] ±

20%, tensão máxima no capacitor 240[V] e

corrente máxima de comutação = 600[A]

pico.

VS = 96...144 [V]

XN ⟩

120

VSN

.1,4 = 1,75

X min =

96

VSmin

VSN

120

=

= 1,25

XN ⟩

VCmax − VSmax 240 − 144

XN ⟨

VSN I Cpmax 120 600

.

=

.

= 2,5

VSmax I Qmax 144 200

1,75 ≤ X N ≤ 2,5

Para menor

XN=1,75

corrente

de

comutação,

V

G ( X min ) = G ( X N . Smin )

VSN

96

= G (1,75.

) = G(1,4)

120

G (1,4) = π − 2 sen −1 (1 / 1,4) = 1,55038[ rad ]

C=

X N . I Qmax

. tQ

VSN . G ( X min )

1,75. 200

=

.30µ = 56,4µF

120 . G (1,4)

VSN

L=

.tQ

X N . I Qmax . G ( X min )

=

120

. 30µ = 6,6µH

1,75. 200 .1,55038

EFEI-IEE/DON

5

VS

tQ [µs]

ICP [A]

VCP [V]

X

96

120

144

29,91 *

37,14

41,46

280

350

420 *

164,5

188,5

212,5 *

1,4

1,75

2,1

Observamos que o menor tempo de tQ

ocorre para menor tensão de alimentação

e é igual ao menor valor especificado.

O maior valor de corrente de comutação

e da tensão no capacitor ocorre para maior

tensão de alimentação e são menores que

o máximos especificados.

V - McMURRAY DE DOIS QUADRANTES

O chopper de dois quadrantes (Q I-II) e

o inversor Mc Murray original apresentam

comportamento semelhante porem o processo de comutação inicia diretamente no

intervalo II.

D11

Q11

Q1

D2

La

Ra

Vs

D22

Q22

Q2

D1

Ea

VII- COMENTÁRIOS FINAIS

Este procedimento de cálculo pode ser

utilizado para uma primeira estimativa dos

componebtes do circuito auxiliar de comutação uma vez que não considera perdas

nos diodos e tiristores e não considera o

snubber e o indutor utilizado para limitação

do di/dt.

especificação do circuito ressonante utilizado na comutação forçada de tiristores

VIII- REFERÊNCIAS

[1]

S.B.Dewan and A.Straughen,- Power

Semiconductor Circuits. Wiley, Toronto,

1975.

[2]

W.McMurray,- SCR Inverter Commutated by an Auxiliary Impulse. IEEE

Trans. On Communication and Electronics, Vol. 83, No 75, pp. 824-829, November 1964.

Artigo apresentado no V SEMINÁRIO DE PESQUISA DA EFEI

EFEI-IEE/DON

6