Organização de Computadores

Antônio Borges / Gabriel P. Silva

4. Modelo de Programação do DLX

“Quero que o matemático Beremiz Samir nos conte uma

lenda, ou uma simples fábula, na qual apareça uma divisão

de 3 por 3 indicada, mas não efetuada, e outra de 3 por 2,

indicada e efetuada sem deixar resto.”

Malba Tahan

O Homem que Calculava

4.1. Introdução

O modelo de programação que estaremos estudando é baseado no processador didático DLX,

definido por Henessy e Patterson no seu livro “Computer Architecture: A Quantitative Approach”

(Morgan Kaufmann, 1991). Usaremos um simulador com essa arquitetura para facilitar a compreensão do funcionamento de um processador.

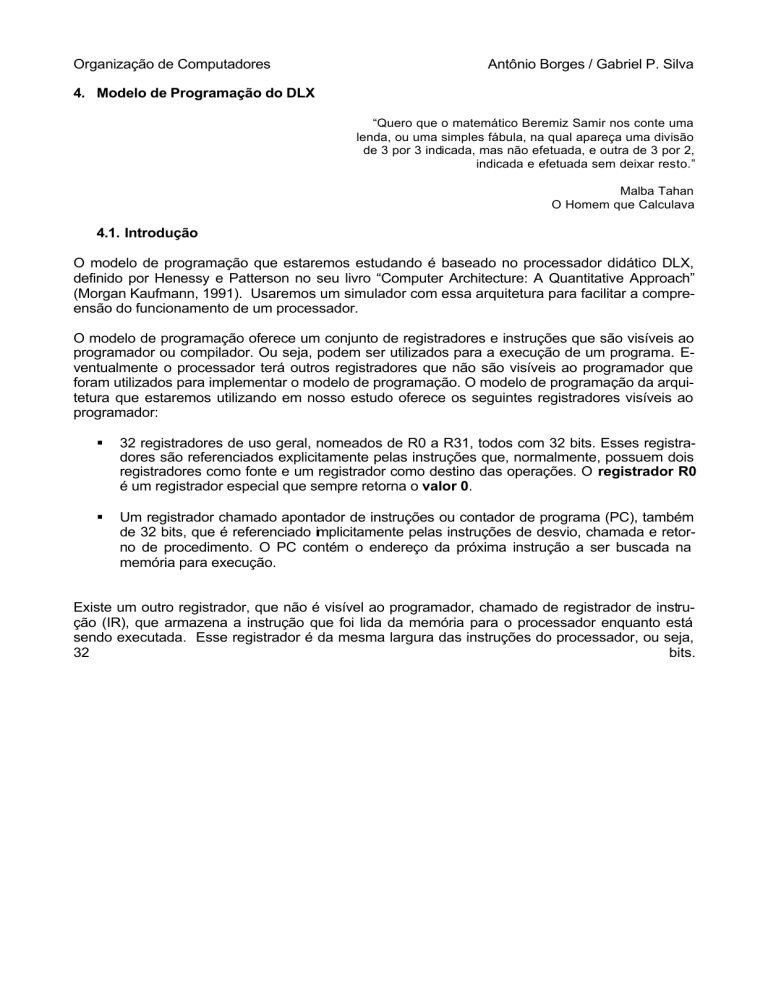

O modelo de programação oferece um conjunto de registradores e instruções que são visíveis ao

programador ou compilador. Ou seja, podem ser utilizados para a execução de um programa. Eventualmente o processador terá outros registradores que não são visíveis ao programador que

foram utilizados para implementar o modelo de programação. O modelo de programação da arquitetura que estaremos utilizando em nosso estudo oferece os seguintes registradores visíveis ao

programador:

§

32 registradores de uso geral, nomeados de R0 a R31, todos com 32 bits. Esses registradores são referenciados explicitamente pelas instruções que, normalmente, possuem dois

registradores como fonte e um registrador como destino das operações. O registrador R0

é um registrador especial que sempre retorna o valor 0.

§

Um registrador chamado apontador de instruções ou contador de programa (PC), também

de 32 bits, que é referenciado implicitamente pelas instruções de desvio, chamada e retorno de procedimento. O PC contém o endereço da próxima instrução a ser buscada na

memória para execução.

Existe um outro registrador, que não é visível ao programador, chamado de registrador de instrução (IR), que armazena a instrução que foi lida da memória para o processador enquanto está

sendo executada. Esse registrador é da mesma largura das instruções do processador, ou seja,

32

bits.

Organização de Computadores

Antônio Borges / Gabriel P. Silva

BANCO DE REGISTRADORES

“0”

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

R17

R18

R19

R20

R21

R22

R23

R24

R25

R26

R27

R28

R29

R30

R31

SP

FP

RA

PC

Figura 6 – Modelo de Programação

Organização de Computadores

Antônio Borges / Gabriel P. Silva

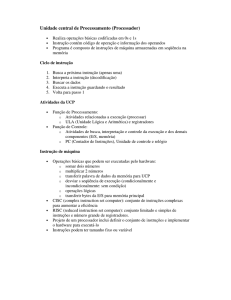

Durante o seu funcionamento o processador executa permanentemente o seguinte ciclo de operações, denominado de ciclo de execução das instruções:

1. Busca a próxima instrução que está localizada na memória para o registrador de instrução;

2. Atualiza o apontador de instruções (PC) para que ele aponte para a próxima instrução a

ser lida da memória e executada.

3. Determina o tipo de instrução e o número de operandos;

4. Busca os operandos, se houver, para os registradores no processador;

5. Executa a instrução;

6. Armazena os resultados;

7. Volta ao passo 1 para executar a próxima instrução.

Este ciclo só será interrompido quando o processador receber sinais elétricos especiais para, por

exemplo, reiniciar o seu funcionamento, parar totalmente a atividade, entrar em modo de economia de energia ou interromper o seu funcionamento para atender a um pedido da unidade de entrada e saída.

A seguir mostramos o diagrama em blocos de uma possível implementação do DLX. A memória

principal, por motivos didáticos, foi dividida em memória de instruções e memória de dados. No

diagrama, os blocos com o nome MUX servem para selecionar entre duas fontes de dados, de

acordo com o comando da unidade de controle. O bloco ADD é um somador binário e o bloco ALU

é a unidade aritmética e lógica.

Figura 7 – Diagrama em Blocos do DLX

Como já dissemos, em nosso modelo todas as instruções possuem 32 bits e nelas estão codificadas a operação que a UAL deve executar e todas as informações adicionais, tais como os registradores fonte e destino das operações aritméticas.

Organização de Computadores

Antônio Borges / Gabriel P. Silva

Existem diversos tipos de instruções que podem ser executadas pelo processador DLX, dentre

eles destacamos:

§

§

§

§

Operações aritméticas (soma, subtração, divisão, multiplicação, etc).

Operações lógicas (complemento, deslocamento, etc.).

Operações de transferência de dados (entre registradores, do registrador para a memória,

da memória para o registrador).

Operações de transferência de controle (desvio incondicional e condicional, chamada de

procedimento, etc).

Nas instruções do DLX podem estar definidos até 3 operandos, sendo dois de leitura e um de

escrita. Os operandos de leitura podem ser dois registradores, ou um registrador e um dado imediato, ou seja, uma constante embutida no próprio código da instrução. O operando de escrita ou

é um registrador ou uma posição de memória cujo endereço está definido em um registrador, eventualmente este valor é somado a uma constante definida na própria instrução.

4.2. Tipos de Instruções

Em uma dada arquitetura existem diversos tipos de instruções em uma linguagem de montagem que podem ser utilizadas pelo compilador para traduzir as sentenças em linguagens de alto

nível. As instruções de uma arquitetura genérica podem ser classificadas em:

§

§

§

§

Instruções Aritméticas e Lógicas (Inteiras)

Instruções de Transferência de Dados

Instruções de Transferência de Controle

Instruções de Ponto Flutuante

A seguir classificamos as principais instruções do DLX e mostramos alguns exemplos de suas

instruções em linguagem de montagem:

a) Instruções Aritméticas e Lógicas (Inteiras)

Essas instruções realizam operações aritméticas e lógicas entre dois registradores ou entre

um registrador e um operando imediato, guardando o resultado em um outro registrador.

nop

and

sll

addi

sub

srli

sge

slti

R1, R2, R3

R3, R4, R5

R15, R0, #25

R6, R7, R8

R9, R10, #5

R1, R4, R6

R5, R8, #3

; “no operation”

; R! = R2 and R3

; R3 = R4 << R5 (desloca R4 de R5 bits p/ esquerda)

; R15 = 25

; R6 = R7 – R8

; R9 = R10 >> 5 (desloca R10 de 5 bits p/ direita)

; Se R4 >= R6 então R1 = 1 senão R5 = 0

; Se R8 < 3 então R5 = 1 senão R5 = 0

; A instrução de comparação (sCC) pode ser:

; seq ( = ), sne ( != ), slt ( < ), sgt ( > ),

; sle ( <= ), sge ( >= )

b) Transferência de dados

Essas instruções realizam operações de transferência do conteúdo de um registrador para a

memória e vice-versa. A quantidade de bytes transferidos é definida pelo tipo de instrução, as

instruções lb e sb transferem apenas um byte, as instruções lw e sw transferem 4 bytes de

cada vez.

Organização de Computadores

lw

lb

sw

sb

Antônio Borges / Gabriel P. Silva

R5, (endereço)

R9, (endereço)

(endereço), R6

(endereço), R8

;

;

;

;

R5 = memória[endereço] (4 bytes)

R9 = memória[endereço] (1 byte)

memória[endereço] = R6 (4 bytes)

memória[endereço] = R8 (byte)

O endereço de memória a ser lido ou escrito é obtido pela soma do conteúdo de um registrador com um dado imediato:

lw

lb

sw

sb

lw

R5, 0(R16)

R5, 150(R0)

200(R0), R6

8(R16), R8

R8, A(R0)

; R5 = memória [R16+0]

; R9 = memória [150]

; memória[200] = R6

; memória[R16+8] = R8

; R8 = memória [A] (A é um rótulo que define

; um endereço de memória.)

c) Transferência de controle

As instruções desse tipo alteram o valor do apontador de instruções (PC), ou seja, a próxima

instrução a ser buscada vai estar no endereço especificado na instrução de desvio e não, com

seria esperado, a instrução seguinte.

§

Desvios Incondicionais

Sempre alteram o valor do apontador de instruções.

j 1000

§

; PC = 1000

Desvios Condicionais

Só alteram o valor do apontador de instruções se a condição especificada for verdadeira.

bnez R1, 2000

beqz R8, 3000

§

; se R1 != 0 então PC = 2000, senão PC = PC+4

; se R8 == 0 então PC = 3000, senão PC = PC+4

Chamada e Retorno de Procedimento

A chamada de procedimento é um tipo especial de instrução de desvio incondicional que salva o endereço da instrução seguinte em um registrador antes do desvio

ser executado. O retorno de procedimento pega o valor salvo no registrador e atribui ao PC. Veremos esta instrução com mais detalhes na seção 5.2.3.

jal 5000

jr

§

R31

; R31 = PC + 4 e PC = 5000

(chamada de procedimento)

; PC = R31

(retorno de procedimento)

Chamadas ao Sistema

São instruções especiais que desviam para rotinas dentro do núcleo do sistema operacional, mudando antes o estado do processador de normal para privilegiado.

Esta instrução será estudada com mais detalhes na seção 5.2.5.

Organização de Computadores

trap #imm

trap #0

trap #5

Antônio Borges / Gabriel P. Silva

; desvia para o sistema

; operacional para executar

; o serviço especificado por #imm

d) Ponto Flutuante

São instruções que manipulam valores reais, normalmente no formato IEEE 754, em precisão

simples (32 bits) ou precisão dupla (64 bits). Existe um banco de registradores adicional para

armazenar estes tipos de operando. Não estaremos abordando em nosso estudo as instruções de ponto flutuante, muito embora façam parte da definição do DLX.