INSTITUTO SUPERIOR TÉCNICO

Departamento de Engenharia Electrotécnica e de Computadores (DEEC)

Área Científica de Electrónica

ELECTRÓNICA GERAL

2ºTrabalho de Laboratório

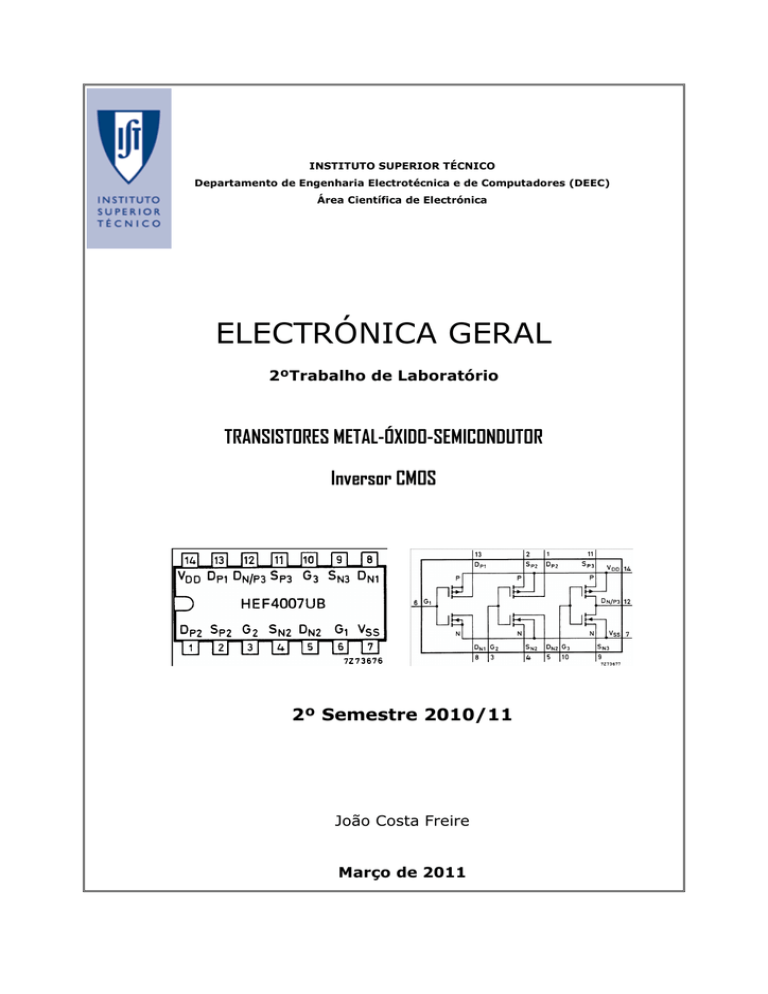

TRANSISTORES METAL-ÓXIDO-SEMICONDUTOR

Inversor CMOS

2º Semestre 2010/11

João Costa Freire

Março de 2011

Laboratório de Electrónica Geral

TRANSISTORES METAL-ÓXIDO-SEMICONDUTOR (HEF 4007)

Inversor CMOS

I. Objectivos

Estudar as características principais que definem o funcionamento de um inversor CMOS, que

é o elemento básico dos circuitos CMOS, nomeadamente os digitais, usando as relações

teóricas clássicas i(v) para um transístor MOS. Com o recurso a ferramentas de CAD são

verificadas as condições de funcionamento dum inversor excitado por um sinal forte

(varrimento em DC), por um sinal sinusoidal em regime linear (AC) e por uma onda quadrada

(comutação). Para o efeito usam-se modelos dos transístores para o simulador PSPICE,

disponíveis. Finalmente, são verificadas experimentalmente algumas das características do

amplificador e verificada a validade de alguns parâmetros dos modelos disponíveis. Note-se

que os parâmetros dos modelos correspondem a valores típicos (médios). No entanto, há uma

elevada dispersão de valores devido aos processos de fabrico dos circuitos.

II. Estudo analítico

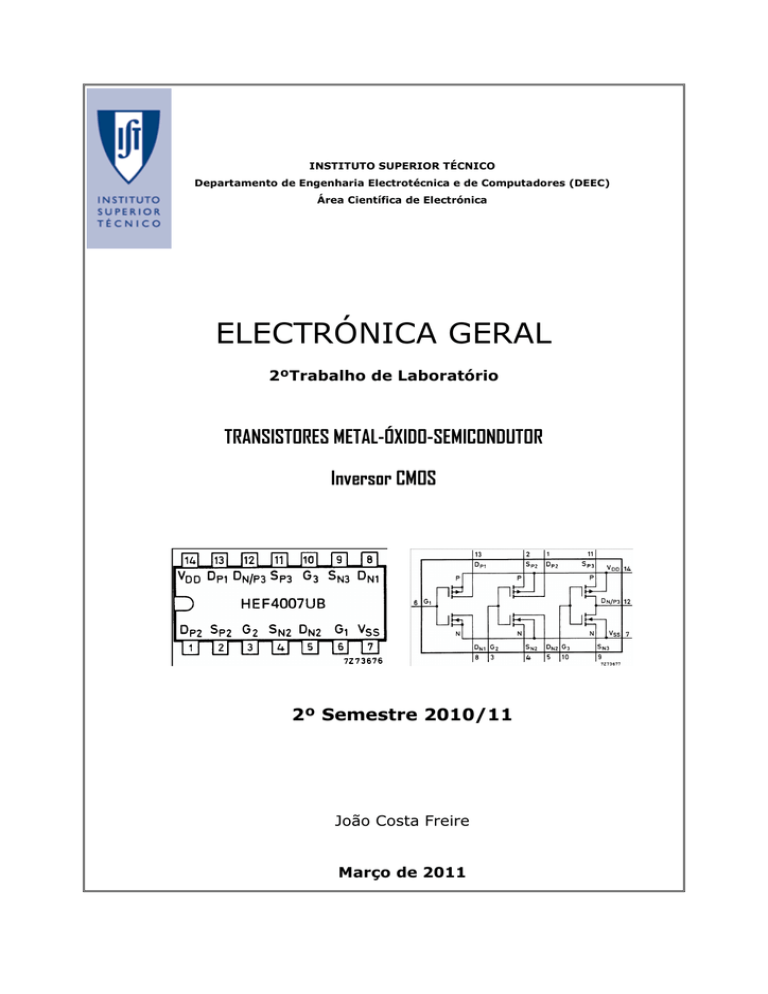

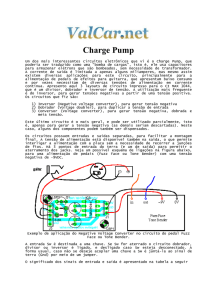

Considere o circuito dum inversor CMOS da figura II.1. Este é constituído por dois

transístores complementares de reforço NMOS e PMOS com terminais de fonte ligados aos

respectivos terminais de substrato, não havendo assim efeito de corpo. Para construir este

circuito utilizar-se-á um dos pares de transístores complementares existentes no circuito

integrado (CI) monolítico HEF4007 (características de catálogo no anexo 1). Usar-se-á o par

que tem as portas ligadas ao terminal 6 e ambas as fontes já ligadas aos respectivos substratos.

Note-se, figura 1 do anexo, que este circuito integrado inclui 3 pares de transístores MOS

complementares: nos 3 pares de transístores as portas dos dois transístores estão ligadas

internamente (terminais 3, 6 e 10), e os substratos dos transístores N ou P estão todos

interligados (terminal 7 ou 14); um dos pares (portas ligadas ao terminal 6) tem ambas as

fontes ligadas ao respectivo substrato (vSB=0), por isso será o utilizado; outro dos pares

(portas no terminal 10) tem os drenos interligados (terminal 12) estando pois montados como

um inversor CMOS; e o terceiro par (portas no terminal 3) tem as fontes e os drenos

independentes (terminais 1, 2, 4 e 5), para poderem ser utilizadas em portas lógicas não

elementares.

-1-

VDD

T2

vI

vO

T1

VSS

Figura II.1 – Circuito inversor CMOS

1. Trace a característica de transferência vO(vI) do circuito da figura II.1, recorrendo aos

modelos simplificados de cada um dos transístores obtidos com base nos parâmetros da

Tabela II.1, lambda=0, k=(KP/2)(W/L) e Vt=VTO, e para as tensões de alimentação

dadas na Tabela II.2. Determine os pontos desta característica onde tem lugar a

alteração dos modos de operação (corte, saturação e tríodo) de cada um dos transístores.

Compare a curva obtida com as fornecidas pelo fabricante (anexo I figuras 3, 4 ou 5).

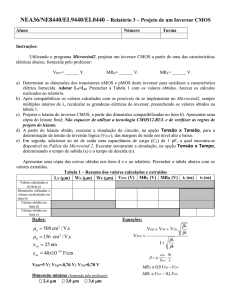

Tabela II.1 – Especificações gerais dos modelos dos transístores do circuito integrado HEF 4007

Modelo dos transístores MOS a utilizar nos cálculos e simulação

NMOS

PMOS

.MODEL N4007 NMOS (TOX=70N

KP=73u

VTO=*V

GAMMA=2.0

CBD=0.2p CBS=0.2p MJ=0.75 L=5u

W=100u LAMBDA=20m)

.MODEL P4007 PMOS (TOX=70N

KP=16u

VTO=*V

GAMMA=1.0

CBD=0.2p CBS=0.2p MJ=0.75 L=5u

W=300u LAMBDA=20m)

* Ver tabela II.2

Tabela II.2 – Especificações dependentes da turma e grupo

VTO dos transístores circuito integrado HEF 4007 e tensões de alimentação

Turma

VTn (V) -VTp (V) Grupo VDD (V) VSS (V)

2ªf 15h

1,6

1,8

1

15

0

2ªf 17h

1,8

1,6

2

13

0

3ªf 12h

2,0

2,0

3

11

0

3ªf 14h30

2,2

2,0

4

9

0

5

7

0

6

5

0

7

10

0

2. Considerando o valor de lambda dado na Tabela II.1, e que permite calcular o parâmetro

ro do modelo dinâmico dos TECMOS, obtenha uma estimativa do ganho a meio da zona

onde o inversor pode operar como amplificador, a partir de uma análise incremental.

-2-

Compare este valor com o obtido a partir da curva típica do ganho em função da tensão

de alimentação VDD (supondo VSS=0) – figura 6 do anexo.

3. A partir da característica vO(vI) obtida no ponto 1, obtenha graficamente uma estimativa

das margens de ruído do inversor, quando funciona como circuito lógico básico, bem

como das tensões limites destas margens de ruído. Considere o limite inferior da tensão

vI que leva a saída vO ao nível lógico 0 e o limite superior de vI que mantém a saída vO

no nível 1 definidos pelos pontos onde o ganho de tensão é igual a 1, isto é, os pontos da

característica de transferência de tensão vO(vI) que limitam a zona onde o inversor tem

ganho maior do que 1 (opera como amplificador). Esta é uma das formas de definir as

margens de ruído.

III Trabalho de simulação

1. DC sweep - Utilizando os modelos disponíveis para os transístores do circuito integrado

HEF 3046 para o Pspice (tabelas II.1 e II.2), obtenha por simulação a característica

vO(vI) do circuito da figura II.1, fazendo um varrimento da tensão vI de 0 a VDD (DC

sweep com gerador vI do tipo VDC).

2. DC sweep - Utilizando o programa PROBE do PSPICE, obtenha também o gráfico da

derivada dvO/dvI com o comando Add Traces e recorrendo à função D( ) cujo

argumento é a tensão do nó correspondente a vO. Obtenha o valor de vI para o qual o

módulo do ganho é máximo (VIMAX). Note que, como a curva tem uma derivada com vI

muito elevada na zona central pelo que deve fazer um zoom na zona de ganho máximo.

3. AC sweep - Obtenha também por simulação, mas agora em regime AC (AC sweep com

gerador vI do tipo VAC), o ganho em sinais fracos para o ponto de funcionamento de

ganho máximo obtido na alínea anterior (VIMAX) e que corresponde mais ou menos a

meio da zona de transição (zona de funcionamento do inversor como amplificador).

Para o efeito aplique na entrada vI um gerador com duas componentes, uma alternada

sinusoidal (AC) e outra contínua (DC: tensão de desvio – offset). Faça um varrimento na

frequência para detectar as frequências de corte do ganho de tensão a -3dB inferior e

superior do inversor. Considere que o inversor está terminado na saída por uma

capacidade de 50pF em paralelo com uma resistência de 1MΩ, valor correspondente à

impedância do cabo coaxial de ligação ao osciloscópio.

-3-

Compare o valor do ganho máximo obtido com o calculado na alínea anterior. Comente

as diferenças encontradas em relação ao amplificador com um transístor bipolar

estudado no 1º trabalho de laboratório.

4. Transient - Aplicando à entrada do circuito da figura I.1 uma onda trapezoidal de

amplitude máxima VDD e mínima VSS, com tempos de subida e descida muito mais

rápidos que os tempos de transição entre estados previstos para o inversor CMOS com

uma carga capacitiva de 50pF (condições da tabela da página 3 do anexo e condições

de medida no laboratório, como já se referiu atrás) e com uma duração de 0,5µs em

cada estado (cerca de 1µs de período – frequência de repetição de 1MHz), obtenha por

simulação os tempos de comutação de subida (rise time) e de descida (fall time), bem

como o tempo de atraso de propagação (delay time) do inversor (Transient com

gerador vI do tipo VPULSE).

Compare com os valores fornecidos pelo fabricante (anexo 1 página 3).

IV. Trabalho experimental

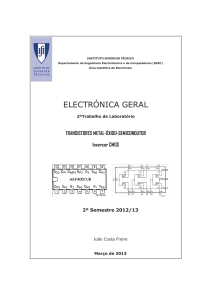

Efectue a montagem do inversor CMOS da figura I.1 usando a base de montagem TEE 03

representada na figura IV.1 que contem um circuito integrado HEF4007 e duas resistências

R1= 22kΩ e R2=100kΩ.

Figura IV.1 – Base de montagem TEE 03

-4-

ATENÇÃO: Antes de ligar a fonte de alimentação DC, ligue o terminal VDD

(terminal 14 do CI HEF 4007) ao terminal positivo da fonte de tensão VDD e a

referência (terminal 7 do CI HEF 4007) ao terminal negativo. Como indicado na nota da

página 8 do anexo, se não se efectuarem previamente estas ligações, pode-se deteriorar

definitivamente o circuito integrado (CI).

Ligue o gerador de sinais e as duas entradas do osciloscópio à base de montagem da

Figura IV.1 de acordo com o esquema da Figura IV.2.

VDD

vI

+

-

v0

gerador

VSS

CH1

OSC.

CH2

Figura IV.2 – Montagem para teste dum inversor CMOS

1. Na primeira parte das medidas o gerador vI é um gerador de funções. Ajuste o gerador de

funções para um sinal de saída sinusoidal de 100Hz. Como tem uma alimentação DC

assimétrica, VSS=0, ajuste a tensão de desvio (offset) do gerador para VDD/2 e a amplitude

máxima deve ser igual a VDD/2, isto é, vI varia de 0 a VDD. Não ultrapasse estes valores.

Deve ligar os aparelhos do laboratório ao circuito inversor sempre por esta ordem: 1º

osciloscópio; 2º fonte de alimentação DC; e 3º gerador de funções. A fonte de

alimentação e o gerador de funções devem ser ajustados aos valores de amplitude

desejados só depois de serem ligados ao circuito inversor. Portanto ao ligar devem ter

ambos um sinal de amplitude 0 (zero). Deve fazer os ajustes de valores lentamente, sempre

a visualizá-los no osciloscópio, para NÃO ultrapassar os valores desejados. Cuidado com

as massas dos cabos coaxiais: têm de estar todas ligadas ao mesmo ponto do circuito

para evitar curto-circuitos indesejáveis. Estes cuidados devem-se a fragilidade das portas

dos TECMOS que é um condensador. Valores excessivos de tensão na portas ou suas

variações bruscas (provocam picos de corrente - iC=CdvC/dt) podem destruir a porta. A

camada de óxido, que é o dieléctrico do condensador, pode degradar-se permanentemente.

Esta camada é muito fina e por isso não suporta só tensões baixas. Cargas eléctricas

-5-

estáticas Q ao manusearmos TECMOS também os podem destruir (v = Q/C: como C é

muito pequeno podem-se facilmente atingir tensões V elevadas). Os transístores têm

normalmente circuitos de protecção para evitar este problema. Normalmente usa-se díodos

para limitar a tensão.

Visualize as tensões de entrada vI e de saída vO no osciloscópio. Visualize a característica

vO(vI) usando o osciloscópio no modo XY ou equivalente: a entrada relativa a vI é aplicada

na deflexão horizontal (eixo dos xx); e a entrada relativa a vO na deflexão vertical (eixo dos

yy). Faça um esboço desta característica (pode usar uma das quadrículas fornecidas no

anexo 2) ou fotografe-a e coloque a figura no seu relatório. Não se esqueça de colocar as

escalas em todos os gráficos que efectuar.

2. Na segunda parte o gerador vI é um gerador de impulsos. Ligue o gerador de impulsos

directamente ao osciloscópio e ajuste-o para impulsos de 100ns (pulse spacing e pulse

width) na forma onda quadrada (square). Ajustar o período do sinal para 1µs. Após ligar o

gerador ao inversor CMOS ajuste o nível dos impulsos de forma a serem iguais às tensões

de alimentação DC (VDD e VSS). Visualize as tensões de entrada vI e de saída vO. Obtenha

os tempos de subida e descida bem como o tempo de atraso de propagação do inversor. Se

pretender, pode usar os cursores do osciloscópio. Faça um esboço do mostrador do

osciloscópio (pode usar uma das quadrículas fornecidas no anexo 2) ou fotografe-o e

coloque a figura no seu relatório. Não se esqueça de colocar as escalas em todos os

gráficos que efectuar.

3. Alínea facultativa - Para ter uma noção da dispersão de fabrico sugere-se que faça os

seguintes testes experimentais.

Ligue os transístores NMOS T1 e T2 da base de montagem às resistências R1 ou R2 de

acordo com as ligações da Figura IV.3.

VDD

VDD

R

T2

vO

vO

T1

R

Figura IV.3 – Montagem dos TECMOS para obter os parâmetros K e Vt.

Nestas condições ambos os transístores têm a tensão vGD = 0, o que garante que está a

operar na zona de saturação. Portanto, em primeira aproximação tem-se: iD = k (vGS-Vt)2.

-6-

Para os dois valores de resistências vai obter para cada transístor dois pares de valores (ID,

VGS) pelo que é possível obter uma estimativa dos parâmetros do modelo K e Vt.

Compare os valores obtidos experimentalmente com os que pode obter do catálogo. Notese que o catálogo não dá directamente os valores de Vt e de k. No entanto, uma estimativa

dos Vt é facilmente obtida dos gráficos das figuras 3 a 5 e 7. Quanto a k, lembrando que a

transcondutância em AC é dada por gm = diD/dvGS|PFR = 2(kID)½ (PFR – ponto de

funcionamento em repouso) tem-se k = (gm/2)2/ID. Da curva A (valores médios) da Fig.10

do catálogo tira-se o valor de gfs para um dado VDD e da curva da Fig.7 o correspondente ID

ou IDD como é denominado no catálogo. O significado de gfs é a transcondutância directa (f

de forward) com o inversor em curto-circuito em AC (s de short-circuit). O circuito de

teste usado para calcular gfs está representado na Fig. 9. Note-se que, ao colocar um

amperímetro na saída se está a introduzir um curto-circuito na saída em AC (condensador

de 100µF a bloquear a corrente DC). Deste modo, toda a corrente dos geradores

comandados que estão entre o dreno e as fontes dos modelos do NMOS e do PMOS,

2gmvgs (admitindo que têm o mesmo gm), vai para o amperímetro, não influenciando a

medida as resistências ro dos modelos dos dois transístores. Em conformidade, gm = gfs /2.

Note-se que em AC, regime dinâmico, os transístores estão em paralelo, logo as correntes

somam-se e os gm também. Assim pode-se escrever que k = (gfs/4)2 / IDD.

Compare também os valores experimentais obtidos para os k e Vt dos transístores com os

usados no modelo do PSpice. Note-se que a constante k = 2 KX W/L, com X = N ou P

consoante se trata do NMOS ou do PMOS. Quanto a Vt é denominado no modelo PSpice

por VTO.

V. Conclusões e críticas

1. Compare os resultados obtidos experimentalmente, parte IV, com os valores obtidos por

via teórica, analítica na parte II, e por simulação com o programa PSpice na parte III.

Comente, nomeadamente: a característica vO(vI), obtida em II.1, III.1 e IV.1, bem como os

valores das margens de ruído e do ganho delas obtidos; os tempos de comutação e atraso

na propagação, obtidos em III.4 e medidos em IV.2. Compare estas curvas e estes valores

numéricos com os dados típicos fornecidos pelo fabricante do circuito integrado (anexo 1).

2. O que aprendeu com este trabalho? Teça comentários à execução do trabalho e proponha

alterações que no seu entender o tornarão mais útil e aliciante.

-7-

Anexo 2

Quadrícula do osciloscópio

Tensão vin

Tensão vout

Escala

Escala

…………V/div

…………V/div

Base de tempo t: Escala …………s/div

Figura ilustrativa podendo usar uma semelhante editando-a.

Quadrícula do osciloscópio

Tensão vin

Modo XY

Escala

…………V/div

Tensão vout : Escala …………V/div

Figura ilustrativa podendo usar uma semelhante editando-a.

-8-

Anexo 3

Exemplo de gráficos do Probe a introduzir no relatório.

Atenção que os gráficos devem permitir uma leitura fácil pelo que devem ter dimensão

adequada. Para o caso da análise transitória apresentam-se 2 níveis de ampliação dos gráficos.

Sugere-se que num programa de processamento de imagem se inverta as cores para tornar a

leitura mais fácil e poupar tinta na impressão.

Análise DC

Análise AC

-9-

Análise Transitória

Ampliação

de cerca

de meio

período:

tempo de

subida de

50% cerca

de 1/6 de

divisão; e

uma

divisão é

50µs.

Ampliação

da zona de

subida da

tensão de

saída para

se notar o

atraso:

cerca de

1/5 de

divisão; e

uma

divisão é

5ns.

- 10 -