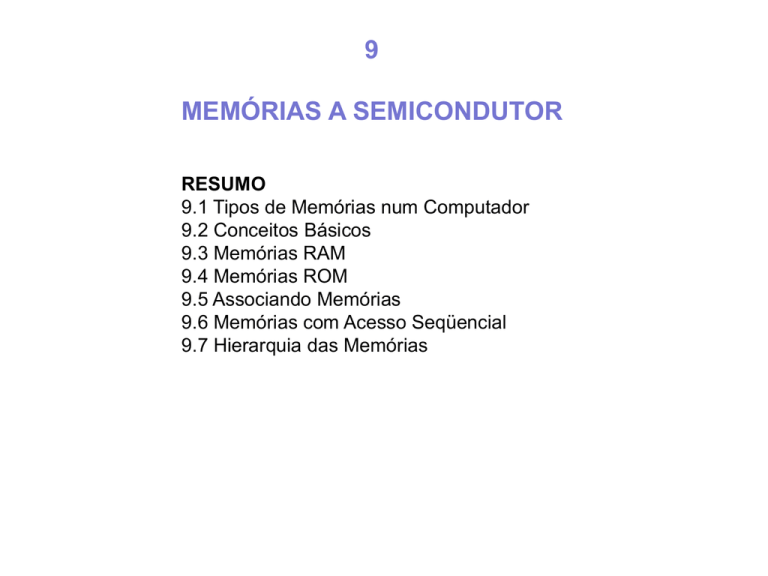

9

MEMÓRIAS A SEMICONDUTOR

RESUMO

9.1 Tipos de Memórias num Computador

9.2 Conceitos Básicos

9.3 Memórias RAM

9.4 Memórias ROM

9.5 Associando Memórias

9.6 Memórias com Acesso Seqüencial

9.7 Hierarquia das Memórias

Objetivos

No final do capítulo, o leitor será capaz de:

•Conhecer os diversos tipos de Memória a Semicondutor

•Trabalhar com RAM, SRAM, DRAM, ROM, EPROM, EEPROM, FLASH

•Manipular convenientemente circuitos comerciais

•Desenvolver associação de “Chips” de Memórias

•Trabalhar com Memórias Seqüenciais

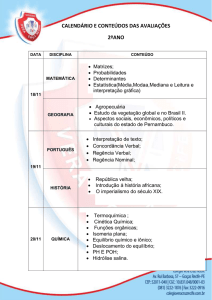

Monitor

Outros

Computadores

CPU

Registradores

Contadores

Controle

De Video

Teclado

Mouse

Placa

de Rede

Barramento

ALU

RAM

Controle

Controladora

de Discos

Portas Serial,

Paralela, USB

ROM

Floppy

Disc

Memória

Principal

CD

Disco

Rígido

Memória

Secundária

Impressora

Modem

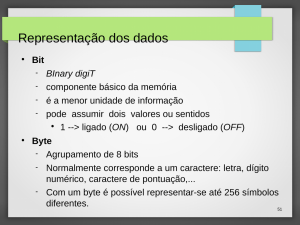

9.2 CONCEITOS BÁSICOS

Memória

Célula de Memória (“Memory Cell”)

“Chip”

Memória Bipolar e MOS

MOS (“Metal-Oxide Semiconductor”)

NMOS: uma técnica MOS onde o mecanismo de condução

básico é governado por elétrons.

PMOS: uma técnica MOS onde o mecanismo de condução

básico é governado por buracos.

CMOS: uma técnica MOS onde o mecanismo de condução

envolve buracos e elétrons.

Potência consumida

Potência utilizada ou dissipada pelo “Chip” de memória.

Custo de armazenamento por “bit”

Corresponde ao preço do circuito integrado dividido pelo número

total de “bits” que pode armazenar.

Escrever (“Write”)

Termo usado para a operação de armazenamento de uma

informação binária.

Ler (“Read”)

Termo usado para a operação de resgate, ou busca, de uma

informação armazenada.

Entradas de endereço (“Address”)

Entradas de dados (“Datas”)

Saídas (“Outputs”)

Dado (“Data”)

Densidade

Palavra (“Word”)

“Byte”

K

Caracter usado para se referir a uma quantidade de “bits” igual

a 210 “bits”, ou seja, 1024 “bits”. Por exemplo, 32 K = 32 x 1024

“bits” = 32.768 “bits”.

“Kilobyte”

Termo usado para um conjunto de 1024 (210) “bytes”. Portanto, uma

memória com 1 Kbyte pode armazenar 1024 x 8 “bits”, ou seja, 8192

“bits”.

“Megabyte”

Termo usado para um conjunto de (220) “bytes”, ou seja, 1 milhão de

“bytes”. Portanto, uma memória com 1 Mbyte pode armazenar 1024 x

1024 x “bytes” (ou seja, 1.048.576 “bytes”), totalizando 8 388 608 “bits”.

“Gigabyte”

Termo usado para um conjunto de (230) “bytes”, ou seja, 1 bilhão de

“bytes”. Portanto, uma memória com 1 Gigabyte pode armazenar 1024

x 1024 x 1024 x “bytes” (ou seja, 1 073 741 824 “bytes”).

“Terabyte”

Termo usado para um conjunto de (240) “bytes”, ou seja, 1 trilhão de

“bytes”.

Portanto, uma memória com 1 Terabyte pode armazenar 1024 x 1024 x

1024 x 1024 x “bytes” (ou seja, 1 099 511 627 776 “bytes”).

Memória volátil

É a memória que perde o seu conteúdo na ausência de alimentação.

Memória não-volátil ou fixa

É a memória que não perde o seu conteúdo na ausência de

alimentação.

“Tempo de acesso”

Define-se como tempo de acesso ao intervalo de tempo necessário

para transferir uma informação de uma locação da memória para as

suas saídas. Este parâmetro é válido para qualquer tipo de memória.

“Standby”

Disponível em algumas memórias, que garante baixo consumo.

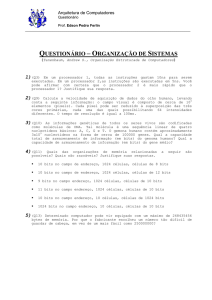

Exemplo 9.1

Um “chip” de memória possui capacidade igual a 16 K x 4. Quantos “bits”

podem ser armazenados no “Chip”?

Solução: Um “chip” com capacidade igual a 16 K x 4 significa que possui

16 x 1024 (=16 K) posições de memória, cada uma com 4 “bits”. Portanto,

pode armazenar 16 x 1024 x 4 “bits”, ou seja, 65536 “bits”.

Exemplo 9.2

Um “chip” de memória possui capacidade igual a 32 K x 8. Quantos são

os terminais para entradas de endereço, para entradas de dados e para

saídas de dados?

Um “Chip” com capacidade igual a 32 K x 8 significa que possui 32 x

1024 (= 32 K) posições de memória, cada uma com 8 “bits”. Portanto,

possui 32 x 1024 (= 32768) posições de memória.

O número (n) de entradas de endereço é definido pela equação: 2n =

número de posições. Neste caso, teríamos: 2n igual a 32768, ou seja, n

deve ser igual a 15.

Como cada posição possui oito “bits”, serão necessários oito terminais

para entradas de dados e oito para saídas de dado, salvo se o “chip”

usar os mesmos terminais para entrada e saída de dados conforme

veremos mais adiante.

9.3 MEMÓRIAS RAM

Neste tipo de memória é possível realizar operações de escrita e de leitura.

Por esta razão, também são conhecidas com a designação de memória de

leitura/escrita (Memory Read/Write - MRW).

RAM - DOIS TIPOS – ESTÁTICA e DINÂMICA

9.3.1 Memória RAM Estática - SRAM

É uma memória do tipo leitura/escrita - tecnologia Bipolar ou MOS onde cada “bit” é armazenado numa estrutura tipo “latch”. Cada

“latch” usa de quatro a seis transistores.

Os dispositivos Bipolares tendem a ser mais rápidos do que os

MOS, que por sua vez, consomem menos potência e permitem

maior capacidade de armazenamento por área de silício.

Célula de Memória

Seleção

X

R

Entrada

S

Q

Saída S

D

Leitura/Escrita

R/W

Seleção

0

X

0

0

Entrada

R

S

Q

0

Saída S

D

Leitura/Escrita

R/W

Quando a entrada de seleção X assume 0, a Célula é desabilitada, a

saída S assume 0, R e S assume 0 garantindo uma manutenção

(“latch”) de Q.

Quando a entrada de seleção X assume 1, a Célula é habilitada,

podendo operar no modo escrita (R/W´ igual a 0) ou no modo

leitura (R/W´ igual a 1).

Seleção

1

X

R

Entrada

S

Q

0

Saída S

D

0

Leitura/Escrita

R/W

Se ainda R/W’ assumir 0, a entrada D é armazenada no “latch”

(saída Q), caracterizando uma operação de escrita. Se, a seguir,

R/W’ assume 1, o valor armazenado no “latch” fica preservado

(travado) e ele fica bloqueado para armazenamento.

Quando a entrada de seleção X assume 1, a Célula é habilitada,

podendo operar no modo escrita (R/W´ igual a 0) ou no modo

leitura (R/W´ igual a 1).

Seleção

1

X

R

Entrada

S

Q

0

Saída S

D

0

Leitura/Escrita

R/W

Com X em 1 e R/W’ em 1, o conteúdo do “latch” passa pela porta

AND de saída e é apresentado em S, caracterizando uma operação

de leitura.

“Buffer” na saída

Seleção

X

CS

R

Entrada

S

Saída S

Q

D

R/W

Leitura/Escrita

Com “buffer” na saída é possível conectar ou desconectar a saída S das

entradas de outros dispositivos.

Quando CS assume nível 1, o circuito se comporta como o da figura

anterior. Contudo, ao assumir nível 0, o “buffer” entra em terceiro estado

(alta impedância), isolando (desconectando) a célula de memória de

outros circuitos. Neste caso, ainda é possível a operação de escrita.

Memória com 4 x 3 células

I2

I1

I0

S0

1

D

E

C

O

D

I

F

I

C

A

D

O

R

A0

A1

Habilita

a Memória

CM

2

CM

3

CM

S1

4

CM

5

CM

6

CM

S2

7

CM

8

CM

9

CM

S3

Enable

10

CM

11

CM

12

CM

Leitura/Escrita

O2

O1

O0

CS

Memória com 1024 x 4 células

Endereços

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

__

CS

__

WE

Entradas/

saídas

1024x4

I/O1

I/O2

I/O3

I/04

"Buffers"

de Entrada

A4

A5

A6

A7

A8

A9

Decodificador/

"latch" de linha

Matriz de

Células

"Buffers"

de Saída

I/O1

I/O2

Controle dos

Dados

de Entrada

I/O3

I/04

Circuito de

Entrada/Saída

Decodificador/

"latch" de coluna

A0

__

CS

__

WE

Y

X

A1

A2

A3

SRAM Síncrona

Uma geração conhecida como memória SRAM Síncrona que possui

um sincronismo com o processador garantindo tempo de acesso

menores as SRAM Assíncronas.

Temporização e Largura de Pulso de Escrita - SRAM

Os parâmetros relacionados aos tempos de chaveamento numa

memória devido aos atrasos nas portas internas, aos sinais de

endereços, de controle e das restrições impostas pelos tempos de

tempos de preparação (estabilização) e manutenção (retenção).

SRAM SMJ5C1008 da Texas - CMOS

•128 K x 8, ou seja, com 1048576 bits ( 128 * 1024 * 8 )

•(CE1)’ e CE2 do tipo “Enable” - habilitar o Chip ou colocar em “standby”

•Quando a entrada (OE)’ assume nível 0, as saídas são colocadas em terceiro estado

•Numa operação de escrita, (WE)’ e (CE1)’ assumem nível 0 enquanto CE2 assume nível 1. Numa

operação de leitura, (WE)’ e CE2 assumem nível 1 enquanto (CE1)’ e (OE)’ assumem nível 1.

128 K x 8

NC

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ1

DQ2

DQ3

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

VCC

A15

CE2

(WE)'

A13

A8

A9

A11

(OE)'

A10

(CE1)'

DQ8

DQ7

DQ6

DQ5

DQ4

A6

A5

A4

A3

A15

A14

A13

A8

A7

DQ8

Decodificador

de linha

Matriz com

1048576 "bits"

.

.

.

Controle

I/O

DQ1

___

CE1

CE2

Decodificador

de coluna

__

OE

__

WE

A16 A0 A2 A1 A10 A9 A12 A11

Power

Down

Sinais numa Operação de Leitura

Tempo de ciclo de leitura: tc

Intervalo de tempo em que as entradas

de endereço permanecem válidas

numa operação de leitura.

tc

A0 - A16

Endereço Válido

t

t hd ac

DQ1 – DQ8 Dados anteriores válidos

Dados válidos

Dados inválidos

Tempo “hold” para dados: thd

Intervalo de tempo em que os dados

permanecem válidos na saída após

uma mudança de endereço.

Chip sempre selecionado

Tempo de acesso: tac

Intervalo de tempo decorrido desde o

instante em que as entradas de

endereço se estabilizam até o instante

em que a informação fica disponível

nas saídas da memória, ou seja,

tempo necessário para copiar o

conteúdo de uma posição na memória

para as suas saídas.

tc

A0 - A16

Endereço Válido

(CE1)’

t ac

CE2

(OE)’

t ce

DQ1 – DQ8

Dados válidos

Alta Impedância

Dados inválidos

Chip selecionado pelos “enable”

Tempo de habilitação do “chip”: tce

Tempo de resposta do circuito após a

seleção do circuito.

Sinais numa Operação de Escrita

Largura do pulso de escrita: tw

tc

A0 - A16

Endereço Válido

t he

t ss

(CE1)’

t se

Tempo “set-up” para endereços: tse

Tempo transcorrido desde a

estabilização das linhas de endereço

até o início do pulso de escrita.

tw

(WE)’

t sd

Dados de

Entrada

Tempo “set-up” para dados: tsd

Tempo transcorrido desde a

estabilização das linhas de dados até

o fim do pulso de escrita.

t hd

Dado Válido

Tempo “set-up” para seleção: tss

Tempo decorrido desde a seleção do

“chip” até o início de armazenamento.

Saídas Q

Alta Impedância

Alta Impedância

Tempo “hold” para seleção: ths

Tempo mínimo de permanência do sinal de

seleção após pulso de escrita.

Tempo “hold” para dados: thd

Tempo mínimo de permanência das

linhas de dados após pulso de escrita.

Tempo “hold” para endereços: the

Tempo mínimo de permanência das

linhas de endereço após pulso de

escrita.

Mapeando o conteúdo da memória

__

CS

__

WE

Endereços

A0

A1

A2

RAM

8x8

Entradas/

saídas

I/O1

I/O2

I/O3

I/04

I/O5

I/O6

I/O7

I/08

0

0

0

10101010

0

0

1

11110000

0

1

0

10000001

0

1

1

10100010

1

0

0

11000011

1

0

1

10000011

1

1

0

11011111

1

1

1

11111111

Endereço

em binário

8 posições

(andares)

Entradas de

endereços

(hexadecimal)

0

F

4321 4321

"Displays"

CW1

0

0

4321

4321

RAM1K

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

4321

CS

WE

IO7

IO6

IO5

IO4

IO3

IO2

IO1

IO0

Procedimento de escrita:

1. CW1 = 0;

2. Defina endereço;

3. Coloque os dados;

4. Acione a chave CW2.

5V

74LS126

74LS126

4C

4A

3C

3A

2C

2A

1C

1A

R1 1k

Leitura/

Escrita

CW2

4C

4A

3C

3A

2C

2A

1C

1A

4Y

3Y

2Y

C1 1Y

3

4

4321

4Y

3Y

2Y

C2 1Y

Procedimento de leitura:

1. CW1 = 0;

2. Defina o endereço;

3. Observe os dados

armazenados nas

saídas.

CW2 = 1 Leitura

CW2 = 0 Escrita

4321

CW1=1 garante alta

impedância

CW1=0 libera o "chip"

Entradas

de dados

9.3.2 Memória Dinâmica DRAM

RAS

CAS

Endereços

Entrada

A0

A1

A2

A3

A4

A5

A6

DRAM

4116

D

16K x 1

Q

Saída

R/W

•Memória volátil tipo leitura/escrita onde cada “bit” da informação é

armazenado num micro capacitor CMOS.

•Um único transistor é usado para carregar o capacitor (nível 1) ou

descarregá-lo (nível 0). Comparadas com as estáticas, elas

consomem menos e favorecem maior densidade (larga integração).

•Precisa passar periodicamente por uma operação de refrescamento

(”refresh operation“),

Os “chips” DRAM possuim sinais de controle típicos denominados RAS

e CAS, usados na definição do endereço em questão.

RAS (“Row Address Strobe”): Um sinal usado para controlar a entrada

do endereçamento de linhas. Pode ser ativo em alto (RAS) ou em baixo

(RAS)’.

CAS (“Column Address Strobe”): Um sinal usado em DRAM’s para

controlar a entrada do endereçamento de coluna. Pode ser ativo em

alto (CAS) ou em baixo (CAS)’.

MEMR

(RAS)’

D

P

Q

(CAS)’

D

P

Q

MEMR

A7

A8

A9

A10

A11

A12

A13

D

S

P

Q

Q

Q

Clock

PROCESSADOR

A0

A1

A2

A3

A4

A5

A6

Q

RAS

CAS

DRAM

4116

MUX

A0

A1

A2

A3

A4

A5

A6

Entrada

D

Q

H

MEMR

L

H

(RAS)'

L

H

Saída

S

S

L

H

R/W

CONTROLE

(CAS)'

L

H

Clock

L

0.00

10.00n

20.00n

Tempo (s)

30.00n

9.3.3 Memória Dinâmica Síncrona - SDRAM

Numa Memória de Acesso Randômino Dinâmica Síncrona (SDRAM “Syncronous Dynamic Random Acess Memory”) que, ao contrário das

DRAM’s típicas assíncronas, os sinais de endereço, dados e controles

são sincronizados com um sinal “clock”.

Isto permite uma taxa de transferência maior do que as DRAM. Por

exemplo, troca dados com o microprocessador em sincronia com o sinal

“clock”, operando am alta velocidade sem imposição de estados de

espera.

9.3.5 Decidindo entre SRAM e DRAM

Apesar da necessidade de refrescamento, a grande vantagem das

memórias dinâmicas sobre as estáticas é a de permitir maior densidade número de componentes por área de silício - na fabricação dos “chips” em

função do armazenamento capacitivo. Também operam com baixo consumo,

da ordem de 3 a 5 vezes menor do que as estáticas.

Por outro lado, as estáticas em função do armazenamento transistorizado

são mais rápidas do que as dinâmicas, contudo, são mais caras devido à

sua menor densidade.

Quando o que se deseja é maior velocidade de acesso e menor

complexidade de circuitos, devemos usar as SRAM. Quando o crítico é a

densidade e o consumo de energia, devemos usar DRAM.

9.4 MEMÓRIAS ROM

Tipos

Existem cinco tipos básicos de ROM: 1) ROM padrão ou de

máscara (fabricada como uma matriz de diodos ou transistores); 2)

PROM; 3) EPROM; 4) EEPROM; 5) FLASH.

9.4.1 ROM com Matriz de Diodos

A

Linha X

Linha Y

B

C

Linha Z

D

Linha W

Saídas

S0

S1

S2

S3

S4

Colunas

S5

S6

S7

A1

A0

D

E

C

O

D

I

F

I

C

A

D

O

R

A

Linha X

B

Linha Y

C

Linha Z

D

Linha W

Saídas

S0

Endereço

S1

S2

S3

Linhas

S4

S5

S6

S7

Saídas

A1

A0

X

Y

Z

W

S0

S1

S2

S3

S4

S5

S6

S7

0

0

1

0

0

0

1

0

1

0

1

0

0

1

0

1

0

1

0

0

1

0

1

0

0

0

1

1

1

0

0

0

1

0

1

0

0

0

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

9.4.2 ROM programável pelo usuário - PROM

O circuito TBP28S166 é um “chip” de memória do tipo PROM

Bipolar com 2 Kbytes. O circuito TMS27PC256 é um “chip” de

memória do tipo PROM CMOS com 32 Kbytes, com controle para

“standby” e com tempo de acesso de 150 ns.

Permite uma única gravação. Possui um fusível em série com o

Diodo.

9.4.3 ROM Programável e Apagável pelo Usuário

“EPROM” - “Erasable PROM”

Memória fixa que pode ser programada e reprogramada pelo

usuário.

É implementada usando o princípio de armazenamento do tipo

“Floating-gate Avalanche Injection MOS” (“FMOS”), onde uma

porta de silício fica sem conexão elétrica (porta flutuante) num

ambiente de alta impedância. Cada intersecção linha/coluna de

uma EPROM possui dois transistores separados entre si por uma

fina camada de óxido.

Os dois transistores são chamados, respectivamente, porta

flutuante (“floating gate”) e porta de controle (“control gate”).

Originalmente, todos os transistores estão cortados, garantindo 1

em todas as posições.

Apagável com equipamento especial a base de luz ultravioleta.

EEPROM – “Electrically Erasable ROM” (E2PROM)

São similares às memórias EPROM, contudo, o conteúdo pode ser

apagado eletronicamente.

1) Os “chips” não precisam ser retirados dos soquetes para o ambiente

de gravação, como normalmente é feito nas EPROM’s;

2) O conteúdo inteiro do “chip” não precisa ser apagado para promover

uma mudança em uma determinada posição da memória;

3) A mudança de conteúdo não requer um circuito ou equipamento

adicional e específico.

4) Tanto a gravação quanto o apagamento é feito por sinais elétricos.

FLASH

São memórias graváveis e apagáveis eletricamente, à exemplo das

EEPROMs. Combina todas melhores características dos tipos anteriores.

De grande densidade, não volátil, leitura/escrita, rápidas e baixo custo .

São usadas no lugar de discos rígidos de baixa capacidade.

Nas memórias EEPROM’s é possível mudar 1 “byte” por vez, tornando-as

versáteis, contudo, mais lentas para serem usadas em sistemas onde

ocorrem mudanças rápidas no armazenamento de dados, limitação

corrigida com o desenvolvimento das memórias FLASH, onde o tempo de

apagamento pode ser da ordem de micro segundos.

Internamente as memórias FLASH são do tipo EEPROM com um circuito de

fiação que permite apagar o conteúdo inteiro do “chip” ou de uma área prédeterminada chamada de bloco. São mais rápidas dos que as EEPROM’s

porque escrevem, de uma vez, dados em pacotes, normalmente com

tamanho igual a 512 “bytes”, ao invés de 1 “byte” por vez.

9.5 ASSOCIANDO MÉMORIAS RAM

CASO 1:

Construindo um circuito equivalente com 1024x8, usando “ Chips” com 1024x4

1024X4

E

N

D

E

R

E

Ç

O

S

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

1024X8

I/O1

I/O2

I/O3

I/O4

Entradas/

Saídas

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

CS

CS

R/W

R/W

?

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

O que

queremos

obter

SOLUÇÃO: Colocar um “edifício” ao lado do outro.

Ou seja, vamos usar dois circuitos com

1024x4.

Associação

Horizontal

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

I/O1

I/O2

I/O3

I/O4

CS

R/W

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

CS

R/W

1024X8

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

?

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

CS

R/W

I/O1

I/O2

I/O3

I/O4

O que

queremos

obter

O que fazer? Interligar todas os terminais

similares, de mesma natureza, menos as

saídas.

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

I/O1

I/O2

I/O3

I/O4

CS

R/W

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

CS

R/W

CIRCUITO FINAL

1024X8

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

CS

R/W

I/O5

I/O6

I/O7

I/O8

?

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

SOLUÇÃO APRESENTADA NO LIVRO

A9

.

.

.

.

.

A0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

CS

WE

WE

RAM 1KX4

IO7

.

.

.

I00

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

CS

WE

WE

RAM 1KX4

(CS)'

(WE)'

9.5 ASSOCIANDO MÉMORIAS RAM

CASO 2:

Construindo um circuito equivalente com 2048x4, usando “ Chips” com 1024x4

1024X4

E

N

D

E

R

E

Ç

O

S

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

2048X4

I/O1

I/O2

I/O3

I/O4

Entradas/

Saídas

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

CS

CS

R/W

R/W

?

I/O1

I/O2

I/O3

I/O4

O que

queremos

obter

SOLUÇÃO: Colocar um “edifício” em cima do outro.

Ou seja, também vamos usar dois

circuitos com 1024x4.

Associação

Vertical

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

I/O1

I/O2

I/O3

I/O4

CS

R/W

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

CS

R/W

2048x4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

?

I/O1

I/O2

I/O3

I/O4

CS

R/W

I/O1

I/O2

I/O3

I/O4

O que

queremos

obter

O que fazer? Interligar todas os terminais

similares, de mesma natureza, menos as

entradas (CS)´ que serão usadas para gerar

a nova entrada A10.

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

I/O1

I/O2

I/O3

I/O4

2048x4

A10

CS

R/W

1024X4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

CS

R/W

CIRCUITO FINAL

I/O1

I/O2

I/O3

I/O4

I/O1

I/O2

I/O3

I/O4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

?

R/W

Note que falta o

(CS)´

I/O1

I/O2

I/O3

I/O4

SOLUÇÕES APRESENTADAS NO LIVRO

A10

.

.

.

.

.

.

A0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

WE

RAM1KX4

2048 X 4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

WE

RAM1KX4

(WE)'

SOLUÇÃO COM ENTRADA (CS)´

(CS)'

A10

.

.

.

.

.

.

A0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

WE

RAM1KX4

2048 X 4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

WE

RAM1KX4

(WE)'

5V

(CS)'

74LS138

A2

A1

A0

E3

E2

E1

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

A10

.

.

.

.

.

.

A0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

WE

RAM1KX4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

IO3

IO2

IO1

IO0

CS

WE

RAM1KX4

SOLUÇÃO COM ENTRADA (CS)´

USANDO DECODIFICADOR

(WE)'

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

9.6 MEMÓRIAS COM ACESSO SEQüENCIAL

(“Sequencial Access Memory” - SAM)

CK

Porta 1

DS

REG

Clock

CON

Ds

Entrada

Série

E

Ei

CK

2-74126

Y1

A1

Y2

A2

Y3

A3

Y4

A4

Y5

A5

Y6

A6

Y7

A7

Y8 C A8

B0

B1

B2

B3

B4

B5

B6

B7

A0

A1

A2

A3

A4

A5

A6

A7

Ca

S0

S1

S2

S3

5V

CK

RDM

L

CLR

Calu

D0

D1

D2

D3

D4

D5

D6

D7

Lrdm

Palavra de Controle

3

F

F

F

CK

L

E

Lc

Erdm

2x74181

SAÍDA 1

4321

4321

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

REG C

CLR

E

CK

Barramento

de Endereços

D7

D6

D5

D4

D3

D2

D1

D0

0

Y8 C A8

Y7

A7

Y6

A6

Y5

A5

Y4

A4

Y3

A3

Y2

A2

Y1

A1

2-74126

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

SAÍDA 2

8

4321 4321 4321 4321 4321

E

Ld

CK

Lrdm WE

1 1

3

S3 S2 S1 S0

1 1 1 1

F

M Cin Ls2 Ls1

1 1

1

1

F

La Lb Li Ei

1 1

1 1

F

Erdm Calu Ca Cb

1

0

0 0

8

4321

REG D

E =1

C =0

Z

Z

L =0

Carga

Síncrona

8 8

Palavra de Controle = Ck

Default =

4321

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

CLR

D0

D1

D2

D3

D4

D5

D6

D7

L

0

2x74173

0

4321 4321 4321

WE

IO7

IO6

IO5

IO4

IO3

IO2

IO1

IO0

ALU

2-74126

Y1

A1

Y2

A2

Y3

A3

Y4

A4

Y5

A5

Y6

A6

Y7

A7

Y8 C A8

RAMCS

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

D3

D4

D5

D6

D7

Cb

REG I

2x74173

ENTRADA DE

ENDEREÇOS

REG A

2-74126

Y1

A1

Y2

A2

Y3

A3

Y4

A4

Y5

A5

Y6

A6

Y7

A7

Y8 C A8

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

CLR

D0

D1

D2

D3

D4

D5

D6

D7

Li

A=B M Cin

4321

E

La L

F0

F1

F2

F3

F4

F5

F6

F7

4321

TECLADO

Lb L

Ea

CLR

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2

L

2

REG B

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

CK

Eb E

D0

D1

D2

D3

D4

D5

D6

D7

ENTRADA

DE DADOS

EM BCD

CK

BARRAMENTO

DE DADOS

BARRAMENTO

DE CONTROLE

CLR