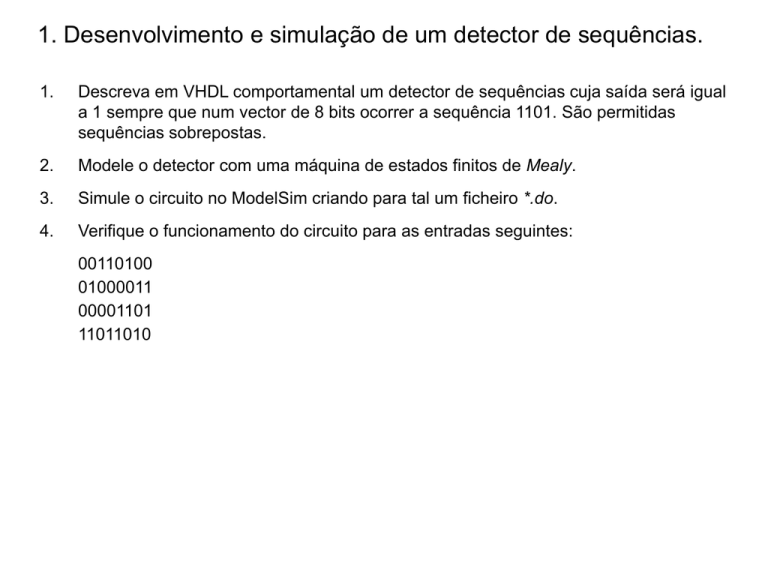

1. Desenvolvimento e simulação de um detector de sequências.

1.

Descreva em VHDL comportamental um detector de sequências cuja saída será igual

a 1 sempre que num vector de 8 bits ocorrer a sequência 1101. São permitidas

sequências sobrepostas.

2.

Modele o detector com uma máquina de estados finitos de Mealy.

3.

Simule o circuito no ModelSim criando para tal um ficheiro *.do.

4.

Verifique o funcionamento do circuito para as entradas seguintes:

00110100

01000011

00001101

11011010

2. Desenvolvimento e simulação de circuitos genéricos.

1. Crie uma função que conte o número de 1s num vector de tamanho

arbitrário. Desenvolva em VHDL um circuito que recebe dois vectores,

de 16 e 32 bits, usa a função para contar 1s e disponibiliza os

resultados em BCD. Simule o circuito.

2. Crie um procedimento que calcula a soma (bit a bit) de dois números de

comprimento arbitrário e detecta a ocorrência de overflow. Use o

procedimento para somar dois quaisquer vectores e simule.

3. Descreva em VHDL estrutural um comparador iterativo que deve ser

construído a partir de comparadores de um bit. Use o comando

generate. Um comparador de um bit tem 5 entradas (os bits x e y a

comparar e os sinais > - GT, < - LT, = - EQ, provenientes de outros bits)

e gera 3 saídas (> - GT, < - LT, = - EQ, a ligar com os bits seguintes).

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity ind_comp is

port ( GT, LT ,EQ : in std_logic;

x, y : in std_logic;

GT_out, LT_out, EQ_out : out std_logic);

end ind_comp;